Asynchrone Reset-Synchronisierung und -Verteilung – Herausforderungen und Lösungen

Ein Mangel an Koordination zwischen asynchronen Resets und synchronen Logiktakten führt zu zeitweiligen Ausfällen beim Einschalten. In dieser Artikelserie diskutieren wir die Anforderungen und Herausforderungen des asynchronen Resets und erkunden fortschrittliche Lösungen für ASIC- und FPGA-Designs.

Asynchrone Rücksetzungen werden traditionell in VLSI-Designs verwendet, um synchrone Schaltungen nach dem Einschalten in einen bekannten Zustand zu bringen. Der asynchrone Reset-Freigabevorgang muss mit dem synchronen Logiktaktsignal koordiniert werden, um Synchronisationsfehler aufgrund einer möglichen Konkurrenz zwischen dem Reset und dem Takt zu beseitigen. Ein Mangel an einer solchen Koordination führt zu zeitweiligen Ausfällen beim Einschalten. Das Problem verschlimmert sich, wenn große Domänendesigns mit mehreren Takten in Betracht gezogen werden. Zusätzlich zu den Synchronisationsproblemen ist die Verteilung eines asynchronen Resets auf Millionen von Flip-Flops eine Herausforderung, die ähnliche Techniken wie CTS (Clock Tree Synthesis) erfordert und ähnliche Flächen- und Routing-Ressourcen erfordert.

Die Anforderungen und Herausforderungen des asynchronen Zurücksetzens werden überprüft, wobei der Schwerpunkt auf Synchronisations- und Verteilungsproblemen liegt. Die Nachteile klassischer Lösungen zur Reset-Synchronisation (Reset-Tree-Source-Synchronisation) und Verteilung (Reset-Tree-Synthese) werden diskutiert. Es werden fortschrittliche Lösungen für eine schnellere und einfachere Timing-Konvergenz und eine zuverlässigere Reset-Synchronisation und -Verteilung vorgestellt. Unterschiedliche Ansätze für ASIC- und FPGA-Designs werden detailliert beschrieben.

Teil 1 (dieser Artikel) beschreibt die Probleme im Zusammenhang mit asynchronen Zurücksetzungen und skizziert Ansätze zur Behebung dieser Probleme. In Teil 2 werden zusätzliche Lösungen für den korrekten asynchronen Reset in ASIC und FPGA diskutiert. Einige nützliche Sonderfälle werden in Teil 3 besprochen.

1. Herausforderungen beim asynchronen Zurücksetzen

Eine Rücksetzfunktion ist normalerweise in digitalen VLSI-Designs enthalten, um die Logik in einen bekannten Zustand zu bringen. Reset ist meistens für die Steuerlogik erforderlich und kann aus der Datenpfadlogik eliminiert werden, wodurch der Logikbereich reduziert wird. Das Zurücksetzen kann relativ zum Taktsignal entweder synchron oder asynchron erfolgen.

Synchrones Zurücksetzen erfordert einen aktiven Takt, verursacht eine gewisse taktzyklusbezogene Latenz und kann sich auf das Timing der Datenpfade auswirken. Andererseits sind synchrone Resets deterministisch und führen nicht zu Metastabilität.

Asynchrones Zurücksetzen erfordert keinen aktiven Takt, um Flip-Flops in einen bekannten Zustand zu bringen, hat eine geringere Latenz als ein synchrones Zurücksetzen und kann spezielle Flip-Flop-Eingangspins ausnutzen, die das Datenpfad-Timing nicht beeinflussen. Asynchrone Resets haben jedoch eine Reihe von Nachteilen:

Sie können Metastabilität in Flip-Flops verursachen, was zu einem nicht-deterministischen Verhalten führt.

Asynchrone Resets müssen direkt zugänglich gemacht werden, um DFT zu aktivieren.

Die asynchronen Resets können in extrem harten Anwendungen zu Zuverlässigkeitsproblemen führen, da sie anfällig für Single Event Transient (SET)-Phänomene [1] sind.

Abgesehen von der Diskussion, welche Art von Reset besser ist [2], konzentrieren wir uns in diesem Artikel auf Probleme und Lösungen im Zusammenhang mit asynchronen Resets. Einige der in diesem Dokument vorgestellten Techniken sind sowohl auf asynchrone als auch auf synchrone Rücksetzungen anwendbar.

Asynchrone Rücksetzungen werden in digitalen Designs häufig verwendet. Die typischen Treiber von asynchronen Resets sind externe Ports, abhängig vom Stromversorgungsstatus (RC-Kreise, Watchdog-Geräte), manuelle Reset-Taster und externe Master, wie z. B. Mikroprozessoren.

In vielen Fällen können asynchrone Resets durch synchrone ersetzt werden, aber es gibt Situationen, in denen die asynchrone Reset-Funktionalität obligatorisch ist. Ein Beispiel ist ein synchrones Design, das beim Einschalten keinen aktiven Takt erhält (der Takt ist entweder instabil oder zur Leistungsreduzierung gated), erfordert jedoch einen bestimmten bekannten Zustand für seine externen Schnittstellen. Ein weiteres Beispiel ist ein Low-Power-Design, das erforderlich ist, um den Strom während des Einschaltvorgangs zu minimieren, da es keine aktiven Taktgeber hat.

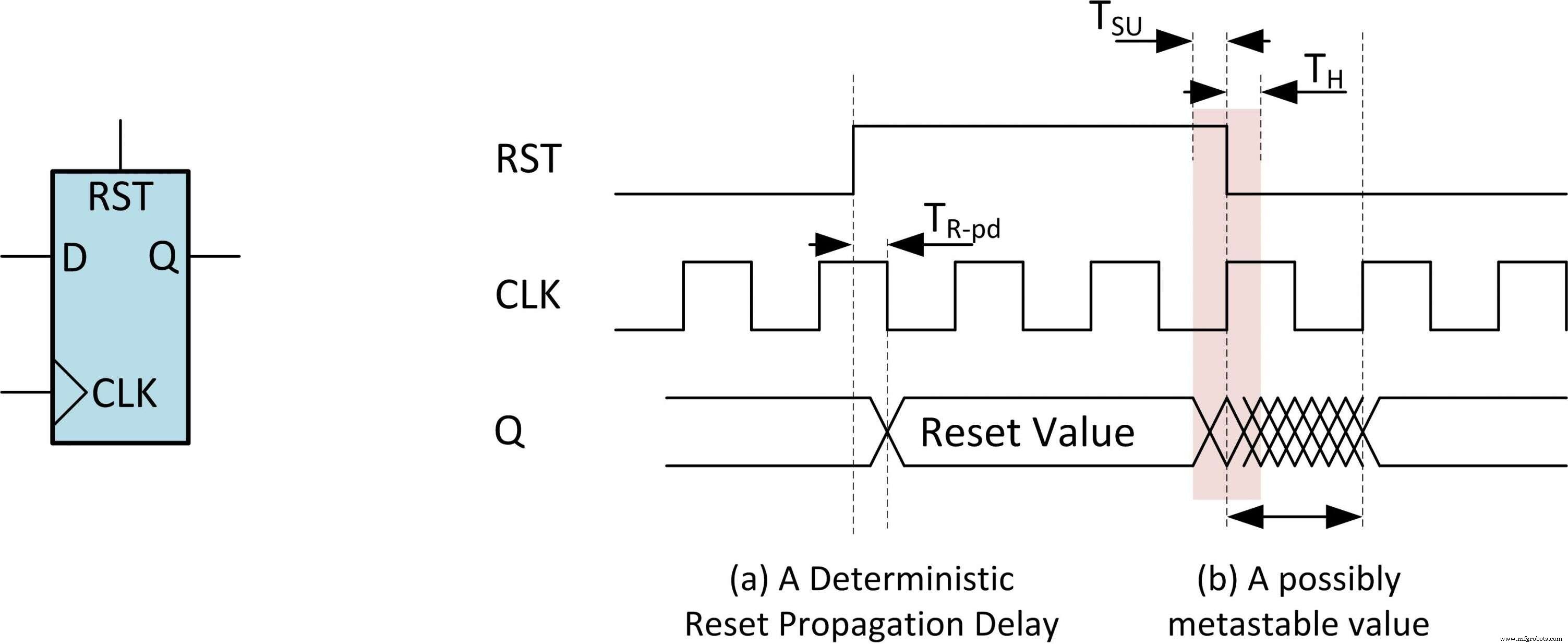

Die Anwendung des asynchronen Resets ist nicht einfach. Obwohl das relative Timing zwischen Takt und Rücksetzen während der Rücksetzungsbestätigung ignoriert werden kann, muss die Rücksetzungsfreigabe mit dem Takt synchronisiert werden. Das Vermeiden der Reset-Freigabeflankensynchronisation kann zu Metastabilität führen. Unter Bezugnahme auf Fig. 1 ist ein aktiver asynchroner High-Reset gezeigt. Die Reset-Behauptung (a) beeinflusst den Flip-Flop-Ausgang Q innerhalb einer deterministisch begrenzten Zeit (Ausbreitungsverzögerung, TR-pd ) und unabhängig vom Taktsignal CLK. Während der Rücksetzfreigabe (b) müssen die Setup- und Haltezeitgebungsbedingungen für den RST-Port relativ zum Taktport CLK erfüllt sein. Eine Verletzung der Setup-and-Hold-Bedingungen für den RST-Port (auch bekannt als Reset Recovery and Removal Timing) kann dazu führen, dass das Flip-Flop metastabil wird, was zu Designfehlern aufgrund des Umschaltens in einen unbekannten Zustand führt. Beachten Sie, dass diese Situation der Verletzung der Setup-and-Hold-Bedingungen für den Flip-Flop-Datenport D ähnelt.

Klicken für größeres Bild

Abbildung 1:Aktive asynchrone High-Reset-Assertion und -Freigabe. (a) Eine asynchrone Reset-Behauptung (b) Eine asynchrone Reset-Freigabe mit Timing-Verletzung. (Quelle:vSync Circuits)

Eingebettet

- Over-the-Air-Updates:Fünf typische Herausforderungen und Lösungen

- Top-Leiterplatten-Trends und -Herausforderungen

- Anvo-Systems und Mouser unterzeichnen Vertriebsvereinbarung

- Swissbit:hardwarebasierte Sicherheitslösungen zum Schutz von Daten und Geräten

- Rutronik und AP Memory unterzeichnen globale Vertriebsvereinbarung

- IIoT-Trends und zu beobachtende Herausforderungen

- Industrielle IoT-Sicherheit:Herausforderungen und Lösungen

- Herausforderungen in der Automobilherstellung und IoT-Lösungen

- Top 5 logistische Herausforderungen und Lösungen für die Fertigungsindustrie

- Hochgeschwindigkeits-PCB-Design-Herausforderungen zur Signalintegrität und ihre Lösungen