Aufstieg in Richtung 7-nm

Dies ist der vierte einer vierteiligen Serie über die von IBM vorgestellten Vorträge auf der IEDM 2016.

Das jährliche International Electron Devices Meeting ist „das weltweit führende Forum für die Berichterstattung über technologische Durchbrüche in den Bereichen Halbleiter- und Elektronikgerätetechnologie, Design, Fertigung, Physik und Modellierung“. Also brachten IBM-Forscher ihr Scanning-Sonden-Thermometer, ihren Luftabstandshalter für einen 10-nm-Chip, ihren 7-nm-Chip mit, und um nicht von Silizium übertroffen zu werden, brachten sie auch ihre Kohlenstoff-Nanoröhrchen mit. Diese Papiere und Präsentationen von IBMern und vielen Partnern werden an der Konferenz in dieser Woche in San Francisco teilnehmen.

IEDM präsentiert vier IBM-Beiträge als einige der besten Beispiele der Konferenz für diese Neuinterpretation des Computing – die Erweiterung des Mooreschen Gesetzes und den Aufbau neuer Architekturen und die Verwendung neuer Materialien, um darüber hinauszugehen. Hier ist ein genauerer Blick auf diese Papiere und die Wissenschaftler hinter der Arbeit. Der letzte Teil der Serie beleuchtet das Paper „A 7nm FinFET Technology Featuring EUV Patterning and Dual-Strained High-Mobility Channels“ von Ruilong Xie, einem leitenden Mitglied des technischen Personals von GlobalFoundries und Mitgliedern des IBM-Teams im Albany Nanotech Center .

Im vergangenen Juli gaben IBM und seine Allianzpartner bekannt, dass sie die weltweit ersten 7-nm-Knotentestchips entwickelt haben. Der Durchbruch gelang durch die Anwendung der Extreme Ultraviolet (EUV) Lithography – einer Technik, bei der Licht zum Ätzen von Mustern in andere Materialien verwendet wird – und der Verwendung von Siliziumgermanium (SiGe) als Kanalmaterial im Transistor.

Von Silizium zu Silizium-Germanium

Das IEDM-Papier des Teams zeigt, dass „die auf SiGe basierende FinFET-Technologie eine Leistungssteigerung mit 10-nm-Technologie-Grundregeln (Industriestandards) gezeigt hat und elegante Lösungen für eine praktikable CMOS-Technologieoption bietet. Eine dieser eleganten Lösungen ist die Berücksichtigung von Low-Power- und High-Performance-Geräten auf demselben Chip – ohne dass die Leistung oder Variabilität eines Gerätetyps gegenüber dem anderen verloren geht“, wie in Materialinnovation bis 7nm explained erklärt .

Darüber hinaus verschiebt SiGe die Grenzen der Chipskalierung, indem es die Art und Weise ändert, wie Strom durch den Kanal eines Transistors fließt. Es stellt sich heraus, dass durch Hinzufügen größerer Germaniumatome zu einem Kristall aus kleineren Siliziumatomen der Kristall eine Gitterfehlanpassung entwickelt, die eine Spannung im Transistorkanal erzeugt. Diese Dehnung macht es möglich, bei niedrigeren Spannungen mehr Strom durch den Kanal zu bewegen. Durch die Verwendung von SiGe als Kanalmaterial in Kombination mit Innovationen bei parasitärem Widerstand und Kapazitätsreduzierung konnte das Team einen Fahrplan für einen 7-nm-Chip erstellen und gleichzeitig ein Gleichgewicht zwischen Leistung und Leistung beibehalten – eine Leistung bei konstanter Leistung, die, wie auf der IEDM . vorgestellt, , 40 Prozent besser als ein 10-nm-Chip!

Extrem kleine Wellenlängen des Lichts

Das verwendete Licht ist mit einer Wellenlänge von nur 13,5 nm viel kürzer als das heutige Standardlicht mit 193 nm Wellenlänge, wodurch es in der Lage ist, 20 Milliarden 7-nm-Transistoren auf einen Chip zu ätzen. Aber bevor das Team so viele Schalter auf einem Chip platzieren kann, muss es die Technologie hinter der Verwendung einer so kurzen Wellenlänge zu einem konsistenten, kontrollierten und wiederholbaren Prozess machen.

Um Chips mit Lithographie herzustellen, wird ein Wafer einem Lichtmuster ausgesetzt, ähnlich wie alle nicht-digitalen Fotonegative auf Kontaktpapier gedruckt werden – es wird über dem Wafer gehalten und das Licht wird durch eine Maske (das "Negativ") geleitet. . Die Größe der Linien und Drähte, die mit dieser Technik gedruckt werden können, spiegelt nicht nur die Größe der Linien auf der Maske wider, sondern auch die Wellenlänge des verwendeten Lichts. Heutzutage kann ein Wafer mit 193 nm Licht mehrmals belichtet werden, wenn das benötigte Muster kleiner ist als das, was 193 nm alleine liefern können.

Ähnlich wie beim japanischen Holzschnittdruck wird ein Muster nach dem anderen auf den Wafer geschichtet, um einen komplizierteren – und kleineren – Chip zu erhalten. Diese Mehrmustertechnik verursacht jedoch eine Verschlechterung; was für Chips in Massenprodukten wie Smartphones vielleicht kein so kritisches Problem darstellt, aber für Supercomputer und spezialisierte Systeme, die eine sehr hohe Zuverlässigkeit erfordern, ein erhebliches Hindernis darstellt. Und obwohl es technisch möglich ist, 7-nm-Chips auf diese Weise herzustellen, ist dies ein wichtiger Grund, warum IBM beschlossen hat, zu untersuchen, wie 7-nm-Chips mit EUV-Technologie hergestellt werden können.

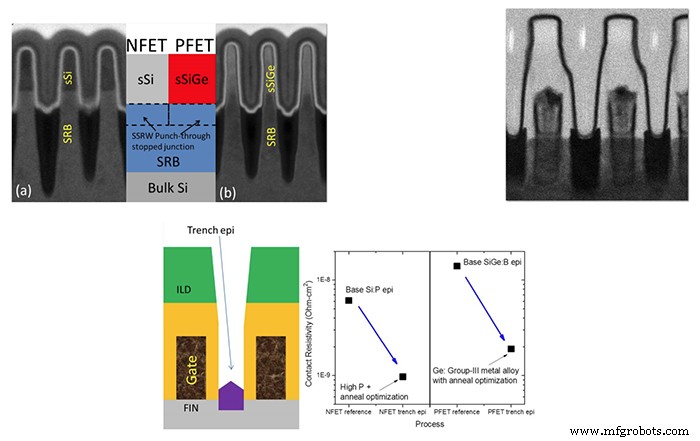

Oben links: Eine schematische Beschreibung von zweifach belasteten Kanalmaterialien auf dem SRB mit einem supersteilen retrograden Bohrloch (SSRW), zusammen mit TEM-Bildern von (a) der zugbelasteten Siliziumfinne und (b) der druckbelasteten SiGe-Finne auf einem gemeinsamen SRB. Oben rechts: Ein TEM-Bild eines 48-nm-kontaktierten Polysilizium-Pitch-Bauelements mit einem optimierten selbstjustierten Kontakt mit einer Kontaktöffnung von ~10 nm und Lmetal von ~15 nm. Unten Mitte: Abbildung und Grafik zeigen, dass der Graben-Epitaxieprozess gleichzeitig die Grundregeln und die Reduzierung des Kontaktwiderstands nach Implantations- und Glühoptimierungen erfüllt.

Bei Verwendung von 13,5-nm-EUV wird nur ein High-Fidelity-Muster benötigt, um ein einzelnes Muster auf einem 7-nm-Chip zu drucken. Die Herausforderung für EUV besteht darin, die Technologie zur Produktionsreife auszureifen. Ähnlich wie das 1964 gebaute IBM System 360 durch Verfeinerung, Skalierung und technischen Aufwand zu kleineren und schnelleren Maschinen von heute führte, wird EUV auf ähnliche Weise reifen müssen.

Bedenken Sie Folgendes:Um 13,5-nm-Licht zu erzeugen, gibt das EUV-Gerät einen Tropfen geschmolzenen Zinns in ein Vakuum ab (um eine Kugelform zu erhalten), der dann mit einem Kohlendioxidlaser getroffen wird, der es glättet und in einen bestimmten Winkel bewegt. Das immer noch fallende Zinn wird dann mit einem weiteren leistungsstärkeren Kohlendioxidlaser getroffen und verdampft, um 13,5-nm-Licht freizusetzen, das dann eingefangen und mit speziellen Spiegeln auf einen Wafer fokussiert wird.

Obwohl der Prozess zur Verwendung dieses 13,5-nm-Lichts kompliziert ist, beweist die Arbeit der Teams, dass die Herstellung eines 7-nm-Chips mit EUV möglich ist und qualitativ hochwertige Ergebnisse liefert. Das sollte bedeuten, dass spezialisierte hochzuverlässige Chips für zukünftige Hochleistungssysteme hergestellt werden können, um die Anforderungen von Supercomputern und Systemen der nächsten Generation zu erfüllen.

Lesen Sie Teil 1:Kartierung von Hotspots

Lesen Sie Teil zwei:Eine andere Art von Chip mit Kohlenstoff-Nanoröhrchen

Lesen Sie Teil drei:Luftspacer für 10-nm-Chips

Nanomaterialien

- C# verwenden

- Bewegungssensor mit Raspberry Pi

- Fortschrittliche Halbleitertechnologie, ein Nanometer nach dem anderen

- Miniatur-Lunge-Herz-Sensor auf einem Chip

- 3 Vorteile der Verwendung eines Bohrwerks

- Vorteile der Verwendung von Legierungen

- Was sind Späneförderer?

- Eine Einführung in Späneförderer

- Was ist ein Magnetspäneförderer?

- Eine Mühle als Drehbank verwenden