PCB-Design und Forschung zu Hochgeschwindigkeits-Passwortkarten basierend auf PCIE

Gegenwärtig ist die schnelle Entwicklung der Internettechnologie Zeuge der massiven Anwendung von E-Mail, Online-Zahlung und persönlicher Kommunikation. Vor diesem Hintergrund ist die Informationssicherheit weltweit ein wichtiges Forschungsthema. Die PKI-Technologie (Public Key Infrastructure) bietet Sicherheitsdienste unter Verwendung der Theorie und Technologie öffentlicher Schlüssel. Die PCIE-Technologie (Peripheral Component Interface Express) hat breite Anwendung in Hochgeschwindigkeitsgeräten als I/O-Busstandard der dritten Generation gefunden, der serielle Datenübertragung und Punkt-zu-Punkt-Verbindungstechnologie anwendet. Im Bereich des digitalen Systemdesigns führt eine relativ hohe Taktfrequenz zu einigen Problemen in Bezug auf Signalintegrität, Leistungsintegrität und Übersprechen, und herkömmliches PCB-Design erfüllt die Anforderungen an die Systemstabilität nicht.

Dieser Artikel bietet ein PCB-Designschema für eine Hochgeschwindigkeits-Passwortkarte basierend auf PCIE gemäß den Vorteilen der seriellen Hochgeschwindigkeitsübertragung von PCIE.

Gesamtdesignschema

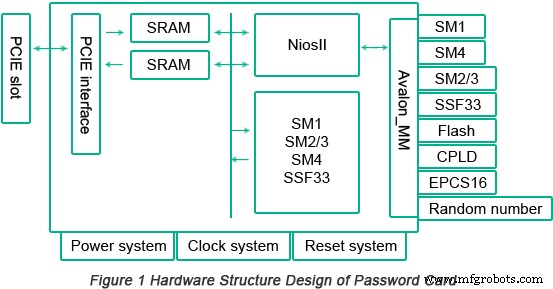

Der FPGA-Chip EP4CGX50CF23C6N, der zu Cyclone IV GX gehört und von Altera entwickelt wurde, wird in diesem Design verwendet, das ein PCIE-IP-Hardcore-Modul integriert und ein Passwortkartendesign für 4 Hochgeschwindigkeitsdatenübertragungen implementiert. Vier Arten von Chips, Chip 1, Chip 2, Chip 3 und Chip 4, sind in der Lage, jeweils Algorithmen von SM1, SM2/SM3, SM4 und SSF33 zu implementieren und Funktionalitäten der Kennwortkarteninitialisierung, Geheimschlüsselverwaltung, Sicherung und Wiederherstellung und Autorität zu implementieren Management. Passwortkarten werden in PCs eingesetzt, mit der Hauptplatine in PCs über einen PCIE-Steckplatz verbunden und von PCs gesteuert. IP-Hardcore in FPGA wird angewendet, um PCIE zu implementieren, was zur Kommunikation zwischen dem PCIE-Kern und dem SRAM-Cache und dem Steuermodul führt. Als Kontrollzentrum implementiert NiosII die Funktion einer Passwortkartensoftware. Währenddessen implementiert ein zusätzlicher Passwortchip die Kommunikation zwischen jedem Schnittstellenmodul und der Passwortkarte. Das Design der Hardwarestruktur der Passwortkarte ist in Abbildung 1 unten dargestellt.

Hochgeschwindigkeits-PCB-Design

• Stapelung und Layout

Das Stackup-Design ist das wichtigste Problem, das berücksichtigt werden sollte, und ein vernünftiges Stackup-Design kann die EMI-Strahlung (elektromagnetische Interferenz) hemmen, die transiente Spannung auf der Stromversorgungsebene oder der Erdungsschicht so gering wie möglich halten und das elektromagnetische Feld von Signal und Leistung abschirmen. Im Allgemeinen werden beim Entwurf digitaler Hochgeschwindigkeitsschaltungen mehrschichtige Platinen und mehrere Leistungen angewendet. Das PCB-Stacking-Design wird auf der Grundlage umfassender Elemente implementiert, darunter Schaltungstaktfrequenz, PCB-Herstellungskosten, Pin-Dichte, Herstellungszeit und Zuverlässigkeit. Darüber hinaus sollten Schichten von Mehrschichtplatten symmetrisch gehalten werden und die Anzahl der Platten sollte eine gerade Zahl sein, da ein asymmetrisches Stapeldesign ein Verziehen der Platten verursacht. Die in diesem Artikel entworfene Passwortkarte ist über den PCIE-Steckplatz mit dem PC verbunden, und die Größe und Form der Leiterplatte ist mit einer Höhe von etwa 67 mm und einer Länge von etwa 174 mm festgelegt, wobei der PCIE X4-Schnittstellenstift unten konfiguriert wird. Durch die hohe Bauteildichte und das dicke Routing wird die Anzahl der Leiterplattenlagen auf 6 Lagen mit Aufteilung von Signallage, Leistungslage, Signallage, Leistungslage, Masselage, Signallage aufgenommen. Dieses Design enthält 3 Signalschichten, 1 Erdungsschicht und 2 Leistungsschichten und bietet die für die Signalintegrität erforderliche Umgebung.

Nach der Festlegung der Leiterplattenbestückung sollten Baugruppen und Layout umgesetzt werden. Erstens muss die Position der Komponenten in Übereinstimmung mit den Abmessungen und dem Muster der Leiterplatte programmiert werden, wobei die Leitungsverbindung, die funktionale Unterteilung und die Trimmung und Schönheit zwischen den Komponenten berücksichtigt werden. Dann müssen die Komponenten entsprechend den verschiedenen Stufen der Komponentenspannung vernünftig verteilt werden, um die Spannungsdrähte so kurz wie möglich zu machen, was in der Lage ist, die Interferenz von Leistungsrauschen zu reduzieren und die Stabilität der Leistung zu erhöhen. Bei der Chipplatzierung sollte auf die Beziehung zwischen seiner Hilfsschaltung und seinem Chip und auf die Platzierung des Kristalloszillators hinter den Taktpins geachtet werden. Hochrauschende Komponenten sollten vermieden werden, um den Quarzoszillator herum platziert zu werden, und sollten sich in der Nähe seiner Antriebskomponenten befinden. Darüber hinaus muss die Platzierung der Leistungs- und Signalstifte jedes Chips berücksichtigt werden, wobei ihre Positionen und Richtungen basierend auf den angeschlossenen Leitungen angepasst werden. Da das Verhältnis von Länge und Breite der Passwortkarte mehr als 2:1 beträgt, wobei die Positionen von PCIE-Steckplatz, Ladelöchern und Anzeige-LED fest sind, muss das Komponentenlayout für feste Komponenten zuerst beim Komponentenlayout berücksichtigt werden. Darüber hinaus sollte aufgrund der großen Anzahl von Verbindungsleitungen zwischen Bauteil und FPGA das Bauteillayout mit FPGA als Mitte vor Positionen anderer Bauteile implementiert werden, damit der obere und untere Raum der Leiterplatte effektiv in Ordnung genutzt werden können um genügend Platz zwischen Komponenten und Komponenten und Positionierungslöchern zu lassen.

• Leistungsdesign

Beim Design von Hochgeschwindigkeits-Leiterplatten steht das Design des Stromversorgungssystems in direktem Zusammenhang mit dem Erfolg des gesamten Systems. Durch Strom und Masse erzeugtes Rauschen sollte auf ein Minimum reduziert werden, um die Zuverlässigkeit der Produkte zu gewährleisten. Die Anwendung des Stromverteilungsschemas beim Schichtverfahren bezieht sich auf die Tatsache, dass Strom durch das Metall auf der gesamten Schicht verteilt wird, wodurch die Stromimpedanz und das Rauschen verringert und die Zuverlässigkeit erhöht werden. Da mehrere Leistungen von PCB betroffen sind, sollte ein Multi-Power-Layer-Design angewendet werden, das in der Lage ist, öffentliche Impedanzkopplungsinterferenzen als Rauschschleife zu eliminieren. Die Anwendung einer Entkopplungskapazität ist in der Lage, das Problem der Leistungsintegrität zu lösen, da ein Kondensator nur auf der unteren oder obersten Schicht der Leiterplatte platziert werden kann, basierend darauf, welche Drähte, die die Entkopplungskondensatoren verbinden, kurz und breit sein sollten. Je nach Chipmaterial kann der durch Stromleitungen fließende Strom berechnet und die Breite der Leitungen bestimmt werden. Je breiter die Leitungen sind, desto mehr Strom können sie führen. Die experimentelle Formel wird wie folgt dargestellt:W(Linienbreite:mm) ≥ L(mm/A) x I(Strom:A)

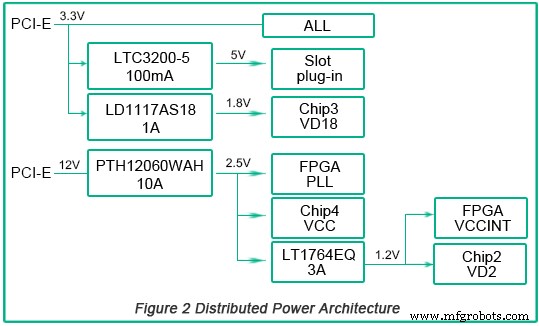

Mehrere Stromversorgungen auf der Leiterplatte beziehen eine oder zwei Arten von Strom von der Stromversorgungsplatine über die Rückwand, und die Leistung wird dann in eine andere Leistung umgewandelt, die von den Komponenten benötigt wird. Die Energieumwandlung wird in zwei Architekturen unterteilt:zentralisierte Energiearchitektur und verteilte Energiearchitektur. Ersteres bezieht sich auf Strom, der von einer unabhängigen Stromversorgung bereitgestellt und dann in alle Arten von erforderlichen Leistungen umgewandelt wird, während letzteres sich auf eine mehrstufige Stromumwandlung bezieht. Da die zentralisierte Stromversorgungsarchitektur die Nachteile hoher Kosten und großer PCB-Fläche aufweist, wird in diesem Design eine verteilte Stromversorgungsarchitektur angewendet. Die kryptografische Karte betrifft 6 Potenzen, darunter 12 V, 3,3 V, 5 V, 2,5 V, 1,2 V und 1,8 V. Dieses Design beginnt mit der Beteiligung von 3,3 V und 12 V am PCIE-Steckplatz, und dann kann die 3,3-V-Stromversorgung 5 V-Strom und 1,8 V-Strom über den Spannungswandlungschip erzeugen und Strom für Plug-in und Chip 3 liefern. Als nächstes kommt 12 V-Strom in 2,5-V-Strom umgewandelt, um FPGA und Chip 4 mit Strom zu versorgen. Schließlich wird 2,5-V-Strom in 1,2-V-Strom umgewandelt, um FPGA und Chip 2 mit Strom zu versorgen. Die verteilte Stromarchitektur der Kryptographiekarte ist in Abbildung 2 unten dargestellt. P>

• Durchgangsloch-Design

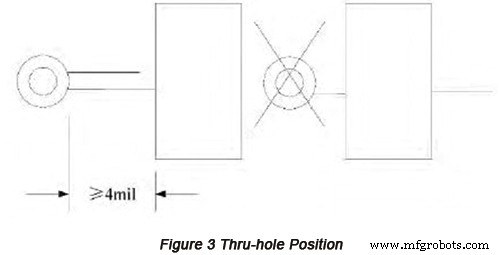

Beim Design-Layout für mehrschichtige PCBs mit hoher Dichte sollten Durchgangslöcher angebracht werden, die Signale von einer Schicht zu einer anderen Schicht übertragen, um eine elektrische Kommunikation zwischen den Schichten bereitzustellen. Die Positionsgestaltung von Durchgangslöchern muss mit großer Sorgfalt ausgeführt werden. Es dürfen keine Durchgangslöcher auf dem Pad platziert werden und es kann eine gedruckte Leitung zum Anschluss aufgebracht werden, was sonst zu Problemen wie Tombstone und unzureichendem Lot führt. Die Lötmaske muss auf das Durchgangsloch-Pad mit einem Abstand von 4 mil aufgetragen werden, und Durchgangslöcher dürfen nicht in der Mitte des Pads für Chipkomponenten auf der Lötseite platziert werden. Die Position der Durchgangslöcher ist in Abbildung 3 unten dargestellt.

Außerdem darf die Durchgangslochposition nicht zu nahe am Goldfinger sein, dessen Steckseite eine Fase enthalten soll. Um Leiterplatten in den PCIE-Steckplatz eingesteckt zu machen, kann eine Abschrägung von (1~1,5) x 45° an zwei Seitenkanten der Einsteckkarte entworfen werden.

• Hochgeschwindigkeits-Signalrouting

Beim Routing muss die Verteilung sinnvoll angepasst werden, um die Verbindungsleitungen so gering wie möglich zu halten, damit das Übersprechen reduziert werden kann. Beim Hochgeschwindigkeits-Digitalsignal-Routing sollte die Signalschicht in der Nähe des Multi-Power-Layer-Routings weit von der Leistungsbezugsfläche entfernt sein, um die Erzeugung eines Rückwegs durch den Signalstrom zu vermeiden.

Da die Taktsignalfrequenz von Hochgeschwindigkeitsschaltkreisen relativ hoch ist, beeinflussen Jitter, Drift und Verformung das System stark, so dass Hochgeschwindigkeits-PCB-Design kleine Signalwelleninterferenzen erfordert. Daher sollte zunächst das Problem der Taktverteilung und des Routings betrachtet werden. Das Routing muss auf Hochgeschwindigkeits-Taktsignalen implementiert werden, und das Routing der Haupttaktsignalleitungen muss so kurz wie möglich, gerade und frei von Durchgangslöchern und Leistungsteil sein, um das Übersprechen zwischen Takt und Leistung zu verhindern. Wenn mehrere Takte mit unterschiedlichen Frequenzen auf derselben Platine verwendet werden, dürfen zwei Taktleitungen mit unterschiedlichen Frequenzen nicht parallel geführt werden. Bei mehreren Komponenten, die Taktsignale mit derselben Frequenz verwenden, kann das Netzwerk jedoch nach Spinnentyp, Baumtyp und Zweigtyp verteilt werden.

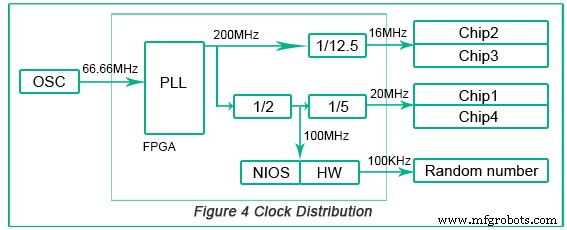

Bei kryptografischen Hochgeschwindigkeitskarten erhält das FPGA einen Takt von 66,66 MHz durch den Kristalloszillator auf der Leiterplatte. Nach dem Schleifen mit intrinsischen Sperren innerhalb des FPGA wird ein 200-MHz-Basistakt als Schnittstelle für Chip 2 und Chip 3 zum Betrieb des Takts erzeugt. Dann wird ein 100-MHz-Takt nach der intrinsischen Frequenzteilerschaltung als NiosII-Softcore und dem Arbeitstakt der Hardwareschaltung im FPGA bereitgestellt. Die geteilte Frequenz von 16 MHz ist der Arbeitstakt für Chip 2 und Chip 3, während die geteilte Frequenz von 20 MHz der Arbeitstakt für Chip 1 und Chip 4 ist. Die Taktverteilung ist in Abbildung 4 unten dargestellt.

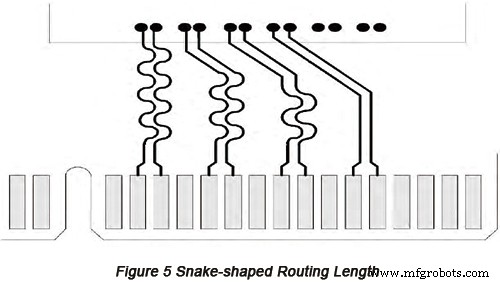

Die Hochgeschwindigkeits-Signalübertragung zwischen PCIE-Steckplatz und PC wird durch eine Hochgeschwindigkeits-Kryptografiekarte in Form von differentiellem Paar-Routing implementiert, um Probleme bezüglich der Signalintegrität zu vermeiden. Im Allgemeinen werden Erdungsdrähte nicht zwischen differentiellen Paarsignalen platziert, da sonst der Kopplungseffekt zwischen differentiellen Paarsignalen zerstört wird. Nach dem Routing der differentiellen Paarsignale wird Kupfer um die Hochgeschwindigkeitssignale der Leiterplatte gelegt, wobei der freie Platz vollständig mit Erdungsdrähten gefüllt wird, um die EMI-Fähigkeit der Schaltung zu erhöhen. Der Schlüssel zum PCB-Routing besteht darin, die Symmetrie von Differentialpaaren aufrechtzuerhalten. Wenn die Länge der differentiellen Paare nicht kompatibel ist, wird die Genauigkeit des Datenlesens und -schreibens durch die verringerte Datenübertragungsrate beeinträchtigt. Um die Gültigkeit des Datenlesens durch das System innerhalb des gleichen Zeitraums sicherzustellen, muss die Verzögerungsdifferenz zwischen Differenzsignalen innerhalb einer zulässigen Kategorie gehalten werden, und die Routing-Länge muss genau gleich sein. Daher kann schlangenförmiges Routing angewendet werden, um dieses Problem zu lösen, indem die Zeitverzögerung angepasst wird. Bei diesem Design wird die Kommunikation per PC über PCIE und eine kryptografische Karte implementiert, und die Übertragung und der Empfang von Hochgeschwindigkeitssignalen werden durch differentielle Paarsignale implementiert, wobei die Länge des PCB-Routings innerhalb von 25 mil gesteuert wird. Das passende Diagramm der schlangenförmigen Routinglänge ist in Abbildung 5 dargestellt.

Hilfreiche Ressourcen

• Wie man hochwertige PCBs entwirft

• PCB-Designelemente, die die SMT-Fertigung beeinflussen

• Forschung zum Hochgeschwindigkeits-PCB-Design in eingebetteten Anwendungssystemen

• Differentielle isometrische Verarbeitung und Simulationsüberprüfung von Hochgeschwindigkeits-PCB-Designs

• PCB-Fertigungsservice mit vollem Funktionsumfang von PCBCart – Mehrere Mehrwertoptionen

• Erweiterter PCB-Bestückungsservice von PCBCart – ab 1 Stück

Industrietechnik

- PCB-Materialien und Design für Hochspannung

- Flex- und Starrflex-Biegefähigkeiten im PCB-Design

- Schritte und Verfahren zum Schutz Ihres PCB-Designs

- Ein Leitfaden vom Schaltplan zum PCB-Design basierend auf Altium Designer

- Rückschläge und Lösungen im HF-PCB-Design

- 3 Routing-Techniken beim PCB-Design von Hochgeschwindigkeits-Signalschaltungen

- Hochgeschwindigkeits-Layout-Tipps

- Design der internen Wärmeableitung von PCB basierend auf dem Wärmemodell

- Diskussion über Strom und Masse bei der elektromagnetischen Kompatibilität von PCB

- Differentiale isometrische Verarbeitung und Simulationsverifizierung von Hochgeschwindigkeits-PCB-Design