Forschung zum Hochgeschwindigkeits-PCB-Design in eingebetteten Anwendungssystemen

Moderne elektronische Systeme entwickeln sich im Trend zu kleinem Gehäuse, großem Umfang und hoher Geschwindigkeit, da die Chipdichte bei SLSI (Super-Large-Scale-Integration) immer größer wird, was einige unvermeidliche Probleme mit sich bringt, wie z. B. Analyse und Handhabung mit den Verbindungs- und Stapelproblemen beim Hochgeschwindigkeits-Schaltungsdesign. Gegenwärtig erreicht die Hochfrequenz elektronischer Produkte Hunderte oder Tausende von MHz, und sowohl die Anstiegsflanke als auch die Abfallflanke werden so steil, dass die PCB-Layoutregeln und die Dielektrizitätskonstante des Substratmaterials für die elektrische Leistung des Systems beim Prozessdesign äußerst entscheidend sind solche Produkte.

Als bedeutender Prozess und Schritt in der Mehrheit der gegenwärtigen elektronischen Produktforschung hat das Hochgeschwindigkeits-PCB-Design die Hauptprobleme gesehen, darunter Timing-Probleme, Rauschinterferenzen und EMI (elektromagnetische Interferenz), deren Lösungen mit dem normalen Betrieb des Systemdesigns zusammenhängen.

Heutzutage führen herkömmliche Designmethoden zu einer geringen Zuverlässigkeit und Erfolgsrate von Produkten, die einen hohen praktischen Wert und breite Markterwartungen für die Forschung zum Hochgeschwindigkeits-PCB-Design in eingebetteten Anwendungssystemen bieten.

Design des Systemschemas

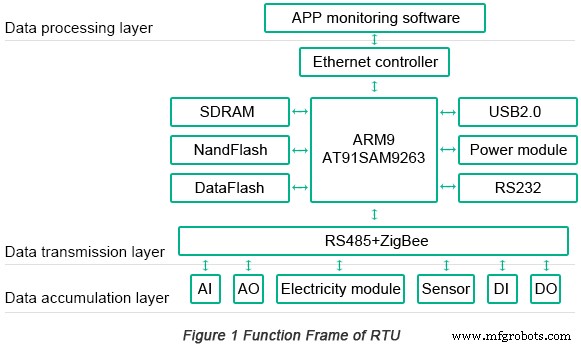

Abbildung 1 zeigt den Funktionsrahmen der eingebetteten RTU (Remote Terminal Unit).

Aus Fig. 1 ist ersichtlich, dass dieses System eine vertikale Kommunikationsstruktur ist, die aus einer Datenakkumulationsschicht besteht, die eine Elektrizitätsenergieeinheit, eine Sensoreinheit und eine analoge Mengenmesseinheit enthält, eine Datenübertragungsschicht, die ein Gateway enthält, das die Daten in der Datenakkumulationsschicht durch die anpasst Befehl vom Internet-Empfangsingenieurzentrum und der Datenverarbeitungsschicht, die von der APP-Überwachungssoftware implementiert wird, Daten in Echtzeit speichern und analysieren und Datenkurven gegenüber der Benutzeroberfläche erstellen, sodass die Flexibilität und Verwaltungseffizienz der Datenakkumulation erhöht werden.

Hardwarerahmen des RTU-Systems

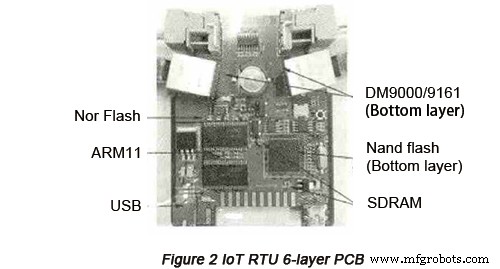

Diese eingebettete IoT-RTU-Systemhardware besteht hauptsächlich aus USB2.0, AT91SAM9263-Prozessor, CAN, SDRAM, NAND-Flash, Daten-Flash, Ethernet-Controller, Taktchip, RS232/485-Schnittstelle, Energieverwaltung und Datenakkumulation.

Dieses Design wird von einem Linux-Betriebssystem betrieben und bietet höhere Speicher- und Geräteverwaltungsmöglichkeiten, sodass eine Echtzeitplanung für mehrere Missionen implementiert wird, die einen komplexen Algorithmus und ein Kommunikationsprotokoll enthält, das für die Netzwerkverbindung, die Datenkommunikation und die Akkumulation der Konfiguration verantwortlich ist. Abbildung 2 ist die in diesem Artikel entworfene RTU-Leiterplatte.

Dieses System unterstützt den Dual-Stack von IPv6 und IPv4 und ist in der Lage, die Schnelligkeit und Echtzeitfähigkeit zu implementieren. Hinsichtlich der Datenspeicherung kann die Anforderung der lokalen Speicherung unter der Bedingung der Kommunikationssperre erfüllt werden. In Bezug auf die Kommunikationsschnittstelle verfügt es über verschiedene Felddaten-Kommunikationsschnittstellen, einschließlich RS485, RS232 und CAN, die das Modbus RTU-Kommunikationsprotokoll unterstützen und die Anforderungen verschiedener Schnittstellen und unterschiedlicher Kommunikationsraten erfüllen.

PCB-Design des RTU-Systems

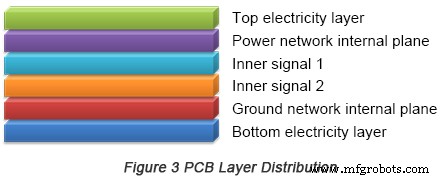

• PCB-Stacking-up-Design des Systems

Die Anzahl der Lagen von PCBs liegt normalerweise im Bereich von 2 bis 32, basierend auf der Schwierigkeit des Designs. Die 6-Lagen-Leiterplatte in diesem Design wird gemäß der Komponentenpackungsdichte, dem kleinen Layout-Routingraum und der hohen Signalfrequenz bestimmt. Diese PCB-Schichtverteilung ist in Abbildung 3 unten dargestellt.

Die Streifenleitungskonfiguration wird in diesem System für FLASH und SDRAM übernommen, und das Routing wird auf dem inneren Signal 1 und dem inneren Signal 2 implementiert.

• PCB-Einschränkungsregeln in diesem System

Während des Hochgeschwindigkeits-PCB-Designs werden Impedanzkontinuität und EMI stark durch Abstand, Länge und Breite der Drähte und die angrenzende Verarbeitung von Schleifen beeinflusst. Die Qualität des Komponentenlayouts und des Routings hängt mit dem Erfolg des endgültigen Designs zusammen, sodass PCB-Einschränkungsregeln vernünftig umgesetzt werden müssen.

Hyper Lynx verfügt über eine Funktion zur Interferenz mit der Diagrammanalyse, und das IBIS-Modell kann angewendet werden, um die Verlustübertragung, Differenzsignale und das Durchgangslochmodell, das sich mit der Frequenz ändert, genau zu simulieren. Das Hauptnetzwerk wird vor dem Routing nach Leitung simuliert, um die PCB-Stapelstruktur und die Routing-Impedanz zu verbessern, und es werden vor dem Simulationsergebnis Regeln zur Beschränkung des Routings von Hochgeschwindigkeits-PCBs entwickelt, um die Designeffizienz zu steigern.

• PCB-Simulation dieses Systems

Im Prozess des Hochgeschwindigkeits-PCB-Designs wird ein ideales Übertragungsleitungsmodell für die Simulation des vorderen Anschlusses angewendet, wobei begrenzte Signalleitungen einmal simuliert werden. Die Übertragungsleitungen am hinteren PCB-Anschluss sind jedoch tatsächlich Routing-Leitungen der PCB mit Einfluss von Durchgangslöchern und Ebenenverschiebungen. Unter diesen Umständen ist das erhaltene Simulationsergebnis äußerst zuverlässig.

Beim Design des Kernschaltkreises des Systems muss der Anschlussanpassungswiderstand des Einzelanschlusssignals im Bereich von 40 bis 60 Ω und der Übersprechschwellenwert zwischen den Signalleitungen 165 mV betragen. Um die Netzwerk-Controller von DM9000 und DM9161 für die Kommunikationsgeschwindigkeitsrate von 100 MBit/s selbstanpassbar zu machen, muss außerdem die differentielle Impedanz innerhalb der Kategorie von 100 ± 5 Ω liegen. Die PCB-Simulation wird durch die von Mentor Graphic entwickelte Hyper Lynx-Simulationssoftware auf SDRAM, Ethernet-Differentialleitungen, Leistungsintegrität und EMV implementiert.

a. SDRAM-Design

Beim Design von Streifenleitungen sind Übersprechen und Durchgangslöcher die Hauptursachen für Zeitverzögerungen. Obwohl die Leiterplatte gemäß den Routing-Regeln fertiggestellt wird, die von Line-Simulationswerkzeugen bestimmt werden, sind einige Probleme unvermeidlich, wie z. B. zu viele Komponentenpins und begrenzte Leiterplattenabmessungen. Daher ist es notwendig, mehrere Netzwerke durch Board-Simulationswerkzeuge geeignet zu simulieren.

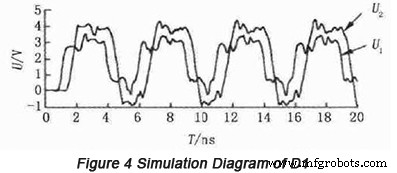

Basierend auf dem Simulationsergebnis liegt die Übersprechintensität des analogen Netzwerks EBI_D0 und EBI_D2 über 165 mV. Die beiden Netze greifen EBI_D1 an und suchen Koppelstelle, weil der Abstand zwischen schlangenförmigen Linien im gelben Markierungsbereich ungeeignet ist. Es kann gezeigt werden, dass die Vergrößerung des Routingabstands hilft, ein solches Problem zu beseitigen. Was uns jedoch wirklich interessiert, ist, warum das Hack-Netzwerk so stark gestört wird. Der Grund liegt möglicherweise in der ungeeigneten Widerstandswahl, die zu einer nicht passenden Impedanz führt. Der bisher ermittelte Widerstandswert des Abschlusswiderstandes beträgt 43,1Ω. Im Erregungszustand von 220 MHz wird die Analysesimulationswelle des Netzwerks EBI_D1 in Abbildung 4 unten gezeigt.

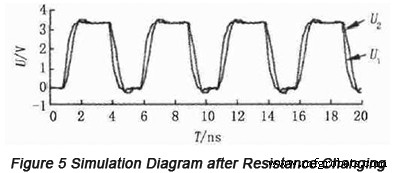

Basierend auf Abbildung 4 tritt eine Impedanzdiskontinuität auf der EMI_D1-Übertragungsleitung auf, und es findet eine Verformung der Signalwellen statt. Obwohl kein Systemfehler beim Starten verursacht werden kann, kann die Stabilität des Produktbetriebs kaum garantiert werden. Back-to-Board-Simulation, Durchgangslöcher und Schadenssimulation werden angewendet, um den Anschlusswiderstand von EBI_D0 und EBI_D1 auf 46,9 Ω zu ändern. Daher ist das Simulationsdiagramm des Übersprechens nach der Widerstandsänderung in Abbildung 5 unten dargestellt.

Anhand dieser Abbildung lässt sich verdeutlichen, dass das Netzwerksignal verbessert und die auf EBI_D1 hervorgerufene Interferenzintensität deutlich reduziert wurde.

b. Entwurf eines differenziellen Internet-Busses

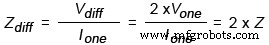

Mit Attributen von Hochgeschwindigkeits- und 3GIO-Verbindungen wendet das von Hyper Lynx entwickelte Board-Simulationsmodul superschnelle serielle Datenpfad- und Quellensynchronisierungstechnologie auf der Grundlage eines Differenzsignalbusses an und bietet ein bequemes und hocheffektives Lösungsschema für Hochgeschwindigkeits-PCB-Design. Sowohl DM9000 als auch DM9161 in diesem System verfügen über zwei Paare von Hochgeschwindigkeits-Signal-Differentialbussen:TX+, TX- und RX+, RX- mit einer Differenzimpedanz von 100 Ω. Aufgrund der Übertragungstheorie kann die differentielle Impedanz basierend auf der Formel berechnet werden: .

.

In dieser Formel bezieht sich Z auf die Übertragungsimpedanz jeder Signalleitung, die einen entscheidenden Einfluss auf die Kommunikationsentfernung und die Rauschfestigkeit hat. Hier wird DM9000 abgeholt, um differentiell an das Netzwerk TP_E_TX+ und TP_E_TX- zu senden. Um den Reflexionseffekt zu verringern, wird bei Signalleitungen mit aufgebrachten Durchgangslöchern ein Widerstand von 100Ω parallel geschaltet.

c. Leistungsintegritätsdesign dieses Systems

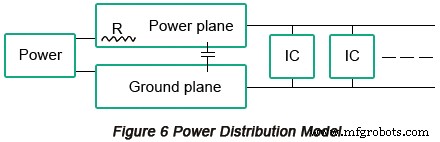

Abbildung 6 ist ein grundlegendes Stromverteilungsmodell, bei dem Strom zu jedem Träger durch Stromschichten und dann zur Masseschicht übertragen wird.

Im Prozess des Hochgeschwindigkeits-PCB-Designs muss der Energieverbrauch in jeder Einheit im Schaltungssystem mit der Breite des Stromnetzes korrekt verteilt und angemessen verstärkt werden.

Die Leistungsintegrität von 6 Schichten kann wie folgt zusammengefasst werden:Der maximale Druckabfall beträgt 2,1 mV, fast 0,06 %; die maximale Stromdichte beträgt 16,3 mA/m²; Innerhalb einer geeigneten Kategorie steigt die Temperatur der Leiterplatte, wenn die Stromdichte 50 mA/m² übersteigt, was den Hauptchip und die Signalleitungen während des Betriebs beeinflusst. Die Erhöhung der Kupferbreite ist in der Lage, die Stromdichte zu verringern, und die Erhöhung der Dicke der Signalleitungen ist hilfreich, um die Temperatur der Leiterplatte zu senken.

d. Analyse der elektromagnetischen Verträglichkeit des Systems

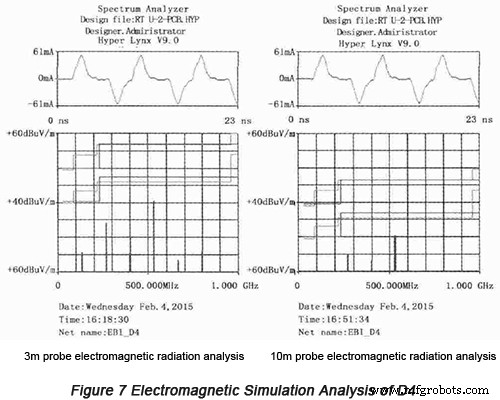

Elektromagnetische Störungen werden üblicherweise als Träger mit Nutzsignalen im Wege der Kopplung übertragen. Bei diesem Design wird die Hyper Lynx-Simulationssoftware angewendet, um die Strahlungsintensität der Leiterplatte nach dem vorläufigen Design zu analysieren. Die entscheidende Signalleitung, D4, wird zwischen ARM9 und SDRAM mit Sondenpositionen von 3 m bzw. 10 m aufgenommen. Unter der Situation einer Anregungsquelle von 220 MHz können sowohl FCC- als auch CISPR-Simulationsdaten nach internationalem Standard erhalten werden, wie in Abbildung 7 unten dargestellt.

Basierend auf den Simulationsergebnissen führt der kurze Abstand zur Leiterplatte zu einer hohen Strahlung von der Leiterplatte und die Strahlung ändert sich mit der Änderung der Signalfrequenzen. Im Prozess des Hochgeschwindigkeits-Schaltungsdesigns kann die PCB-Entstörung optimiert werden, während die Rauschabstrahlung reduziert werden muss.

Hilfreiche Ressourcen

• Hochgeschwindigkeits-Layout-Tipps

• Hochgeschwindigkeits-Leiterplatten-Routingtechniken zur Reduzierung des Einflusses von EMI

• Missverständnisse und Strategien zum Hochgeschwindigkeits-Leiterplattendesign

• Eingebettete Komponenten PCB-Fertigungstechnologie

• Embedded-Technologie und Komponenten-Embedded-PCB-Montageverfahren

• Vollfunktions-PCB-Fertigungsservice von PCBCart - Mehrere Mehrwertoptionen

• Erweiterter PCB-Montageservice von PCBCart - Beginnen Sie ab 1 Stück

Industrietechnik

- PCB-Layout-Software

- Überlegungen zum PCB-Layout

- Ultiboard-PCB-Design-Tutorial

- 3 Routing-Techniken beim PCB-Design von Hochgeschwindigkeits-Signalschaltungen

- Hochgeschwindigkeits-Layout-Tipps

- Überlegungen zum thermischen PCB-Design

- Differentiale isometrische Verarbeitung und Simulationsverifizierung von Hochgeschwindigkeits-PCB-Design

- Die häufigsten Fehler, die Ingenieure beim PCB-Design machen

- Signalintegritätsanalyse und PCB-Design auf gemischten Hochgeschwindigkeits-Digital-Analog-Schaltkreisen

- Hochgeschwindigkeits-PCB-Design-Herausforderungen zur Signalintegrität und ihre Lösungen