Einschaltphasen-Determinismus:Multichip-Synchronisation verwenden

Die Integration mehrerer Digital-Signal-Processing (DSP)-Blöcke, Breitband-Digital-Analog-Wandler (DACs) und Breitband-Analog-Digital-Wandler (ADCs) in einem einzigen monolithischen Chip ermöglicht nun die Entlastung energiehungriger FPGA-Ressourcen ermöglichen Plattformen mit geringerer Stellfläche, geringerem Stromverbrauch und erhöhter Kanalanzahl, die mit höheren Abtastraten als bisher erreichbar sind. Zusammen mit dieser neuen Fähigkeit kommen neuartige Multichip-Synchronisationsalgorithmen (MCS) in diesen integrierten Schaltkreisen (ICs), die es Benutzern ermöglichen, eine bekannte (deterministische) Phase für alle Kanäle zu erreichen, wenn sie das System mit Strom versorgen oder anderweitig Softwareänderungen am System vornehmen. Diese deterministische Phase vereinfacht daher die breiteren Kalibrierungsalgorithmen auf Systemebene, die erforderlich sind, um die Synchronisierung aller Kanäle am Ausgang oder Eingang der an diese ICs angeschlossenen Front-End-Netzwerke zu erreichen. Dieser Artikel präsentiert experimentelle Ergebnisse, die diese MCS-Fähigkeit unter Verwendung einer 16-Kanal-Empfänger-/Senderplattform demonstrieren, die aus mehreren Digitizer-ICs, Taktquellen und digitalen Schnittstellen besteht.

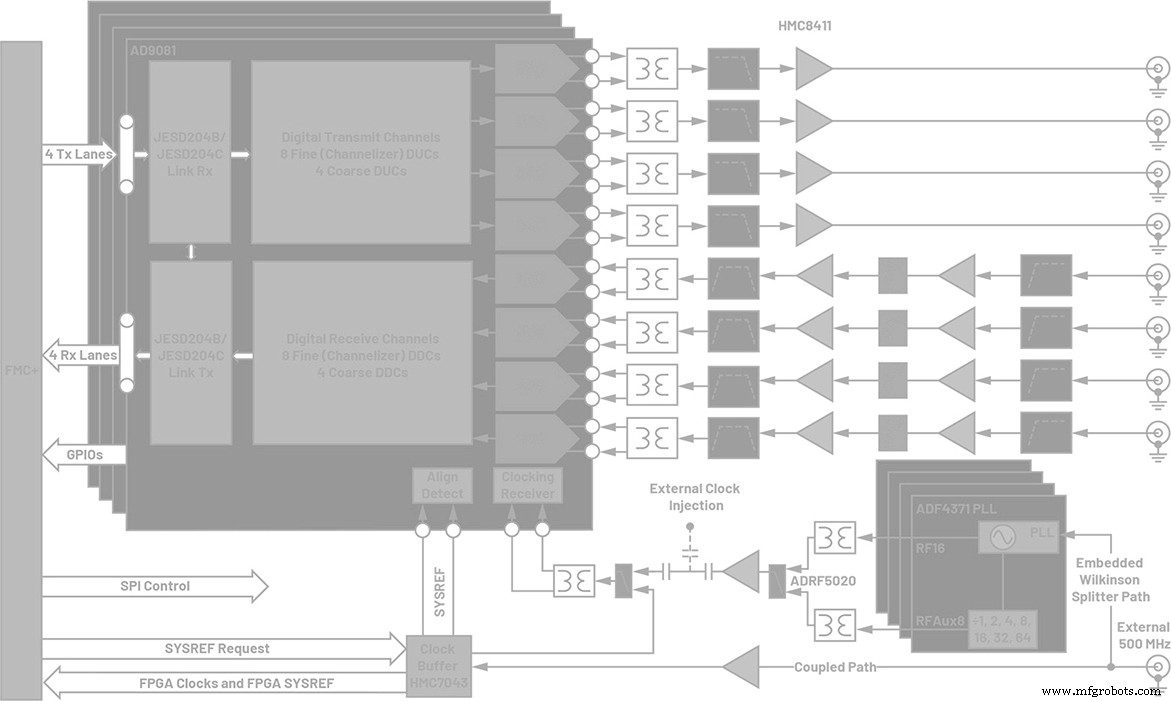

Blockdiagramm des High-Level-Systems

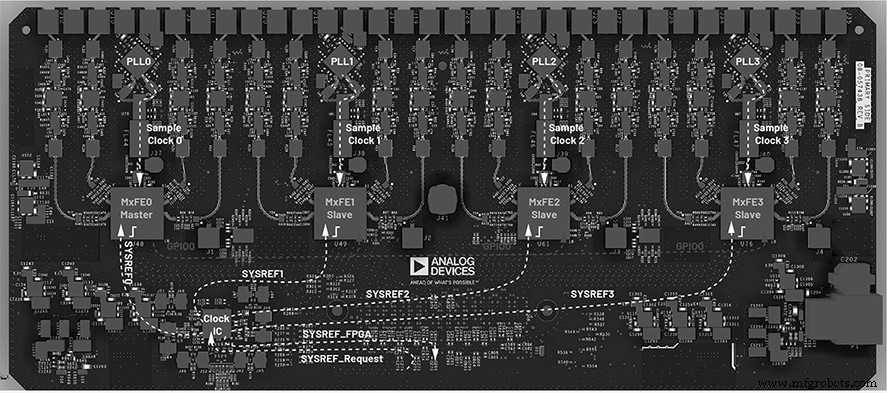

Ein Blockschaltbild des für diesen Test verwendeten Systems ist in Abbildung 1 dargestellt und besteht aus vier integrierten DAC/ADC/DSP-ICs, die jeweils aus vier 12 GSPS-DACs, vier 4 GSPS-ADCs und 12 digitalen Aufwärtswandlern (DUC) und 12 digitalen . bestehen Downconverter (DDC) Blöcke.

klicken Sie für das Bild in voller Größe

Abbildung 1. Ein High-Level-Blockdiagramm des Systems, das verwendet wird, um MCS- und Mehrkanal-Kalibrierungsalgorithmen zu demonstrieren. (Quelle:Analog Devices)

Die DUCs/DDCs ermöglichen eine Frequenzumsetzung und/oder Interpolation/Dezimierung innerhalb des digitalen Bereichs. Unter Verwendung eines einzelnen 500-MHz-Referenztakts, der auf die Platine eingespeist wird, wird dann ein referenzverriegelter Taktpuffer verwendet, um die für MCS benötigten Systemreferenzsignale sowie die für die digitale Schnittstelle zum Basisbandprozessor (BBP) erforderlichen Takte zu erzeugen. Das System enthält außerdem vier separate Phasenregelschleifen(PLL)-Synthesizer, die die 12-GHz-Quellen erzeugen, die zum Takten jedes digitalisierenden ICs aus der gemeinsamen Referenz benötigt werden. An jedem Digitizer-Ausgang/-Eingang ist ein HF-Frontend angebracht, das ein gefiltertes und verstärktes Signal zu/von den randgekoppelten HF-Anschlüssen erzeugt. Es wird eine vollständige Stromverteilungslösung implementiert. Alle für das System benötigten Spannungen werden aus einer einzigen 12-V-Quelle erzeugt. Alle Sendesignale breiten sich auf der Unterseite der Platine aus, während sich alle Empfangssignale auf der Oberseite der Platine ausbreiten, um die optimalste Kanal-zu-Kanal-Isolation zu erreichen.

Unterarray-Uhrenbaumstruktur

Wie bereits erwähnt, besteht der Taktbaum des Subarrays aus einer einzelnen 500-MHz-Referenzquelle, die aufgeteilt und an die Referenzeingänge von vier separaten PLL-Synthesizer-ICs gesendet wird, wie oben in Abbildung 1 gezeigt. Dieses 500-MHz-Signal wird ebenfalls um 10 dB gekoppelt, verstärkt , und in einen anderen Taktpuffer-IC gesendet, der für die Erzeugung der Systemreferenzen (SYSREFs) und BBP-Takte verantwortlich ist, die für die digitale Schnittstelle erforderlich sind. Das Ziel dieses Uhrenbaums ist dreifach, da es:

- Ermöglicht SYSREF-Verzögerungen der einzelnen Kanäle, um Abweichungen der Leiterbahnlänge zwischen den ICs zu korrigieren.

- Ermöglicht eine individuelle PLL/Synthesizer-Phaseneinstellung und gewährleistet daher die Synchronisation über die jeweiligen Digitizer-IC-Taktquellen, um alle induzierten Wärmegradienten innerhalb des Systems zu kompensieren.

- Ermöglicht dem Benutzer, die erforderlichen Setup-and-Hold-Anforderungen für die Digitalisierungs-ICs zu erfüllen.

Die Taktbaum-ICs wurden ausgewählt, um zu zeigen, dass verschiedene Anomalien des Platinenlayouts in Software und/oder Hardware mit Hilfe von digitalen und analogen Verzögerungsblöcken, die in diesen Chips vorhanden sind, korrigiert werden können. Letztendlich ist das Ergebnis ein Taktbaum, der allen erforderlichen ICs innerhalb desselben Abtasttaktzyklus jedes dieser ICs einen SYSREF-Impuls liefern kann.

Digitale Schnittstelle mit Basisbandprozessor

Die vier Digitalisierungs-ICs bilden jeweils eine JESD204B- oder JESD204C-Digital-Link-Schnittstelle mit dem BBP. 1,2 Diese Schnittstelle ist für die Übertragung der ADC- und DAC-Codes über die physikalischen Spuren (SERDES) zum und vom BBP verantwortlich. Die Anzahl der in dieser Schnittstelle verwendeten differentiellen SERDES-Traces wird als die Anzahl der Lanes (L) für diese Verbindung bezeichnet. Die über den Link gesendete Konverter-Bitauflösung wird als N’ angesehen. Die Anzahl der kanalisierten Datenpfade, auch als virtuelle Wandler bezeichnet, wird mit M bezeichnet. Die in diesem Artikel gezeigten Ergebnisse verwenden einen JESD204C-Link mit M =16, N' =16, L =4 für die DAC-seitigen Links und M =8 , N' =16, L =2 für die ADC-seitigen Verbindungen.

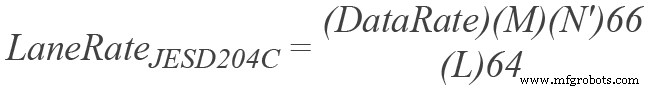

Die Rate, mit der Daten zwischen dem Digitalisierer-IC und dem BBP übertragen und empfangen werden, wird als Lane-Rate bezeichnet. Die DSP-Blöcke auf Silizium (d. h. die DDCs/DUCs) ermöglichen es dem Benutzer, die Digitizer mit einer anderen Rate als der über die physischen Lanes gesendeten Datenrate abzutasten. Als solche hängt die Spurrate von der digital dezimierten/interpolierten Datenrate für jeden Datenpfad ab. Für diese Arbeit wurde eine I/Q-Datenrate von 250 MSPS verwendet. Für eine JESD204C-Schnittstelle ist die Spurrate wie folgt definiert:

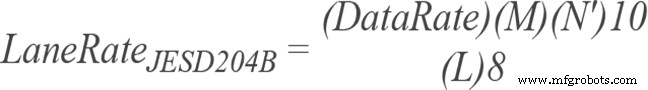

wohingegen für eine JESD204B-Schnittstelle die Spurrate wie folgt definiert ist:

Die in diesem Artikel gezeigten Ergebnisse verwenden eine Lane-Rate von 16,5 Gbit/s sowohl für die ADC- als auch die DAC-seitigen JESD204C-Verbindungen.

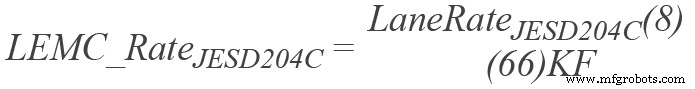

Jeder JESD204B/JESD204C-Link kann innerhalb verschiedener Unterklassen aufgebaut werden. Diese Unterklassen werden basierend darauf getrennt, ob eine Multichip-Synchronisation oder eine deterministische Latenz erforderlich ist. Für diese Arbeit verwenden die gezeigten Daten einen JESD204C-Unterklasse-1-Modus und verwenden daher SYSREF-Signale, um Teile der digitalen Daten auszurichten, die über die mehreren im System vorhandenen Verbindungen übertragen werden. Insbesondere in diesem JESD204C-Unterklasse-1-Modus werden die SYSREF-Signale verwendet, um den lokalen erweiterten Multiblockzähler (LEMC) auszurichten, der mit einer Rate sendet:

wobei F die Anzahl der Oktette pro JESD-Frame pro Lane ist und K die Anzahl der Frames pro einzelnem Multiframe ist. Für diese Arbeit wird F =8 und K =32 und daher eine LEMC-Rate von 7,8125 MSPS verwendet. Die Kenntnis dieser LEMC-Rate ist wichtig, da jede erfolgreiche MCS-Routine zeigen muss, dass HF-Frequenzen, die kein ganzzahliges Vielfaches der LEMC-Rate sind, eine deterministische Einschaltphase erreichen können.

Multichip-Synchronisierungsmethode

Innerhalb dieses Systems bieten die integrierten Breitband-ADC/DAC-ICs MCS-Schaltkreise, um eine deterministische Einschaltphase auf allen Sende- und Empfangs-HF-Kanälen zu ermöglichen, selbst wenn die DUC/DDC-DSP-Blöcke innerhalb des ICs verwendet werden. Diese MCS-Funktion ermöglicht es Benutzern, während einer Werkskalibrierung eine Lookup-Tabelle (LUT) zu füllen, um Betriebsausfallzeiten zu minimieren. Jede erfolgreiche MCS-Demonstration muss in der Lage sein, eine deterministische Phase über alle Kanäle innerhalb des Systems für jeden versuchten HF-Frequenz-, Temperaturgradienten- und System-Energiezyklus bereitzustellen.

Die integrierten ADC/DAC-ICs enthalten 12 DUC-Blöcke und 12 DDC-Blöcke, wie oben in Abbildung 1 gezeigt. Jeder dieser Blöcke enthält einen Interpolations- (DUC) oder Dezimations-(DDC)-Subblock, um die Datenrate des digitalen DAC-Eingangssignals zu ändern oder ADC digitalisiertes Ausgangssignal bzw. In jedem DUC/DDC ist auch ein komplexer numerisch gesteuerter Oszillator (NCO) enthalten, der eine Frequenzumsetzung innerhalb des digitalen Bereichs ermöglicht. Jeder dieser NCOs ist zu einer komplexen Phasenanpassung in Echtzeit fähig, so dass das digitale Signal zwischen dem DAC/ADC und dem BBP modifiziert werden kann, um verschiedene SERDES-Spurlängen-Fehlanpassungen zu kompensieren.

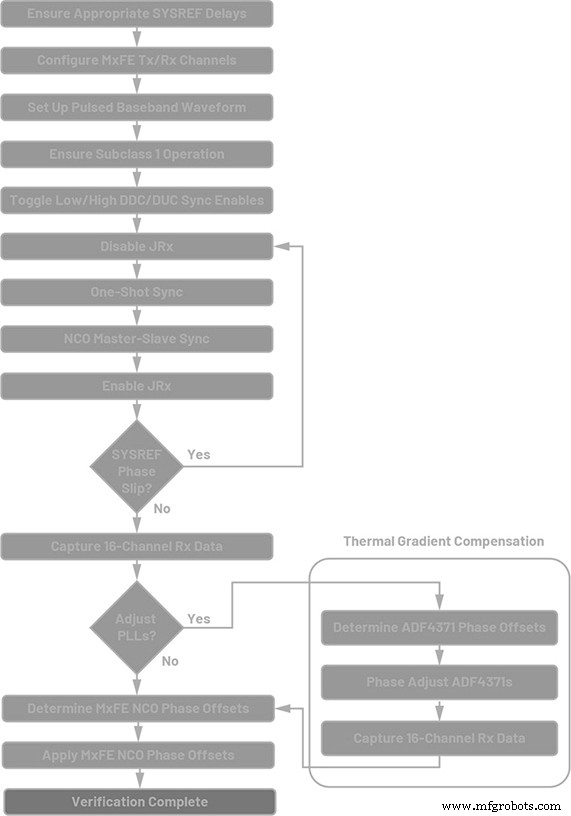

Die MCS-Funktion für diese ADC/DAC-ICs ist dafür verantwortlich, Phasendeterminismus in allen Aspekten des Datenpfads des Digitizer-ICs zu erreichen. Der Arbeitsablauf zum Erreichen von MCS ist in Abbildung 2 dargestellt.

klicken Sie für das Bild in voller Größe

Abbildung 2. Der MCS-Workflow umfasst separate Funktionen, die verschiedene Teile des Datenpfads ausrichten. (Quelle:Analog Devices)

Der MCS-Algorithmus kann in zwei separate Funktionen unterteilt werden:

- One-Shot-Sync:Diese Funktion ist für die Ausrichtung der Basisbanddaten verantwortlich, die über die physischen Lanes aller Digitizer-ICs innerhalb des Subarray-Systems gesendet werden.

- NCO-Master-Slave-Synchronisierung:Diese Funktion ist für die Ausrichtung aller NCOs über alle verschiedenen Digitizer-ICs innerhalb des Subarray-Systems verantwortlich.

Die One-Shot-Sync-Funktion erfordert zunächst, dass der Benutzer die JESD-Link-Parameter (wie M, N’, L usw.) definiert und dann die Synchronisationslogik für jede gewünschte SYSREF-Mittelung konfiguriert (bei Verwendung kontinuierlicher SYSREF-Impulse). Außerdem können gewünschte LEMC-Verzögerungen verwendet werden, um zu erzwingen, dass der LEMC mit einer bestimmten Verzögerung nach der SYSREF-Flanke erzeugt wird. Nachdem dies abgeschlossen ist, aktiviert der Benutzer das One-Shot-Sync-Bit in jedem Digitalisierer-IC und fordert dann an, dass SYSREF-Impulse innerhalb desselben Taktzyklus an jeden IC gesendet werden, wie in Abbildung 3 gezeigt.

Klicken für Bild in voller Größe

Abbildung 3. Der MCS-Algorithmus verwendet SYSREF-Signale, um One-Shot-Sync und GPIO-Signale zu implementieren, um NCO-Master-Slave-Sync zu implementieren, um eine deterministische Phase zu erreichen. (Quelle:Analog Devices)

Für dieses System wurden analoge Feinverzögerungen innerhalb des Taktpuffer-IC eingeführt, um synchrone SYSREFs zu allen Digitalisierer-ICs zu ermöglichen. Eine nachfolgende Überprüfung kann ausgeführt werden, um den erfolgreich durchgeführten One-Shot-Sync-Prozess zu überprüfen, indem Register innerhalb jedes ICs abgefragt werden, die Informationen über die Phasenbeziehung zwischen dem SYSREF-Signal und der LEMC-Grenze jedes IC-Links liefern.

Sobald eine stabile Phase gemessen ist (das heißt, sobald das SYSREF-LEMC-Phasenregister 0) liest, weiß der Benutzer, dass die LEMCs aller Digitalisierer-ICs ausgerichtet sind, und der Benutzer kann dann mit dem NCO-Master-Slave-Synchronisierungsprozess fortfahren. Für diese Aktivität sind die für die One-Shot-Synchronisierung beschriebenen Teilaufgaben in einer vom Chiphersteller bereitgestellten Anwendungsprogrammierschnittstelle (API) enthalten.

Die NCO-Master-Slave-Sync-Funktion weist zuerst einen der Digitalisierer-ICs innerhalb des Subarrays als Master-Chip zu, wie oben in Abbildung 3 gezeigt. Alle anderen Digitalisierer werden dann als Slave-ICs betrachtet. Der Master-IC ist so aufgebaut, dass der GPIO0-Pin dieses Geräts als Ausgang konfiguriert und an die GPIO0-Netze der drei Slave-Digitalisierer-ICs geroutet wird. Die Slave-GPIO0-Netze sind als Eingänge konfiguriert. Der Benutzer kann dann wählen, ob er entweder auf den SYSREF-Impuls, die ansteigende LEMC-Flanke oder die abfallende LEMC-Flanke triggern möchte. Für die in diesem Artikel gezeigten Daten wird die ansteigende Flanke des LEMC als NCO-Master-Slave-Sync-Triggerquelle verwendet und die GPIO-Netze werden durch den BBP statt lokal auf dem Subarray geroutet. Als nächstes werden die DDC-Synchronisationsbits auf Low und dann auf High umgeschaltet, um den ADC-seitigen NCO-Synchronisationsalgorithmus zu aktivieren. Ebenso wird das Ausrichtungsbit des Mikroprozessors auf Low und dann auf High umgeschaltet, um den DAC-seitigen NCO-Synchronisationsalgorithmus zu aktivieren.

Wenn dieser Trigger angefordert wird, bestätigt der Master-Digitalisierer-IC bei der nächsten ansteigenden LEMC-Flanke ein Master-Ausgangssignal durch sein GPIO0-Netz hoch. Dieses Signal breitet sich zu den GPIO0-Eingängen jedes der Slave-Geräte aus. An der nächsten LEMC-Kante erfahren alle Digitizer-ICs einen NCO-Reset-Algorithmus. Danach werden alle LEMC-Impulse im Hinblick auf den NCO-Master-Slave-Sync-Algorithmus ignoriert. Wie bei der One-Shot-Synchronisierung sind diese NCO-Master-Slave-Sync-Unteraufgaben zur Benutzerfreundlichkeit in API-Funktionen enthalten.

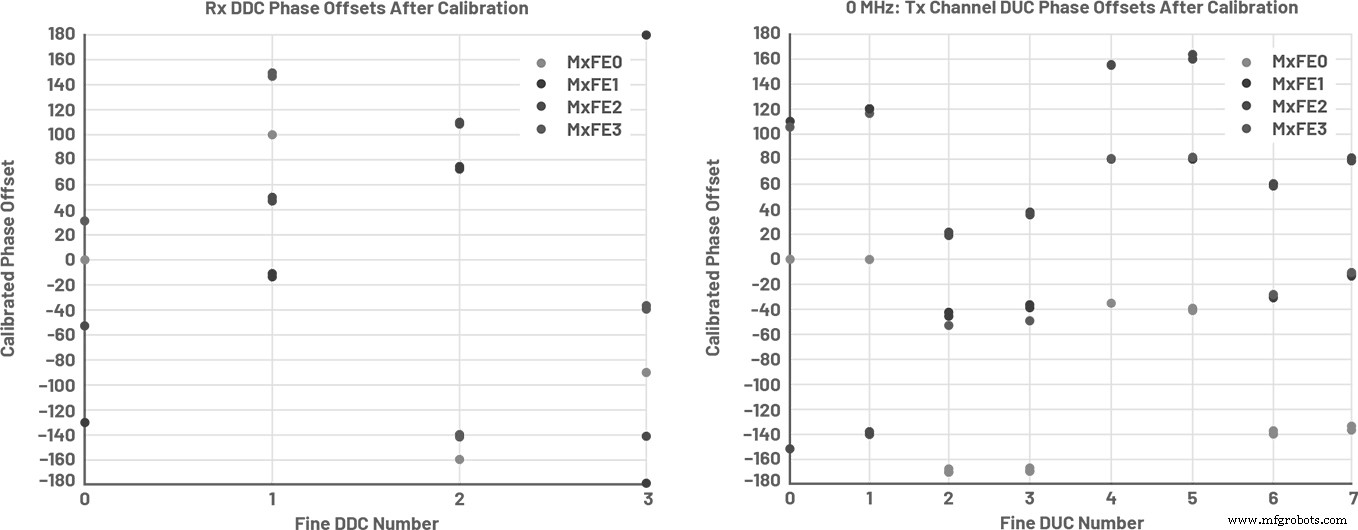

Durch die Verwendung sowohl der One-Shot-Sync- als auch der NCO-Master-Slave-Sync-Funktion werden beide Eingänge an jedem DDC/DUC so ausgerichtet, dass der Ausgangsphasenversatz jedes Empfangs- und Sendekanals nach mehreren Leistungszyklen wiederholbar ist, wie in Abbildung 4 gezeigt in Abbildung 4 zeigt die kalibrierten Phasenverschiebungen über 100 Leistungszyklen (durch mehrere durchgehende Punkte angezeigt) für jeden Empfangs- und Sendekanalisierer, während das System bei jedem Neustart unter einem statischen Temperaturgradienten arbeitet.

Klicken für Bild in voller Größe

Abbildung 4. Die feinen Empfangs-DDCs (links) und die feinen Sende-DUCs (rechts) sind richtig ausgerichtet, wenn der MCS-Algorithmus ausgeführt wird. (Quelle:Analog Devices)

Wie aus den mehreren Punkten in dieser Figur ersichtlich ist, sind die Punkte jeder Farbe für eine gegebene DDC/DUC alle nach Leistungszyklen eng an derselben Position gruppiert, wodurch die deterministische Phase für diesen bestimmten Kanal dargestellt wird. Für die Daten in diesem Test wurden sendeseitig alle acht Kanalisierer-DUCs verwendet, während nur vier der acht Kanalisierer-DDCs verwendet werden. Es wurde jedoch bestätigt, dass tatsächlich alle acht Kanalisierer-DDCs eine deterministische Phase bereitstellen, während auch der MCS-Algorithmus verwendet wird.

Das Ausgeben dieses Algorithmus beim Hochfahren stellt eine deterministische Phase für jeden Kanal her, wenn die Abtasttakte des PLL-Synthesizers und die SYSREFs der Takt-ICs beim Hochfahren dieselbe Phasenbeziehung beibehalten. Jedes System unterliegt jedoch thermischen Gradienten, die zu einer Drift des PLL-Takts führen können und die zu einer anderen Einschaltphase führen kann, wenn sie nicht kompensiert wird. Um die Drift des thermischen Gradienten innerhalb des Systems zu kompensieren, verwendet diese Plattform Phasenanpassungen des PLL-Synthesizers.

Im nächsten Teil dieser Artikelserie werden wir die Phasenanpassungen von PLL-Synthesizern, die Skalierbarkeit auf mehrere Subarrays und Kalibrierungsalgorithmen auf Systemebene untersuchen.

Referenzen

1 Del Jones. „JESD204C Primer:Was ist neu und für Sie drin – Teil 1.“ Analoger Dialog , Bd. 53, Nr. 2, Juni 2019.

2 Del Jones. „JESD204C Primer:Was ist neu und für Sie drin – Teil 2.“ Analoger Dialog , Bd. 53, Nr. 3, Juli 2019.

Eingebettet

- Phasenverschiebung

- AC-Phase

- Phasenrotation

- C# verwenden

- MACOM stellt neuen Verstärker mit extrem niedrigem Phasenrauschen vor

- Keysight bringt neues Phasenrausch-Testsystem auf den Markt

- Die Verwendung mehrerer Inferenzchips erfordert eine sorgfältige Planung

- Generieren einer hochpräzisen Wellenform mit einem DAC und einer benutzerdefinierten Leiterplatte

- Verilog-Taktgenerator

- Eine Mühle als Drehbank verwenden