Robustes und Latch-Up-immunes LVTSCR-Bauelement mit integriertem PMOSFET für ESD-Schutz in einem 28-nm-CMOS-Prozess

Zusammenfassung

Es wird erwartet, dass ein niederspannungsgesteuerter Silizium-gesteuerter Gleichrichter (LVTSCR) einen Schutz vor elektrostatischer Entladung (ESD) für eine integrierte Niederspannungsschaltung bietet. Allerdings ist er aufgrund seiner extrem niedrigen Haltespannung normalerweise anfällig für den Latch-up-Effekt. In diesem Artikel wurde ein neuartiger LVTSCR, der mit einem zusätzlichen p-Typ-MOSFET namens EP-LVTSCR eingebettet ist, in einer 28-nm-CMOS-Technologie vorgeschlagen und verifiziert. Das vorgeschlagene Gerät besitzt eine niedrigere Triggerspannung von ~ 6,2 V und eine deutlich höhere Haltespannung von ~ 5,5 V mit nur 23 % Verschlechterung des Fehlerstroms beim Übertragungsleitungsimpulstest. Es wird auch gezeigt, dass der EP-LVTSCR mit einem niedrigeren Einschaltwiderstand von ~ 1,8 Ω sowie einem zuverlässigen Ableitstrom von ~ 1,8 nA, gemessen bei 3,63 V, arbeitet, wodurch er für ESD-Schutz in 2,5 V/3,3 V CMOS . geeignet ist Prozesse. Darüber hinaus wurden der Auslösemechanismus und die Leitungseigenschaften des vorgeschlagenen Geräts untersucht und mit TCAD-Simulation demonstriert.

Hintergrund

Mit der kontinuierlichen Miniaturisierung der Strukturgröße von Halbleiterbauelementen ist die durch elektrostatische Entladung (ESD) in den integrierten Schaltungen (IC) induzierte Beschädigung zu einem ernsteren Problem geworden. Darüber hinaus sind die Herstellungskosten der ESD-Schutzvorrichtung aufgrund der fortschrittlichen Prozesstechnologie stark gestiegen [1]. Daher sind die Designs von ESD-Schutzgeräten mit hoher Flächeneffizienz und Robustheit von großem Wert.

Es wurde verifiziert, dass ein siliziumgesteuerter Gleichrichter (SCR) aufgrund des starken positiven Rückkopplungseffekts in seinen parasitären Bipolartransistoren einen hohen ESD-Strom bei einer kleinen Geräteabmessung aushält [2]. Aber der SCR hat typischerweise eine hohe Triggerspannung (V t1 ), die die Gate-Oxid-Durchbruchspannung der Eingangsstufe in der nanoskaligen CMOS-Technologie überschreitet. Um das V . zu reduzieren t1 von SCR wurde der modifizierte laterale SCR (MLSCR) für den Eingangs-ESD-Schutz durch Einfügen von stark dotiertem n + . berichtet oder p + Regionen über der Grenze von n-Wanne und p-Wanne [3, 4]. Aber die Triggerspannung des MLSCR ist immer noch größer als die Durchbruchspannungen der Ausgangstransistoren im CMOS-Ausgangspuffer. Daher kann es allein keinen effizienten ESD-Schutz am Ausgang bieten.

Um den CMOS-Ausgangspuffer effizient zu schützen, wurde ein niederspannungsgesteuerter SCR (LVTSCR) vorgeschlagen, indem ein Kurzkanal-NMOS (PMOS)-Bauelement in den herkömmlichen SCR eingefügt wird, um eine viel niedrigere Triggerspannung zu erzielen [5,6,7] , die der Snapback-Triggerspannung des eingefügten NMOS(PMOS)-Bauelements entspricht. Wie die herkömmlichen SCR- und MLSCR-Geräte unterliegt auch der LVTSCR aufgrund seiner extrem niedrigen Haltespannung (Vh ) von etwa 2 V [8]. Ein solcher Latch-up-Effekt führt zu einer Fehlfunktion während des normalen Betriebs und einem unaufhörlich hohen Strom, um den IC zu zerstören [9].

Es gibt mehrere mögliche Methoden, um das V . zu verbessern h des LVTSCR [10,11,12,13,14,15]. Die gängigste Lösung besteht darin, die Basisregion der parasitären Bipolartransistoren (BJT) des SCR zu erweitern, um die Injektionseffizienz ihrer Emitter-Basis-Übergänge zu verringern [10]. Bei dieser Lösung erhöht sich nicht nur der Layoutbereich des Geräts, sondern auch der Einschaltwiderstand (R an ) sollte auch, was zu einer drastischen Verschlechterung seines Fehlerstroms (I t2 ). Dann wurde ein optimiertes Verfahren vorgeschlagen, indem eine Floating-n-Well-Region in LVTSCR mit weniger Opfern bei I . eingefügt wurde t2 [11], arbeitet aber auch mit einem großen R an eine exorbitante Leitungsspannung, die die Gate-Oxid-Durchbruchspannung gegenüber einem kleinen Strom überschreitet, wodurch der effektive ESD-Schutzstrom verringert wird. Die Methode durch Hinzufügen der zusätzlichen N-LDD/P-HALO-Schichten in LVTSCR kann auch das V . erhöhen h [12], während solche Vorrichtungen nur für den spezifischen Prozess kompatibel sind und in gewöhnlichen CMOS-Prozessen nicht weit verbreitet verwendet werden können. Darüber hinaus wurde in [13] über einen Gate-Masse-NMOS-getriggerten LVTSCR (GGSCR) berichtet, der die V . erhöht h B. indem der Drain des eingebetteten NMOS zur Anode geführt wird, jedoch könnte dies dazu führen, dass der eingebettete NMOS beschädigt wird, bevor der SCR bei einem niedrigen Strom leitet. Kürzlich haben die zusammengesetzten LVTSCR-Strukturen niedrige V t1 sowie hohes V h wurden in [14, 15] nachgewiesen. Diese Verbundstrukturen werden mit hohem Komplexitäts- und Flächenbedarf entworfen, wodurch ihre Anwendung in der fortschrittlichen CMOS-Technologie unter Berücksichtigung der Designkosten eingeschränkt wird. Daher ist ein robustes, flächeneffizientes und gegen Latch-up-immunes ESD-Schutzgerät für den fortschrittlichen ESD-Prozessschutz sehr wünschenswert.

In diesem Papier wird eine neuartige LVTSCR-Struktur mit einem eingebetteten PMOS-Transistor (EP-LVTSCR) für 2,5 V/3,3 V-Versorgungsspannungsanwendungen vorgeschlagen. Das vorgeschlagene Bauelement wurde in einem 28-nm-CMOS-Prozess hergestellt und seine elektrischen Eigenschaften werden durch die Messung von Transmission Line Pulse (TLP) verifiziert. Die physikalischen Mechanismen des vorgeschlagenen Geräts werden durch technologische Computer-Aided-Design (TCAD)-Simulationen untersucht. Als Ergebnis besitzt die vorgeschlagene Struktur eine höhere Haltespannung, eine niedrigere Triggerspannung mit einem niedrigeren R an , und nur ein leichter Rückgang von I t2 ohne zusätzlichen Prozessschritt.

Methoden

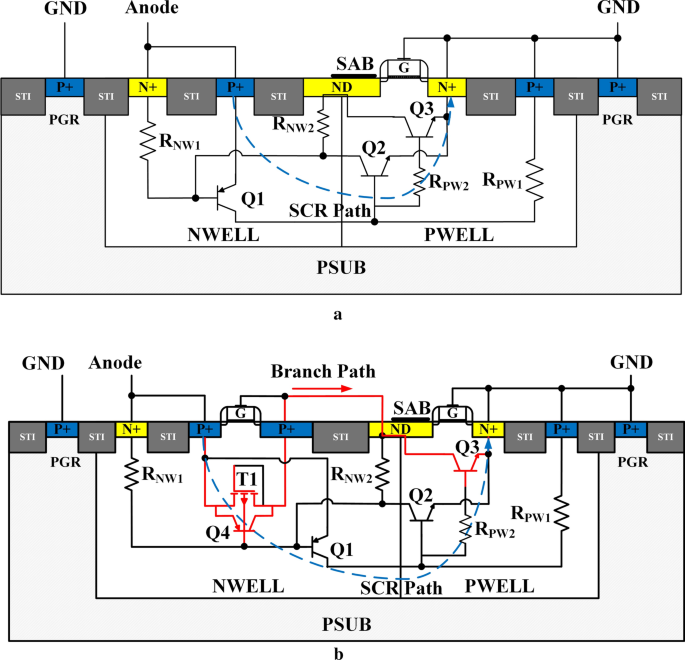

Die konventionelle LVTSCR und die vorgeschlagene EP-LVTSCR wurden in dieser Arbeit untersucht. Die schematischen Querschnittsansichten des herkömmlichen LVTSCR und des EP-LVTSCR sind in Fig. 1a bzw. b gezeigt, während ihre Ersatzschaltungen innerhalb der Strukturen mit den parasitären Transistoren und Wannenwiderständen abgebildet sind. In beiden Geräten werden Silizidblockschichten (SAB) auf der Oberseite des partiellen ND-Bereichs platziert, die Ballastwiderstände induzieren, indem sie die Bildung von Silizidschichten verhindern [16, 17]. Beim herkömmlichen LVTSCR wird ein NMOS-Transistor in PWELL eingefügt, wobei seine Drain-(ND)-Einstellung über NWELL und PWELL liegt, während seine Source und sein Gate zusammen mit Masse (GND) verbunden sind, was in Fig. 1a zu sehen ist. Während der ESD-Belastung werden der parasitäre seitliche p-n-p-BJT (Q1) und die parasitären seitlichen n-p-n-BJTs (Q2 und Q3) allmählich eingeschaltet. In einem solchen Zustand sind die Transistoren Q1 und Q2 gekoppelt, um den SCR-Leitungspfad zu bilden, der die Stromentladung überwiegt, wobei der SCR-Leitungspfad durch die gestrichelte Linie angezeigt wird

Querschnittsansicht von a die konventionelle LVTSCR und b die vorgeschlagene EP-LVTSCR

Im Vergleich zum herkömmlichen LVTSCR weist EP-LVTSCR einen zusätzlichen PMOS-Transistor (T1) auf, der in die NWELL eingebettet ist, da sein Gate und sein Drain mit einem Metall mit ND verbunden sind, was in Fig. 1b gezeigt ist. Wenn ein ESD-Impuls an die Anode des EP-LVTSCR angelegt wird, leitet die in Sperrrichtung vorgespannte N+/NWELL/N+/PWELL/P+-Diode zuerst, wenn die Zapping-Spannung höher als die N+/PWELL-Durchbruchspannung ist. Dann fließen die Löcher/Elektronen, die durch den Lawinenvervielfachereffekt erzeugt werden, zur Kathode/Anode, wodurch die Stromdichte im NWELL/PWELL erhöht wird und das Abfallpotential über dem NWELL/PWELL weiter erhöht wird. Sobald der Gesamtspannungsabfall auf R NW1 und R NW2 , was dem Spannungsabfall zwischen Source und Gate entspricht (− V gs ) von T1 überschreitet seine Schwellenspannung (V te ) von etwa 0,9 V wird der T1 eingeschaltet. Anschließend werden die parasitären lateralen n-p-n-Transistoren Q2 und Q3 abhängig von der Leitfähigkeit ihrer Emitter-Basis-Übergänge getriggert. Es ist zu beachten, dass das Leiten von T1 den R . senkt an über NWELL, und somit können Q2 und Q3 bei niedrigeren Spannungen getriggert werden. Wenn der Strom weiter ansteigt, sinkt der Spannungsabfall an R NW1 steigt auf etwa 0,7 V an und schaltet Q1 und den parasitären lateralen p-n-p-Transistor des PMOS (Q4) ein. Schließlich schaltet sich der SCR-Pfad gegen den leitenden Zweigpfad ein.

Mehrere Berichte zeigten, dass die Haltespannung von SCR hauptsächlich durch die Potenzialdifferenz über die NWELL/PWELL-Verarmungsregion V . bestimmt wird ab [18,19,20], das umgekehrt proportional zu den in die Verarmungsregion injizierten Minoritätsträgern (Elektronen/Löchern) ist. Während der Verzweigungspfad von EP-LVTSCR Löcher/Elektronen, die in die Verarmungsregion injiziert wurden, aus dem SCR-Pfad extrahieren kann, wodurch der V . erhöht wird h von EP-LVTSCR.

Um den physikalischen Mechanismus von EP-LVTSCR weiter zu demonstrieren, wurde eine TCAD-Simulation durchgeführt, bei der die physikalischen Modelle wie Mobilität, Rekombination, Thermodynamik und effektive intrinsische Dichte integriert wurden und die mathematischen Methoden wie Extrapolation, RelErrcontrol und Gleichstrom integriert wurden Berechnung verwendet wurden. Die ESD-Strommodellierung durch 1,2-A-Pulse mit 10 ns Anstiegszeit wurde auf die Anoden von EP-LVTSCR bzw. des konventionellen LVTSCR angewendet, wobei das Substrat der Bauelemente als einzige Wärmesenke betrachtet wurde und die Umgebungstemperatur auf 300 . eingestellt wurde K.

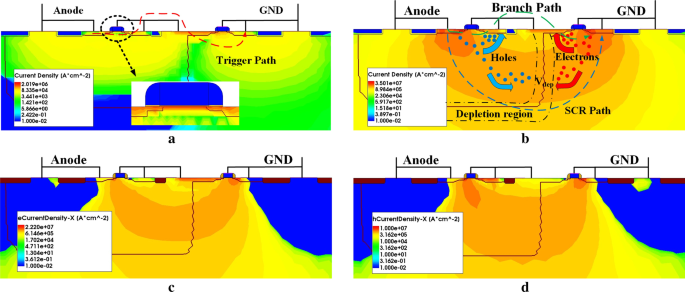

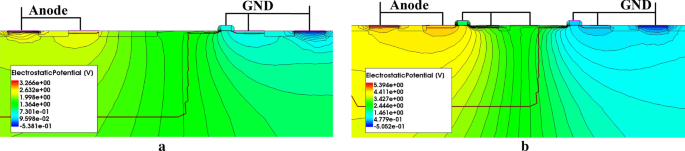

Die simulierten Ergebnisse der Gesamtstromdichteverteilungen von EP-LVTSCR bei 500 ps und 5 ns sind in Abb. 2a bzw. b gezeigt. Bei 500 ps konzentriert sich die Stromdichteverteilung auf die Transistoren T1 und Q2, was anzeigt, dass die Reihen T1/Q2 als Triggerpfad eingeschaltet wurden, wie in Fig. 2a gezeigt. Wenn die Zeit auf 5 ns ansteigt, haben sowohl der SCR-Pfad als auch der Verzweigungspfad geleitet, wie in Fig. 2b zu sehen ist. Zu diesem Zeitpunkt wird ein Teil der Löcher/Elektronen, die durch P+/N+ erzeugt werden, aus NWELL/PWELL extrahiert, um durch den Verzweigungspfad zu fließen, was durch die horizontalen Löcher und die Elektronenstromdichte der in Fig. 2c, d . gezeigten vorgeschlagenen Struktur veranschaulicht wird . Darüber hinaus werden die elektrostatischen Potenzialverteilungen des herkömmlichen LVTSCR und des EP-LVTSCR bei 5 ns in Fig. 3a, b verglichen. Offensichtlich ist der potentielle Peak innerhalb des EP-LVTSCR höher. Diese Simulationsergebnisse liefern einen direkten Beweis für die obige Annahme der höheren Haltespannung von EP-LVTSCR, die sich aus dem in Abb. 1b gezeigten Verzweigungspfad ergibt.

TCAD-simuliert a Gesamtstromdichteverteilung bei t = 500 ps, b Gesamtstromdichteverteilung bei 5 ns, c horizontale Elektronenstromdichteverteilung bei 5 ns und d Stromdichteverteilung der horizontalen Löcher bei 5 ns des vorgeschlagenen EP-LVTSCR unter einer 1,2A-TLP-Belastung

TCAD-simulierte elektrostatische Potentialverteilungen von a die vorgeschlagene EP-LVTSCR und b die konventionelle LVTSCR bei t = 5 ns unter einer 1,2A-TLP-Belastung

Ergebnisse und Diskussion

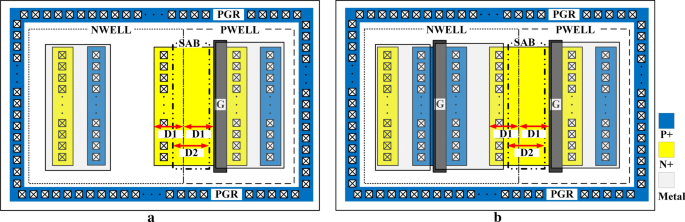

Der herkömmliche LVTSCR und EP-LVTSCR werden in einem 28-nm-2,5 V/3,3 V-Logik-CMOS-Prozess mit der gleichen Breite von 40 um implementiert, und ihre Layouttopologien sind in Fig. 4a bzw. b gezeigt. Um die mit dem Substrat verbundenen parasitären Effekte zu vermeiden, werden in beiden Strukturen P-Typ-Schutzringe (PGR) verwendet, und jeder PGR ist mit GND verbunden [21]. Die zentrale Achse von ND ist auf die NWELL/PWELL-Verbindung ausgerichtet, und der Parameter D1 wird verwendet, um die Hälfte der ND-Länge zu beschreiben, während D2 die Länge der SAB-Region ist.

Layouttopologien von a die konventionelle LVTSCR und b die vorgeschlagene EP-LVTSCR

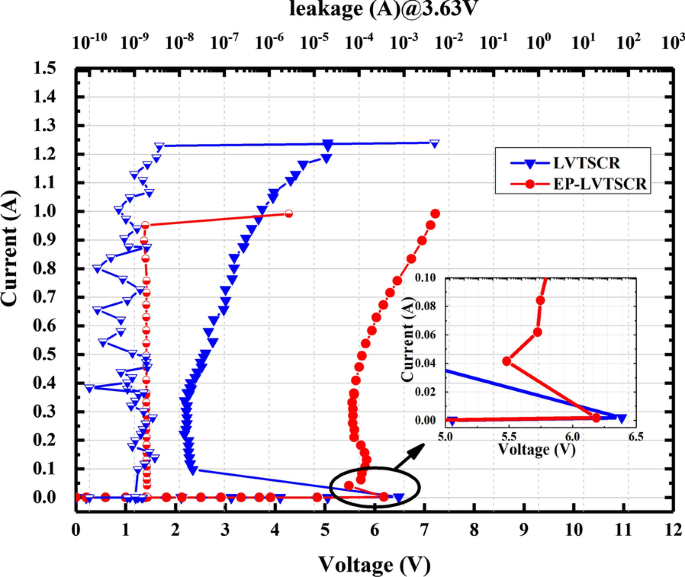

Die ESD-Eigenschaften des herkömmlichen LVTSCR und EP-LVTSCR wurden mit dem Hanwa TED-T5000 TLP-Tester mit 10 ns Anstiegszeit und 100 ns Pulsbreite gemessen, und die Leckströme wurden jeweils unter 3,63 V (1,1 * VDD) Gleichspannungsvorspannung gemessen TLP-Stress. Die gemessenen TLP I–V und Leckeigenschaften des EP-LVTSCR und LVTSCR sind in Abb. 5 dargestellt. Offenbar besitzt der EP-LVTSCR ein höheres V h von 5,49 V im Vergleich zum herkömmlichen LVTSCR von 2,18 V. Obwohl der EP-LVTSCR eine deutliche Verbesserung der Haltespannung aufweist, ist sein I t2 gerade um etwa 0,29 A verringert, was vom Assistenten des Zweigstrompfads profitiert. Außerdem führt EP-LVTSCR auch ein V . durch t1 von 6,49 auf 6,18 V abnehmend. Für 2,5 V- oder 3,3 V-IO-Pins in 28-nm-CMOS-Prozessen reichte das ESD-Designfenster von 3,63 bis 9,4 V mit einer Sicherheitsmarge von 10 %. Daher kann das vorgeschlagene EP-LVTSCR als gültige ESD-Schutzlösung für 2,5 V/3,3 V-IO-Ports verwendet werden, indem das Latch-up-Problem in einer traditionellen LVTSCR-Struktur überwunden wird.

Gemessene TLP I–V und Leckströme von EP-LVTSCR und dem konventionellen LVTSCR mit gleicher Chipfläche

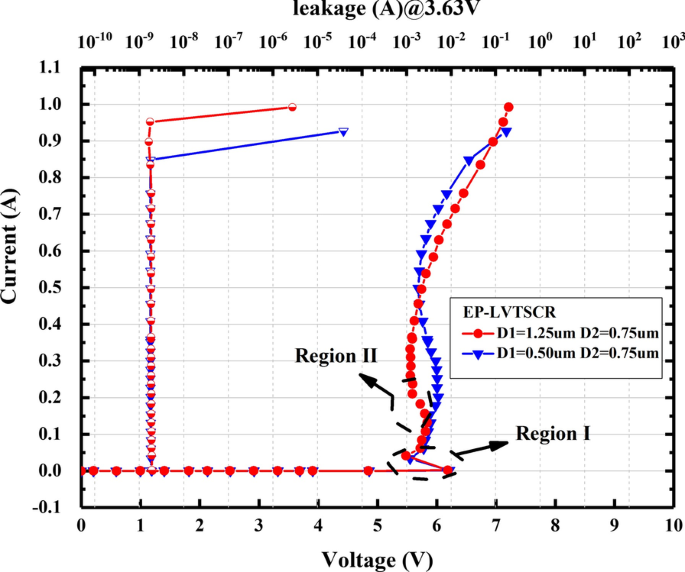

In diesem Artikel wurden die elektrischen Eigenschaften des vorgeschlagenen ESD-Schutzes durch Modifizieren der Designvariablen D1 und D2 optimiert. Abbildung 6 veranschaulicht die TLP-Messergebnisse von EP-LVTSCRs mit zwei verschiedenen D1. Es ist zu beachten, dass die I-V-Kurven von EP-LVTSCRs aufgrund der Multitrigger-Effekte beim Einschalten der Geräte zwei Snapback-Bereiche aufweisen. Der erste Snapback-Bereich I deutet die Leitung des Triggerpfads an, der in Fig. 2a angezeigt ist, während der zweite Snapback von Bereich II durch das Einschalten des SCR-Pfads induziert wird. Wenn D1 von 1,25 auf 0,5 um sinkt, wird das I t2 sinkt um etwa 0,1 A und der Haltestrom im zweiten Snapback wird um etwa 0,17 A erhöht. Dies liegt daran, dass die Wannenwiderstände R NW2 und R PW2 (Abb. 1) werden mit der D1-Verringerung verringert, wodurch mehr Strom benötigt wird, um die Leitung von SCR auszulösen und aufrechtzuerhalten.

Gemessene TLP I–V und Leckströme von EP-LVTSCR mit zwei verschiedenen D1

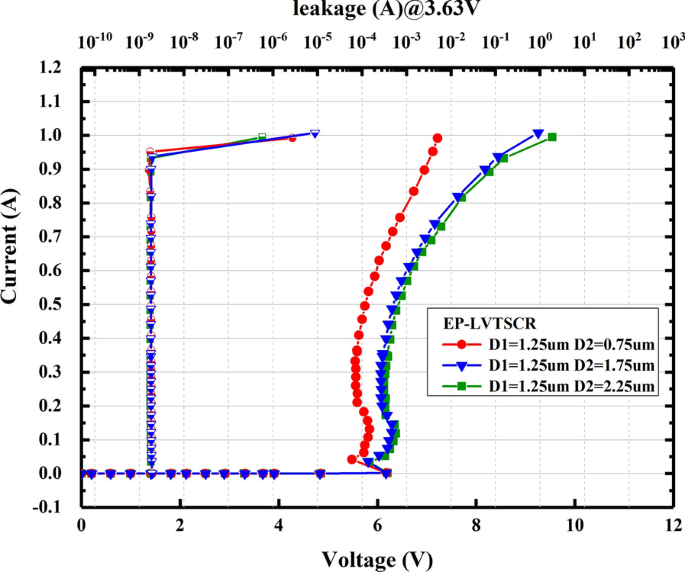

Abbildung 7 zeigt die TLP I–V-Ergebnisse von EP-LVTSCR mit drei verschiedenen D2. Wenn D2 von 0,75 auf 2,25 µm ansteigt, steigt der Ballastwiderstand von ND allmählich an, was zu einer Erhöhung des Widerstands des Zweigpfads und einer weiteren Vergrößerung von R . führt an , die durch die Steigungsänderungen der IV-Kennlinien in Abb. 7 beobachtet werden können. Als Ergebnis ist die V h steigt von 5,5 auf 5,8 V mit dem Anstieg von D2 und ohne signifikante Änderungen von It2 .

Gemessene TLP I–V und Leckströme von EP-LVTSCR mit drei verschiedenen D2

Schlussfolgerungen

Ein verbessertes ESD-Bauelement namens EP-LVTSCR wurde in einer 28-nm-CMOS-Technologie entwickelt und hergestellt. Die Mechanismen der vorgeschlagenen Geräte wurden auch mit TCAD-Simulationen demonstriert. Im Vergleich zum herkömmlichen LVTSCR besitzt der vorgeschlagene EP-LVTSCR aufgrund seines verbesserten Triggermechanismus und Zweigleitungseffekts eine niedrigere Triggerspannung von 6,2 V und eine deutlich höhere Haltespannung von 5,5 V. Bei solch einem höheren Anstieg von V h , verringerte sich der Fehlerstrom des EP-LVTSCR nur um etwa 20 %. Außerdem arbeitet die vorgeschlagene Struktur mit einem niedrigeren Einschaltwiderstand sowie einem zuverlässigen Leckstrom von etwa 2 nA bei einer Spannung von 3,63 V, sodass sie sich hervorragend zum Schutz von 2,5 V/3,3 V-I/O-Pins eignet. Darüber hinaus wird erwartet, dass die EP-LVTSCRs auch einen ESD-Schutz für 5-V-Stromkreise bieten, da sie von ihren einstellbaren Haltespannungseigenschaften profitieren.

Verfügbarkeit von Daten und Materialien

Alle während dieser Studie generierten oder analysierten Daten sind in diesem veröffentlichten Artikel enthalten.

Abkürzungen

- ESD:

-

Elektrostatische Entladung

- SCR:

-

Siliziumgesteuerter Gleichrichter

- MLSCR:

-

Modifiziertes seitliches SCR

- LVTSCR:

-

Niederspannungs-getriggerter SCR

- CMOS:

-

Komplementärer Metalloxid-Halbleiter

- IC:

-

Integrierte Schaltungen

- V t1 :

-

Triggerspannung

- V h :

-

Haltespannung

- BJT:

-

Bipolartransistoren

- R an :

-

Einschaltwiderstand

- I t2 :

-

Fehlerstrom

- TLP:

-

Übertragungsleitungsimpuls

- TCAD:

-

Technologie computergestütztes Design

- SAB:

-

Silizidblock

- V te :

-

Schwellenspannung

- DC:

-

Gleichstrom

Nanomaterialien

- Ein Überblick über die IC-Technologie für Mikrocontroller und eingebettete Systeme

- Maxime:dualer IO-Link-Transceiver mit DC-DC-Regler und Überspannungsschutz

- Embedded Design mit FPGAs:Entwicklungsprozess

- TRS-STAR:robuste und lüfterlose Embedded-Systeme von avalue

- Tauchbeschichtungsverfahren und Leistungsoptimierung für elektrochrome Drei-Zustands-Bauelemente

- Ein RRAM-integrierter 4T SRAM mit selbsthemmender ohmscher Schaltlast durch reinen CMOS-Logikprozess

- Eine neuartige Nanocone-Cluster-Mikrostruktur mit Antireflexions- und superhydrophoben Eigenschaften für Photovoltaikanlagen

- Multifunktionales Gerät mit schaltbaren Funktionen der Absorption und Polarisationsumwandlung im Terahertz-Bereich

- Automatisierung und Cybersicherheit:Rundumschutz für Kunden

- PCB-Materialien und Design für Hochspannung