Ein RRAM-integrierter 4T SRAM mit selbsthemmender ohmscher Schaltlast durch reinen CMOS-Logikprozess

Zusammenfassung

Dieses Papier berichtet über einen neuartigen, volllogikkompatiblen 4T2R nichtflüchtigen statischen Direktzugriffsspeicher (nv-SRAM) mit seinem selbstsperrenden Datenspeichermechanismus für SRAM-Anwendungen mit niedrigem Stromverbrauch und hoher Geschwindigkeit. Mit kompakter Zellenfläche und voller Logikkompatibilität enthält dieses neue nv-SRAM zwei STI-ReRAMs, die in das 4T SRAM eingebettet sind. Daten können über eine flüchtige Struktur mit Kreuzkopplung gelesen/geschrieben werden, um eine schnelle Zugriffsgeschwindigkeit aufrechtzuerhalten. Daten können in einer neuen SRAM-Zelle durch eine einzigartige Selbstsperroperation auf der Last des resistiven Direktzugriffsspeichers (RRAM) nichtflüchtig gespeichert werden, wodurch während des Datenhaltens keine statische Leistung erreicht wird.

Hintergrund

In den letzten Jahren wurden verschiedene statische Speicher mit wahlfreiem Zugriff mit geringem Stromverbrauch entwickelt, um den Bedarf in Computersystemen auf tragbaren Geräten und IOT-Anwendungen zu decken [1, 2, 3, 4, 5, 6]. Wenn die CMOS-Technologie auf den Nanometerbereich herunterskaliert wird, steigt der Leckstrom im Sperrzustand drastisch an, was zu einer Verschlechterung des statischen Stromverbrauchs für flüchtige Speichermodule führt [7, 8]. Der durch den Leckstrom in nanoskaligen Transistoren erhöhte statische Stromverbrauch ist zu einer der Hauptherausforderungen für die Weiterentwicklung von SRAMs mit geringem Stromverbrauch geworden. [9,10,11]. Im Laufe der Jahre wurden verschiedene Zellstrukturen oder Betriebstechniken [12,13,14,15,16] vorgeschlagen, um den Stromverbrauch in SRAMs zu minimieren. Einige der neu vorgeschlagenen Zellen enthalten nichtflüchtige Speicherelemente, wie z. B. einen resistiven Direktzugriffsspeicher (RRAM) und einen magnetoresistiven Direktzugriffsspeicher (MRAM) [17,18,19,20], um eine Null-Halteleistung bei gleichzeitig niedrigem Betrieb zu erreichen Leistung und schnelle Zugriffsgeschwindigkeit bei der Verarbeitung flüchtiger Daten. Das Hinzufügen nichtflüchtiger Speicherelemente zu logikbasierten SRAM-Arrays erfordert jedoch im Allgemeinen zusätzliche Schichten und/oder Prozesse zu den Standardlogikplattformen [21, 22, 23]. Dies wird die Prozesskomplexität ihrer Entwicklung unvermeidlich erhöhen. Außerdem erfordern diese Back-End-basierten RRAMs und MRAMs eine große Verbindungsstruktur, die aus mehreren Stapeln von Durchkontaktierungen und Metallen zu den SRAM-Zellen besteht. Diese Überbrückungsstrukturen erhöhen die parasitäre Kapazität zum SRAM-Datenspeicherknoten, was die Zugriffsgeschwindigkeit dieser nichtflüchtigen SRAM-Zellen beeinflusst [24, 25]. In unserer früheren Arbeit [26] wurde zuerst ein neuer 4T nv-SRAM mit null statischer Leistung mit STI-Seitenwand-RRAMs vorgeschlagen, die sich neben den schwebenden Speicherknoten des 4T-SRAMs befinden. In diesem Schreiben wird dieser 4T2R nv-SRAM mit nichtflüchtiger Datenspeicherung, Null-Halteleistung und schneller Zugriffsgeschwindigkeit weiter analysiert und für eingebettete NVM-Anwendungen optimiert.

Methoden

STI-ReRAM-Zellenstruktur

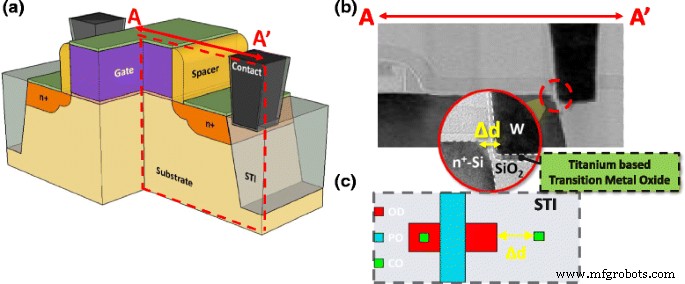

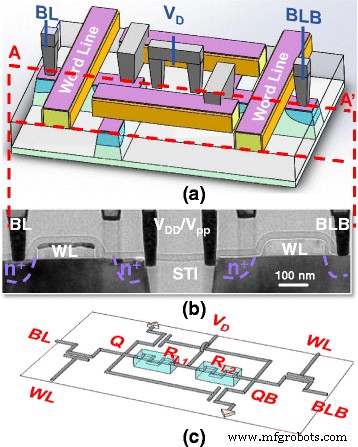

In der 3D-STI-RRAM-Struktur in Fig. 1a besteht der Widerstandsspeicherknoten aus einem Übergangsmetalloxid (TMO) zwischen zwei Elektroden, dem N+-Gebiet und einem Wolframpfropfen auf der linken bzw. rechten Seite. Wie im TEM-Bild in Fig. 1b und im Layout in Fig. 1c gezeigt, wird durch Anordnen des Kontakts auf der STI-Region mit dem richtigen Abstand zur N+-Region das verbleibende SiO2 und die Sperrschicht unter dem Wolframstecker werden zu einem TMO-Film und weisen die ohmsche Schaltqualität auf.

a 3D-Darstellung einer 1T1R-Zelle mit STI-ReRAM direkt neben dem n+-Übergang. b Das entsprechende TEM-Bild eines resistiven Speicherknotens aus Übergangsmetalloxiden, gebildet zwischen einem speziell platzierten Kontakt und dem n+-Gebiet des Auswahltransistors. c Layout

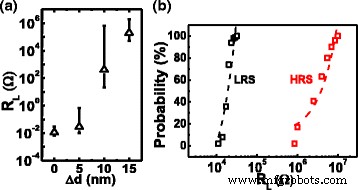

Die TMO-Dicke kann gesteuert werden, indem ein geeigneter Abstand Δd zwischen einem Kontakt und dem N+-Diffusionsbereich gewählt wird. Basierend auf der Messung in Fig. 2a besteht eine positive Korrelation zwischen dem anfänglichen Widerstandsniveau und dem gezogenen Abstand Δd, bestimmt durch die Masken, die STI bzw. Kontaktbereiche definieren. Für die folgende Studie wird RRAM mit Δd gleich 10 nm wegen seiner niedrigeren Formungsspannung und vorzugsweise RL . gewählt Verteilung sowohl im niederohmigen Zustand (LRS) als auch im hochohmigen Zustand (HRS), wie in Abb. 2b zusammengefasst. Mit der richtigen Wortleitungs-(WL)-Spannungssteuerung während der Setz-/Bildungsoperationen kann der Setzstrom lokal durch den Auswahltransistor geklemmt werden, was eine bessere Dauerleistung ermöglicht.

a Der gemessene Anfangswiderstand von STI-RRAM-Proben mit unterschiedlichem △d. b Kumulative Wahrscheinlichkeit des Ladewiderstands nach Reset/Setzen des STI-RRAM sowohl im hoch- als auch im niederohmigen Zustand

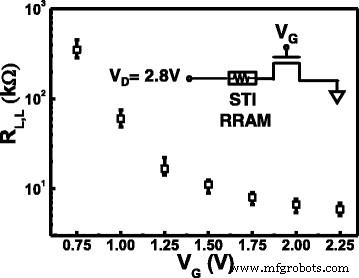

Die Daten in Fig. 3 zeigen ferner, dass der Lesestrompegel in LRS gut durch die Gatespannung VG . gesteuert werden kann . Beim Umformen bei VD = 2,8 V, begrenzt der Auswahltransistor den maximalen Strom, der durch das STI-RRAM fließt, nachdem das Gerät auf LRS gesetzt wurde. Der nachfolgende LRS-Zustandswiderstandspegel ist umgekehrt proportional zum lokal geklemmten Strom, der in verschiedenen TaO-basierten RRAM-Bauelementen gefunden wurde [27, 28].

Korrelation zwischen den Belastungswiderstandsstufen, RL,L , und die angelegte Gatespannung während des Setzens. Daten deuten darauf hin, dass unterschiedliche RL,L kann durch Einstellen eines anderen Pegels der Select-Gate-Spannung erhalten werden

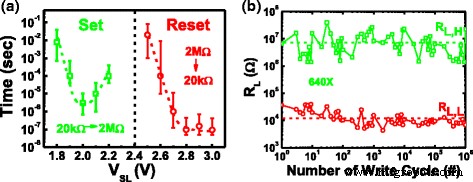

Um die Widerstandsschalteigenschaften von STI-RRAM sicherzustellen, werden die Zeit bis zum Setzen und die Zeit bis zum Zurücksetzen getestet, wie in Fig. 4a gezeigt. Set- und Reset-Operationen können optimiert werden, wenn VSL = 2 bzw. 2,8 V. Der RRAM-Dauertest ist in Abb. 4b zusammengefasst. Durch die Verwendung eines inkrementellen Schrittimpulsprogrammierungsalgorithmus kann das Lesefenster nach 1 Million Zyklen stabil bleiben.

a Zusammengefasste Zeit bis zum Einstellen und Zeit bis zum Zurücksetzen im Vergleich zu VPP . b Ergebnis des Dauertests von einer Million Zyklen des STI-RRAM unter Verwendung des inkrementellen Schrittpulsprogrammierungsalgorithmus

Nichtflüchtiges SRAM-Konzept

Die 3D-Darstellung in Abb. 5 zeigt die neu vorgeschlagene 4T2R-nv-SRAM-Zellenstruktur und ihr entsprechendes TEM-Querschnittsbild entlang der Schnittlinie AA’. Zwei STI-RRAMs dienen sowohl als nichtflüchtige Speicherknoten als auch als Lastwiderstände, die zwischen den Q- und QB-N+-Diffusionsbereichen und einem Kontakt mit geeignetem Abstandsdesign eng auf den STI-Kanten gelandet sind. Das TEM-Bild zeigt einen wohlgeformten STI-RRAM sowohl auf der linken als auch auf der rechten Seite des Isolationsbereichs und führt zu einer ziemlich kompakten Zelle mit diesen eng platzierten nichtflüchtigen Speicherknoten auf dem gleichen Niveau der Transistoren.

a 3D-Darstellung der vorgeschlagenen 4T2R-nv-SRAM-Zellenstruktur und der b entsprechendes TEM-Querschnittsbild. c Das Schaltbild einer SRAM-Zelle ist mit zwei RRAM-Widerständen als Ladevorrichtungen gezeigt

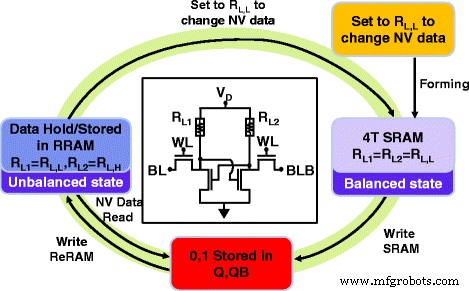

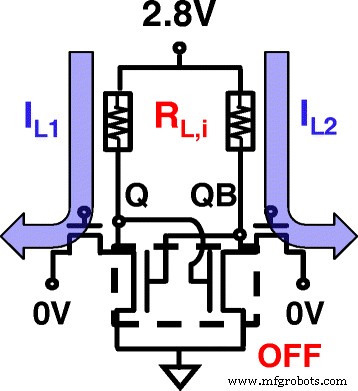

Der vorgeschlagene 4T nv-SRAM kann im flüchtigen und im nichtflüchtigen Modus betrieben werden. Seine vier verschiedenen Zustände und sein Betriebsschema sind in Abb. 6 dargestellt.

Schaltplan einer nv-SRAM-Zelle und ihr entsprechendes Flussdiagramm zum Umschalten zwischen flüchtigen und nichtflüchtigen SRAM-Operationen

In seinen Anfangszuständen hat STI-RRAM normalerweise einen Widerstandswert von 10 8 Ω, während der TMO-Film intakt ist. Durch einen Blanket-Forming-Vorgang können die nv-SRAM-Zellen gleichzeitig blockweise bei VD . initialisiert werden = 2,8 V. Beide RL1 und RL2 (Lastwiderstand links bzw. rechts) werden auf RL,L . initialisiert . Das letzte RL,L Der Pegel von 20~370 kΩ kann durch Anlegen einer anderen WL-Spannung während des Umformvorgangs gesteuert werden. Die Zelle erreicht dann einen Gleichgewichtszustand, was bedeutet, dass sich die beiden Ladewiderstände im gleichen Zustand befinden. In diesem Zustand kann diese Zelle nun als typischer 4T2R-SRAM fungieren und flüchtige Daten auf herkömmliche Weise verarbeiten, indem sie Daten im kreuzgekoppelten Latch speichert.

Um die Daten nichtflüchtig zu speichern, können die komplementären zwischengespeicherten Daten auf den RRAMs durch einen Selbstsperrmechanismus gespeichert werden, der in dieser Zelle vererbt wird. Wenn die Daten erfolgreich im RRAM-Paar gespeichert wurden, kann man die Versorgungsspannung zum dauerhaften Datenhalten abschalten. Um auf den gespeicherten Zustand zuzugreifen, wenden Sie einfach VDD . erneut an zum Array. Die nichtflüchtigen Daten werden automatisch in den Q- und QB-Knoten wiederhergestellt und können über den herkömmlichen SRAM-Lesemodus abgerufen werden. Um die nichtflüchtigen Daten aufzufrischen, wird schließlich eine Blanket-Set-Operation auf die SRAM-Arrays angewendet, so dass die Array in ihre Gleichgewichtszustände zurückkehrt.

Ergebnisse und Diskussion

Elektrische Analyse

Die Betriebsbedingungen für Übergänge zwischen verschiedenen Stufen sind in Tabelle 1 zusammengefasst.

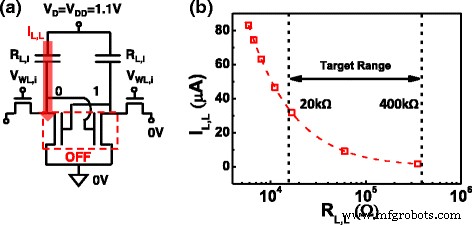

Verschiedene RL,L Der Pegel kann durch Einstellen einer anderen WL-Spannung während der Initialisierung eines Blocks oder Arrays erhalten werden. Unter Berücksichtigung der Stabilität und Betriebsspannung beträgt der RL,L In dieser Studie wird zunächst ein Pegel zwischen 20 und 400 kΩ untersucht. Bei entsprechender WL-Spannung von 0,75 bis 1,25 V verringert sich der resultierende Lastwiderstand relativ linear, wie in Abb. 3 gezeigt. Erwartungsgemäß niedrigeres RL,L Pegel führt zu einem höheren Standby-Strom, siehe Abb. 7. RL,L muss niedrig genug bleiben, um ein großes Datenfenster zwischen den beiden Widerstandszuständen zu vergrößern. Für die weitere Optimierung des angestrebten RL,L . müssen sowohl statische als auch dynamische und nichtflüchtige Datenfenster berücksichtigt werden , die durch die Initialisierungsbedingung gesetzt wird.

a 4T2R SRAM-Zelle im Haltezustand. b Wie erwartet, Belastungswiderstand, IL,L während des Haltens kann effektiv gesenkt werden, indem ein höheres RL,L . gewählt wird

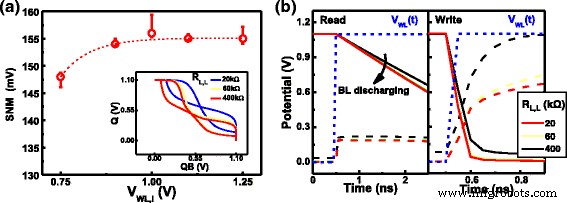

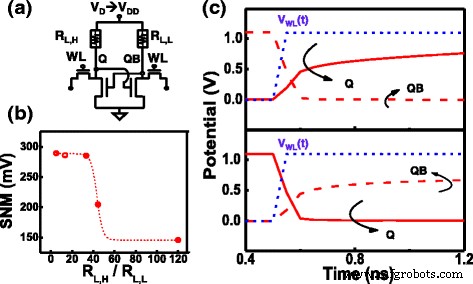

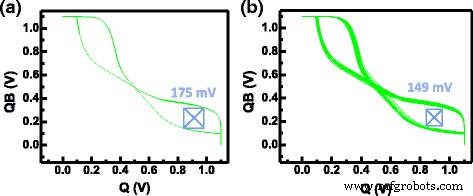

Zunächst wird die statische und dynamische Charakterisierung des nv-SRAM im Gleichgewichtszustand untersucht, wobei Zellen betrachtet werden, die durch verschiedene Bedingungen initialisiert wurden. In Fig. 8 ist der statische Rauschabstand (SNM), der durch die mehreren Schmetterlingskurven von Zellen erhalten wird, die durch unterschiedliche WL-Spannungen initialisiert wurden, dargestellt. Die Daten zeigen, dass RL,L Pegel hat minimale Auswirkungen auf die Lesemarge von symmetrischen Zellen, wenn die Ladewiderstände innerhalb des Zielbereichs liegen. Die SNM-Verteilung mehrerer Zellen in den Gleichgewichtszuständen unter verschiedenen Initialisierungsbedingungen ist in 8a zusammengefasst. Insgesamt bleiben SNMs von Zelle zu Zelle ziemlich stabil, während bei einer WL-Spannung von weniger als VDD . ein vernünftiger Lesespielraum erreicht werden kann , was für Anwendungen mit geringer Leistung von Vorteil sein kann. Um die dynamischen Lese- und Schreibeigenschaften dieser Zelle im symmetrischen Zustand zu untersuchen, ist das Einschwingverhalten beim Schreiben von „1“ und „0“ in 8b zusammengefasst. Es zeigt sich, dass höhere RL,L reduziert die Pull-up-Geschwindigkeit zu den Q-, QB-Knoten, was die Übergangszeit sowohl bei Lese- als auch bei Schreibvorgängen leicht erhöhen kann. Die Reaktionsgeschwindigkeit liegt jedoch noch im erwarteten Bereich. Die obigen Daten legen nahe, dass dieser 4T2R nv-SRAM im Gleichgewichtszustand flüchtige Daten wie herkömmliche SRAMs verarbeiten kann.

a Der statische Leseabstand (SNM) der vorgeschlagenen SRAM-Zellen mit unterschiedlicher WL-Spannung während der Initialisierung. Angemessenes SNM kann innerhalb eines ziemlich großen Bereichs von RL,L . aufrechterhalten werden von 20~400 kΩ. b Dynamische Lese- und Schreibeigenschaften einer Zelle unter Ausgleichslastbedingungen zeigen eine gute Reaktionszeit innerhalb von Nanosekunden. Höheres RL,L reduziert leicht die Pullup-Geschwindigkeit während des Schreibvorgangs

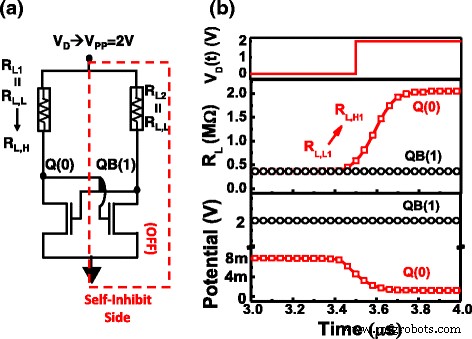

Um Daten im STI-RRAM-Paar zu speichern, ermöglicht diese Zelle ein selbstselektives Zurücksetzen von nur einem der RRAMs im Ladewiderstandspaar, wodurch die Daten durch Anlegen eines höheren Vpp Spannung an den Versorgungsknoten des Zellenblocks gleichmäßig. Sobald die Latch-Daten im Q- und QB-Knoten gespeichert sind, wird ein nichtflüchtiges Schreiben durch den Selbstsperrmechanismus in der Kreuzkopplungsstruktur mit RRAM erreicht, wie in Fig. 9a gezeigt. Nur eine Seite des RRAM mit niedriger Spannung am Q-Knoten wird auf RL,H . zurückgesetzt . Der Strom im anderen Zweig ist fast Null, da der Pull-Down-Transistor durch das niedrige VQ . ausgeschaltet wird .

a Illustration des Selbstsperrmechanismus während des Schreibens von nichtflüchtigen Daten durch Zurücksetzen einer Seite von zwei RRAMs. b Dynamische Änderung von RL und Q, QB Potential verifizieren Selbstsperrung des Schreibens von Latch-Daten in RRAMs

Daten werden im RRAM-Paar als VPP . gespeichert Impuls wird an den Versorgungsknoten angelegt. Beim Schreiben nichtflüchtiger Daten wird das dynamische Umschalten von RL und die Übergangsantwort des Q-, QB-Potentials sind in Fig. 9b zusammengefasst. Messdaten legten nahe, dass zum erfolgreichen Zurücksetzen des STI-RRAM auf einer Seite ein Impuls von 300 ns bei Vpp . erforderlich ist = 2 V ist ausreichend. Um sicherzustellen, dass der flüchtige Betrieb immer noch unbeeinflusst bleibt, wenn sich die Zellen im unausgeglichenen Zustand befinden, wie in 10a gezeigt, ist die SNM-Verteilung von Zellen mit unterschiedlichen RL,H /RL,L Verhältnis sind in Abb. 10b zusammengefasst. Es hat sich herausgestellt, dass das niedrige Widerstandsverhältnis zwischen den Zuständen den Halte-SNM nicht verschlechtert. Um sicherzustellen, dass eine Zelle eine unausgeglichene Last aufweist, wird das dynamische Schreiben von Daten in eine solche Zelle charakterisiert. Die Daten zeigen, dass beide Zustände erfolgreich geschrieben werden können, wobei das anfängliche Unsymmetrie-Widerstandsverhältnis von 2 M/400 k überwunden wird, wie in Abb. 10c gezeigt.

a Kreuzkupplungsstruktur bei Schieflast. b Statischer Rauschabstand bei unterschiedlichen WL-Spannungen während der Initialisierung. c Dynamisches Schreiben für zwei verschiedene Datenzustände. Unwucht RL,L = 400 kΩ kann auch geschrieben werden

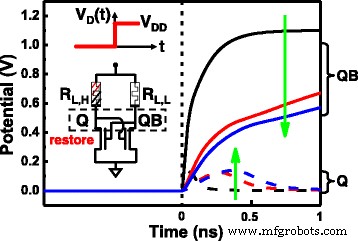

Um die zuvor im RRAM gespeicherten flüchtigen Daten wieder zu laden, kann man einfach VDD . anwenden an den Stromversorgungsknoten wird die unausgeglichene Belastung in den RRAMs selbst an den Latch-Knoten von Q und QB wiederhergestellt, wie in Fig. 11 dargestellt

Wiederherstellung der in Q und QB gespeicherten nichtflüchtigen Daten aus einem unausgeglichenen RRAM-Lastzustand. Das Potenzial von Q- und QB-Knoten kann beide nach Wiedereinschalten der Stromversorgung innerhalb von Nanosekunden wiederhergestellt werden

Parasitärer Effekt und Vergleich

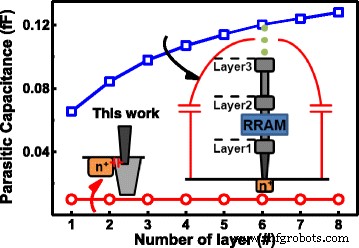

Durch die Integration des vollständig logikkompatiblen STI-RRAM in diese neue SRAM-Zelle kann diese Zelle leicht durch die meisten Standardlogikprozesse implementiert werden, ohne Maskierungsschichten sowie Prozessschritte hinzuzufügen. Dieses Merkmal kann seine Anwendungen und Flexibilität in verschiedenen nichtflüchtigen Speicher-IP-Modulen, die in vielen IC-Systemen benötigt werden, stark verbessern. Darüber hinaus weist der vorgeschlagene 4T2R-nv-SRAM eine viel kleinere parasitäre Kapazität im Vergleich zu anderen zuvor berichteten nv-SRAMs auf [29,30,31], die nichtflüchtige Back-End-of-Line-Komponenten (BEOL) erfordern. Um den Q- und QB-Knoten von der Oberfläche von Si mit diesen BEOL-RRAMs oder -MRAMs zu verbinden, werden mehrere Stapel von Metall- und Durchgangsschichten benötigt. Diese großen Brückenstrukturen führen zu einem signifikanten parasitären RC-Effekt. Große parasitäre Kapazitäten, die in die internen Knoten innerhalb der SRAM-Zellen eingebracht werden, können die Reaktionszeit der Geräte kritisch beeinflussen.

Um den parasitären Effekt auf diese zu vergleichen, werden nv-SRAMs basierend auf der Schätzung der Post-Layout-Simulation untersucht. Unter der Annahme, dass alle Zellen mit der gleichen Standard-CMOS-Technologie implementiert sind, steigt die parasitäre Kapazität an den Latch-Knoten mit zunehmender Anzahl von Metallschichten für Zellen, die große Überbrückungsstrukturen benötigen. Für den neuen nv-SRAM, der STI-RRAM verwendet, gibt es eine sehr geringe Zunahme der Gesamtkapazität an den zwischengespeicherten Knoten. Darüber hinaus ist es unabhängig von der Anzahl der Metallschichten, die in einer bestimmten Schaltung angepasst sind. Um den Effekt der parasitären Kapazität der SRAM-Geschwindigkeit weiter zu untersuchen, werden simulierte dynamische Reaktionen der in [29,30,31] vorgeschlagenen SRAM-Zellen und diese Arbeit in Abb. 12 verglichen.

Parasitäre Kapazität an den Latch-Knoten von nv-SRAM-Zellen aus Lit. [30] und dass aus dieser Arbeit auf der Grundlage der 40-nm-CMOS-Technologie eine signifikante Zunahme der parasitären Kapazität mit zunehmender Anzahl von Metallschichten festgestellt wird

Eine viel kleinere parasitäre Kapazität dieses eingebetteten nv-SRAM kann zu einer schnelleren Reaktionszeit während des dynamischen Lesevorgangs in der SRAM-Zelle führen. Dadurch wird verhindert, dass sich die große interne Kapazität der Verbindungsbrücke auf die Reaktionszeit des logikbasierten SRAM-Arrays auswirkt.

Tabelle 2 vergleicht die Hauptmerkmale früher gemeldeter nichtflüchtiger SRAMs, die in Back-End-RRAMs oder MRAMs eingebaut sind, und diese Arbeit. Trotz der höheren Zustandsschaltspannung bietet der STI-RRAM-basierte nv-SRAM eine viel kleinere parasitäre Kapazität an den internen zwischengespeicherten Knoten innerhalb der SRAM-Zellen und volle Logikkompatibilität.

Variationsinduzierte Verschlechterung des statischen Rauschabstands

Um ein stabiles SNM bei Zellen zu gewährleisten, die Prozessschwankungen, Schwankungen des RRAM-Widerstandsniveaus und der Schwellenspannung des Transistors unterliegen, VT , werden in den folgenden Untersuchungen berücksichtigt:Mismatches in VT ist dafür bekannt, durch skalierte Technologien eine SNM-Verschiebung im SRAM zu verursachen [32, 33]. Darüber hinaus kann dies auch zu unterschiedlich eingestellten Compliance-Strömen führen, was wiederum zu einer erhöhten Variation des Widerstandspegels der beiden RL,L . führen kann . Wie in Abb. 13 dargestellt, unterschiedliche VT zu einem unterschiedlichen Initialisierungs-Compliance-Strom in der STI-RRAM-Zelle führen, was zu einer weiteren Fehlanpassung in RL,L . führt . Um die Auswirkungen von VT . zu analysieren Variation von SNM, nehmen wir an VT eine Gaußsche Zufallsvariable mit Mittelwert und Variation basierend auf früheren Berichten sein [34]. Durch Monte-Carlo-Simulation wird die Verteilung von Schmetterlingskurven, die Variationen in RL,L . ausgesetzt sind, sind in Abb. 14a zusammengefasst. Wenn beide Variationen von RL,L und VT berücksichtigt werden, wird eine signifikante Verengung des SNM-Fensters beobachtet, wie in 14b gezeigt. Erhöhte Variabilität im nv-SRAM muss in zukünftigen Studien berücksichtigt werden.

VT Variation führt zu unterschiedlicher Initialisierungs-Compliance IL,1 und IL,2

Schmetterlingskurven von Monte-Carlo-Simulationen zum Vergleich von SNM-Verschlechterungen durch a Variation in RL,L nach der Initialisierung und b Variationen in beiden RL,L und VT

Schlussfolgerungen

Ein neuartiger 4T2R STI-RRAM-basierter nichtflüchtiger SRAM, der vollständig mit dem CMOS-Logikprozess kompatibel ist, wurde erfolgreich in einem reinen CMOS-Logikprozess an einem 40-nm-Technologieknoten ohne zusätzliche Masken oder Schritte demonstriert. Diese nv-SRAM-Zelle verfügt über einen Selbstsperr- und Selbstwiederherstellungsmechanismus für nichtflüchtige Daten, eine kleine parasitäre Kapazität an den Latch-Knoten und eine statische Nullleistung während des Datenhaltens. Diese überlegenen Eigenschaften machen STI-RRAM-basierte nv-SRAMs zu einer vielversprechenden Lösung für zukünftige nichtflüchtige Speicheranwendungen mit stromsparender/schneller Logik.

Nanomaterialien

- Einführung in digitale integrierte Schaltungen

- Integrierte Schaltkreise

- Digitale Logik mit Feedback

- Dioden-Schaltkreise

- Leistung in ohmschen und reaktiven Wechselstromkreisen

- Praktische Leistungsfaktorkorrektur

- Retentionsmodell von TaO/HfO x und TaO/AlO x RRAM mit selbstrichtenden Schaltereigenschaften

- Bipolar-resistive Schalteigenschaften von HfO2/TiO2/HfO2-RRAM-Bauelementen mit dreischichtiger Struktur auf Pt- und TiN-beschichteten Substraten, die durch Atomlagenabscheidung hergestellt wurden

- Compliance-freier ZrO2/ZrO2 − x /ZrO2 Resistiver Speicher mit steuerbarem Grenzflächen-Mehrzustands-Schaltverhalten

- Leitungsmechanismus und verbesserte Ausdauer bei HfO2-basiertem RRAM mit Nitridierungsbehandlung