Verilog-Mathematikfunktionen können anstelle von konstanten Ausdrücken verwendet werden und unterstützen sowohl Integer und echt Mathematik. Ganzzahlige mathematische Funktionen Die Funktion $clog2 gibt die Obergrenze von log2 zurück des gegebenen Arguments. Dies wird normalerweise verwendet, um d

Anzeigesystemaufgaben werden hauptsächlich verwendet, um Informations- und Debug-Meldungen anzuzeigen, um den Ablauf der Simulation aus Protokolldateien zu verfolgen, und helfen auch beim schnelleren Debuggen. Es gibt verschiedene Gruppen von Anzeigeaufgaben und Formaten, in denen sie Werte drucken

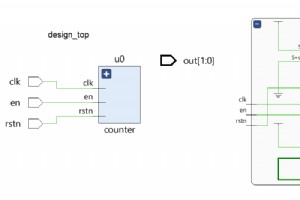

Uhren sind grundlegend für den Aufbau digitaler Schaltungen, da sie es ermöglichen, dass verschiedene Blöcke miteinander synchronisiert werden. Eigenschaften einer Uhr Die Schlüsseleigenschaften einer Digitaluhr sind ihre Frequenz die die Taktperiode bestimmt , seine Einschaltdauer und die Taktphas

Das Design und die Testbench von Verilog haben normalerweise viele Codezeilen, die aus always bestehen oder initial Blöcke, fortlaufende Zuweisungen und andere prozedurale Anweisungen, die zu unterschiedlichen Zeitpunkten im Verlauf einer Simulation aktiv werden. Jede Wertänderung eines Signals im

Die Verilog-Simulation hängt davon ab, wie Zeit definiert ist, da der Simulator wissen muss, was eine Nummer 1 in Bezug auf Zeit bedeutet. Der `timescale Die Compiler-Direktive gibt die Zeiteinheit und Genauigkeit für die darauf folgenden Module an. Syntax `timescale <time_unit>/<time_

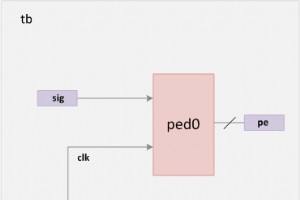

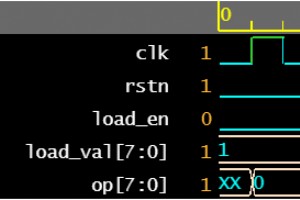

Verilog ist eine Hardwarebeschreibungssprache und Designer müssen ihre RTL-Designs nicht simulieren, um sie in Logikgatter umwandeln zu können. Was muss also simuliert werden? Simulation ist eine Technik, bei der verschiedene Eingangsstimuli zu unterschiedlichen Zeiten auf das Design angewendet w

Standard-Verilog-Primitive wie nand und not ist möglicherweise nicht immer einfach oder ausreichend, um komplexe Logik darzustellen. Neue primitive Elemente namens UDP oder benutzerdefinierte Primitive kann definiert werden, um kombinatorische oder sequentielle Logik zu modellieren. Alle UDPs haben

Verilog bietet auch Unterstützung für die Modellierung auf Transistorebene, obwohl es heutzutage von Designern selten verwendet wird, da die Komplexität von Schaltungen dazu führt, dass sie zu höheren Abstraktionsebenen übergehen, anstatt die Modellierung auf Schalterebene zu verwenden. NMOS/PMOS

Digitale Elemente sind binäre Einheiten und können nur einen der beiden Werte halten - 0 und 1. Der Übergang von 0 auf 1 und 1 auf 0 hat jedoch eine Übergangsverzögerung, ebenso wie jedes Gatterelement, um den Wert vom Eingang zu seinem Ausgang weiterzuleiten. Zum Beispiel muss ein UND-Gatter mit

Einige der wichtigsten eingebauten Primitive wurden im vorherigen Artikel besprochen, und es wäre gut, einige praktische Beispiele für die Verwendung von einfachem and zu sehen , nor und not Tore. Beachten Sie, dass Sie zum Schreiben des Verilog-Codes mit Gates wissen müssen, wie die Elemente verbu

Die meisten digitalen Designs werden auf einer höheren Abstraktionsebene wie RTL erstellt, obwohl es manchmal intuitiv wird, kleinere deterministische Schaltungen auf einer niedrigeren Ebene zu erstellen, indem kombinatorische Elemente wie und verwendet werden und oder . Die Modellierung auf dieser

Die meisten Programmiersprachen haben ein charakteristisches Merkmal namens Bereich die die Sichtbarkeit bestimmter Codeabschnitte für Variablen und Methoden definiert. Der Geltungsbereich definiert einen Namensraum um Kollisionen zwischen verschiedenen Objektnamen innerhalb desselben Namensraums zu

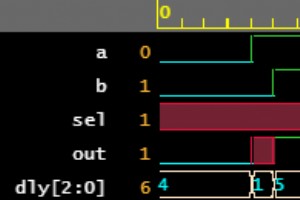

Verilog-Verzögerungsanweisungen können Verzögerungen haben, die entweder auf der linken oder rechten Seite des Zuweisungsoperators angegeben sind. Verzögerungen zwischen Zuweisungen // Delay is specified on the left side #<delay> <LHS> = <RHS> Eine Zwischenzuordnung Verzöge

Es gibt zwei Arten von Zeitsteuerungen in Verilog - Verzögerung und Ereignis Ausdrücke. Die Verzögerung control ist nur eine Möglichkeit, eine Verzögerung zwischen dem Zeitpunkt hinzuzufügen, zu dem der Simulator auf die Anweisung trifft, und wenn er sie tatsächlich ausführt. Der Ereignisausdruck er

Verilog unterstützt einige Compiler-Direktiven, die den Compiler im Wesentlichen anweisen, den Code auf eine bestimmte Weise zu behandeln. Beispielsweise kann ein Teil des Codes eine Implementierung einer bestimmten Funktion darstellen, und es sollte eine Möglichkeit geben, den Code nicht in das Des

Parameter sind Verilog-Konstrukte, die es ermöglichen, ein Modul mit einer anderen Spezifikation wiederzuverwenden. Beispielsweise kann ein 4-Bit-Addierer so parametriert werden, dass er einen Wert für die Anzahl der Bits akzeptiert, und neue Parameterwerte können während der Modulinstanziierung übe

Ein function soll die Eingabe verarbeiten und einen einzelnen Wert zurückgeben, während ein task ist allgemeiner und kann mehrere Ergebniswerte berechnen und sie mit output zurückgeben und inout Argumente eingeben. Aufgaben können simulationszeitaufwändige Elemente wie @ enthalten , gestellt und and

Oft stellen wir fest, dass sich bestimmte Codeteile wiederholen und innerhalb der RTL mehrmals aufgerufen werden. Sie verbrauchen meistens keine Simulationszeit und können komplexe Berechnungen beinhalten, die mit unterschiedlichen Datenwerten durchgeführt werden müssen. In solchen Fällen können wir

Der case -Anweisung prüft, ob der angegebene Ausdruck mit einem der anderen Ausdrücke in der Liste übereinstimmt, und verzweigt entsprechend. Es wird typischerweise verwendet, um einen Multiplexer zu implementieren. Das if-else-Konstrukt ist möglicherweise nicht geeignet, wenn viele Bedingungen über

Ein for Schleife ist die am weitesten verbreitete Schleife in Software, wird aber hauptsächlich zum Replizieren verwendet Hardwarelogik in Verilog. Die Idee hinter einer for Schleife besteht darin, eine Reihe von Anweisungen zu wiederholen, die in der Schleife angegeben sind, solange die angegebene

Verilog