Blockierung Blockierung Zuweisungsanweisungen werden mit = zugewiesen und werden nacheinander in einem Verfahrensblock ausgeführt. Dies verhindert jedoch nicht die Ausführung von Anweisungen, die in einem parallelen Block ausgeführt werden. module tb; reg [7:0] a, b, c, d, e; initial be

Das Platzieren von Werten auf Netzen und Variablen wird als Zuweisungen bezeichnet. Es gibt drei Grundformen: Verfahrensweise Kontinuierlich Prozedural kontinuierlich Gesetzliche LHS-Werte Eine Zuweisung besteht aus zwei Teilen – rechts (rechts) und links (links) mit einem Gleichheitszeichen (=) o

Es gibt Möglichkeiten, eine Reihe von Anweisungen zu gruppieren, die syntaktisch einer einzelnen Anweisung entsprechen und als Blockanweisungen bezeichnet werden . Es gibt zwei Arten von Blockanweisungen:sequentiell und parallel. Sequentiell Anweisungen werden mit begin umschlossen und end Schlüsse

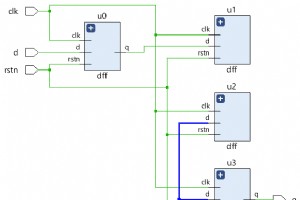

Ein vorheriges Beispiel untersuchte einen einfachen Sequenzdetektor. Hier ist ein weiteres Beispiel für einen Musterdetektor, der ein etwas längeres Muster erkennt. Gestaltung module det_110101 ( input clk, input rstn, input in, output

Ein sehr häufiges Beispiel für einen FSM ist ein Sequenzdetektor, bei dem erwartet wird, dass das Hardwaredesign erkennt, wenn ein festes Muster in einem Strom von binären Bits gesehen wird, die ihm eingegeben werden. Beispiel module det_1011 ( input clk, input rstn,

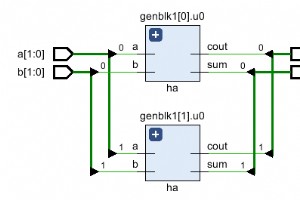

Ein generate block ermöglicht es, Modulinstanzen zu multiplizieren oder eine bedingte Instanziierung eines beliebigen Moduls durchzuführen. Es bietet die Möglichkeit, das Design basierend auf Verilog-Parametern zu erstellen. Diese Anweisungen sind besonders praktisch, wenn die gleiche Operation oder

Der gesamte Verhaltenscode ist in module geschrieben und endmodule . Welches digitale Design Sie auch immer erstellen möchten, es passt in module Block. Es können Ports definiert sein oder nicht - erlauben Sie Signalen, in den Block als input einzutreten oder entkomme dem Block als output . Modul D

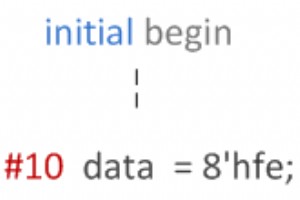

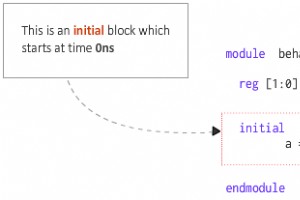

In einer Simulation wird normalerweise eine Reihe von Verilog-Anweisungen nacheinander ausgeführt. Diese Anweisungen werden innerhalb einer Prozedur platziert Block. Es gibt hauptsächlich zwei Arten von Verfahren Blöcke in Verilog - initial und immer Syntax initial [single statement] ini

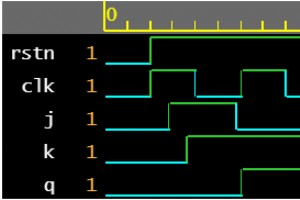

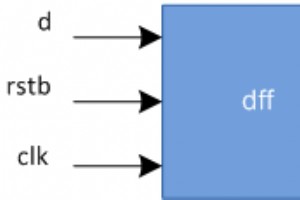

Ein früherer Artikel zeigte verschiedene Beispiele für die Verwendung eines always Block, um kombinatorische Logik zu implementieren. Eine always block wird auch hauptsächlich verwendet, um sequenziell zu implementieren Logik, die Speicherelemente wie Flip-Flops hat, die Werte halten können. JK-Flip

Der Verilog-Always-Block kann sowohl für sequentielle als auch für kombinatorische Logik verwendet werden. Anhand eines assign wurden einige Gestaltungsbeispiele gezeigt Aussage in einem früheren Artikel. Derselbe Satz von Designs wird als Nächstes mit einem always erkundet blockieren. Beispiel Nr.

Ein always block ist einer der prozeduralen Blöcke in Verilog. Anweisungen innerhalb eines Always-Blocks werden sequentiell ausgeführt. Syntax always @ (event) [statement] always @ (event) begin [multiple statements] end Die always Block wird bei einem bestimmten Ereignis ausgeführt. Da

Multi-Bit-Verilog-Wires und -Variablen können mithilfe von Verkettung zusammengelegt werden, um ein größeres Multi-Net-Wire oder eine Variable zu bilden Operatoren { und } durch Kommata abgetrennt. Die Verkettung darf neben Verbindungen und Variablen auch Ausdrücke und Größenkonstanten als Operanden

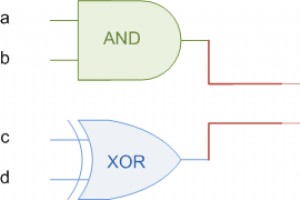

Daten, die nicht verarbeitet werden können, sind ziemlich nutzlos, in digitalen Schaltungen und Computersystemen ist immer irgendeine Form von Berechnung erforderlich. Schauen wir uns einige der Operatoren in Verilog an, die es Synthesewerkzeugen ermöglichen würden, geeignete Hardwareelemente zu rea

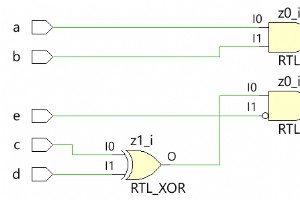

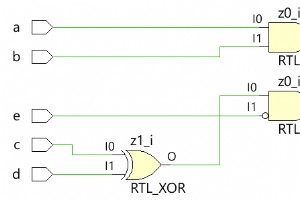

Die Verilog-Zuweisungsanweisung wird normalerweise verwendet, um ein Signal von wire kontinuierlich zu steuern Datentyp und wird als kombinatorische Logik synthetisiert. Hier sind einige weitere Designbeispiele mit assign Aussage. Beispiel Nr. 1:Einfache kombinatorische Logik Der unten gezeigte Cod

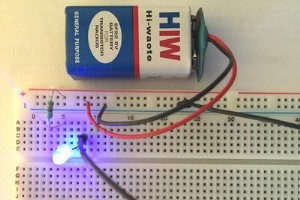

Signale vom Typ wire oder ein ähnlicher wire-artiger Datentyp erfordert die kontinuierliche Zuweisung eines Wertes. Stellen Sie sich zum Beispiel einen elektrischen Draht vor, der zum Verbinden von Teilen auf einem Steckbrett verwendet wird. Solange die +5V-Batterie an einem Ende des Kabels anliegt,

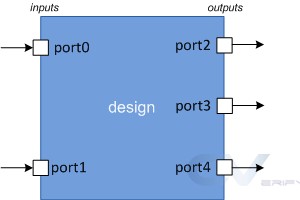

Wie wir in einem früheren Artikel gesehen haben, werden größere und komplexe Designs erstellt, indem mehrere Module hierarchisch integriert werden. Module können instanziiert werden innerhalb anderer Module und Ports dieser Instanzen kann mit anderen Signalen innerhalb des übergeordneten Moduls verb

Ports sind eine Reihe von Signalen, die als Ein- und Ausgänge für ein bestimmtes Modul fungieren und die primäre Art der Kommunikation mit ihm darstellen. Stellen Sie sich ein Modul als einen vorgefertigten Chip vor, der auf einer Leiterplatte platziert ist, und es wird ziemlich offensichtlich, dass

Ein module ist ein Block von Verilog-Code, der eine bestimmte Funktionalität implementiert. Module können in andere Module eingebettet werden und ein Modul höherer Ebene kann mit seinen Modulen niedrigerer Ebene über deren Eingangs- und Ausgangsports kommunizieren. Syntax Ein Modul sollte in module

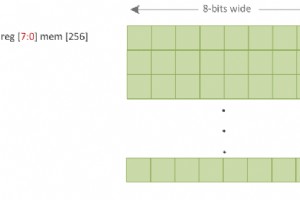

Ein Array Die Deklaration eines Netzes oder einer Variablen kann entweder skalar oder vektoriell sein. Eine beliebige Anzahl von Dimensionen kann durch Angabe eines Adressbereichs nach dem Bezeichnernamen erstellt werden und wird als mehrdimensionales Array bezeichnet. Arrays sind in Verilog für reg

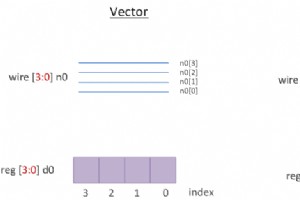

Verilog muss sowohl einzelne Bits als auch Gruppen von Bits darstellen. Beispielsweise ist ein sequentielles Einzelbitelement ein Flip-Flop. Ein sequentielles 16-Bit-Element ist jedoch ein Register, das 16 Bits aufnehmen kann. Zu diesem Zweck hat Verilog Skalar und Vektor Netze und Variablen. Skalar

Verilog

Der ultimative Leitfaden für EAM:Funktionsweise von EAMs, Vorteile und Auswahl der richtigen EAM-Lösung für Ihre Anforderungen

Teilen Sie Aufgaben sorgfältig zwischen Menschen und Robotern auf

Schaltkonzepte:Schließen einer Lücke im Kfz-Ersatzteilmarkt mit 3D-gedruckten Schaltwippen

CompositesWorld und ITHEC sind Partner für thermoplastische Verbundwerkstoffe 3-tägige virtuelle Veranstaltung