So erstellen Sie einen getakteten Prozess in VHDL

Die überwiegende Mehrheit der VHDL-Designs verwendet getaktete Logik , auch bekannt als synchrone Logik oder sequenzielle Logik . Ein getakteter Prozess wird nur durch ein Haupttaktsignal ausgelöst, nicht wenn sich eines der anderen Eingangssignale ändert.

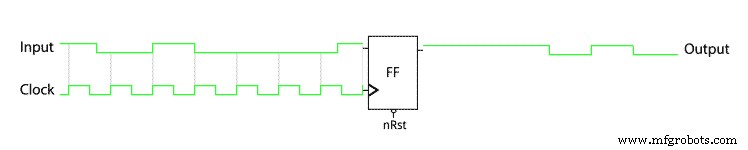

Der Grundbaustein der getakteten Logik ist eine Komponente namens Flip-Flop . Es gibt verschiedene Varianten davon, und in diesem Tutorial konzentrieren wir uns auf das durch positive Flanke getriggerte Flip-Flop mit negativem Reset:

Das Flip-Flop ist eine Sample-and-Hold-Schaltung, das heißt, es kopiert den Wert vom Eingang zum Ausgang, wenn die steigende Flanke des Taktsignals eintrifft. Der Ausgang wird dann bis zur nächsten ansteigenden Taktflanke oder bis das Reset-Signal gepulst wird, stabil auf dem abgetasteten Wert gehalten.

Dieser Blogpost ist Teil der Reihe Basic VHDL Tutorials.

Alle getakteten Prozesse werden gleichzeitig ausgelöst und lesen ihre Eingaben sofort. Gleichzeitig geben sie die Ergebnisse der letzten Iteration aus. Das Taktsignal erzeugt effektiv Zeitschritte im Datenfluss. Dies macht es für den Designer überschaubar, komplexe, tiefgreifende Logik zu erstellen. Er oder sie kann die Aktionen des Algorithmus in Ereignisse zerlegen, die in Taktzyklen stattfinden.

Flip-Flops oder Arrays von Flip-Flops werden manchmal als Register bezeichnet , es ist dasselbe.

Die Empfindlichkeitsliste für getaktete Prozesse enthält normalerweise nur das Taktsignal. Dies liegt daran, dass ein getakteter Prozess nur durch eine Flanke des Taktsignals ausgelöst wird, die anderen Eingangssignale werden ihn überhaupt nicht aufwecken.

Dies ist eine Vorlage zum Erstellen eines getakteten Prozesses mit synchronem Reset:process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

Übung

In diesem Video-Tutorial lernen wir, wie man einen getakteten Prozess in VHDL erstellt:

Der endgültige Code für Flip-Flop Testbench :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

Der endgültige Code für das Flipflop-Modul :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

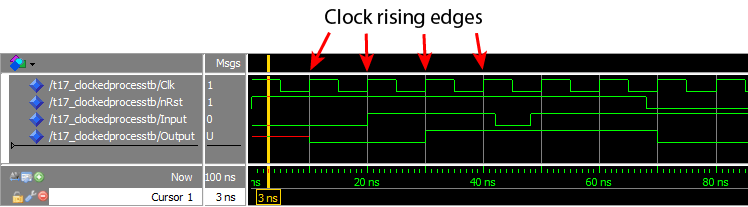

Das Wellenformfenster in ModelSim, nachdem wir auf Ausführen gedrückt und die Zeitachse vergrößert haben:

Analyse

Wir können aus der Wellenform ersehen, dass das Ausgangssignal nur bei jeder steigenden Flanke des Taktsignals aktualisiert wird. Das Eingangssignal wird nur abgetastet, wenn das Taktsignal von „0“ auf „1“ wechselt. Der negative Einbruch des Eingangssignals ab etwa 45 ns geht komplett verloren. Es wird nicht in den Ausgang kopiert, da es zwischen zwei ansteigenden Flanken der Uhr liegt und daher ignoriert wird.

Diese Animation veranschaulicht, wie der Ausgang auf die sich ändernden Eingangs- und Taktsignale reagiert:

Die vertikalen Linien zeigen an, wie das Eingangssignal relativ zu den steigenden Flanken des Takts ist.

Achten Sie besonders auf den einen positiven Impuls des Eingangssignals ab 20 ns. Sie ist taktsynchron und genau eine Taktperiode lang. Der Ausgang reagiert nicht sofort, sondern um eine Taktperiode verzögert.

Als ich VHDL lernte, fand ich das besonders schwer zu verstehen. Die steigende Flanke der Uhr ist synchron mit der steigenden Flanke des Eingangs, also wie kann das Flip-Flop den einen oder anderen Wert wählen?

Der Simulator verwendet Zeitschritte, um Ereignisse auf vorhersehbare Weise zu modellieren, und Signale breiten sich in Nullzeit aus. Da das Flip-Flop die Eingabe im exakt gleichen Zeitschritt liest, in dem es die Ausgabe aktualisiert, sieht es den alten Wert der Eingabe und kopiert ihn in die Ausgabe.

Lesen Sie hier mehr über VHDL-Zeitschritte:Delta-Zyklen erklärt

Ich sollte dieser Antwort hinzufügen, dass dies wirklich nicht der Fall ist wie es funktioniert. In der physischen Welt braucht ein Signal Zeit, um sich auszubreiten, wir wissen nicht genau, wann es am Flip-Flop ankommt. Diese Ausbreitungsverzögerungen werden für uns automatisch durch den Softwareprozess (Ort und Route) geschätzt, der den VHDL-Code in eine Netzliste umwandelt.

In Wirklichkeit muss der Eingang einige Nanosekunden vor und nach der steigenden Taktflanke stabil gehalten werden:

Diese kritischen Zeiträume sind als Setup-and-Hold-Zeit bekannt. Glücklicherweise ist dies etwas, was Sie normalerweise nicht berücksichtigen müssen. Beim reinen Arbeiten mit getakteter Logik werden diese Probleme von der Software behandelt, die den VHDL-Code in eine Netzliste umwandelt.

Imbiss

- Getaktete Prozesse mit synchronisiertem Reset haben nur das Taktsignal auf der Sensitivitätsliste

- Die

if rising_edge(Clk)stellt sicher, dass der Prozess nur bei steigenden Taktflanken aufwacht - In einem synchronen Design passiert alles nur bei aktiver Taktflanke

Nehmen Sie am Basic VHDL Quiz teil 3 »

oder

gehen Sie zum nächsten Tutorial »

VHDL

- So erstellen Sie eine Liste von Zeichenfolgen in VHDL

- So erstellen Sie eine Tcl-gesteuerte Testbench für ein VHDL-Code-Sperrmodul

- So stoppen Sie die Simulation in einer VHDL-Testbench

- So erstellen Sie einen PWM-Controller in VHDL

- So generieren Sie Zufallszahlen in VHDL

- So erstellen Sie einen Ringpuffer-FIFO in VHDL

- So erstellen Sie eine selbstüberprüfende Testbench

- So erstellen Sie eine verknüpfte Liste in VHDL

- So verwenden Sie eine Prozedur in einem Prozess in VHDL

- So verwenden Sie eine Funktion in VHDL