CXL 2.0 /PCIe 5.0-Lösungen beseitigen heterogene Rechen- und Datenengpässe

Das Fabless-Halbleiter-Startup Astera Labs hat eine neue speziell entwickelte CXL 2.0- und PCIe 5.0-Konnektivitätslösung angekündigt, um heterogene Rechenarchitekturen zu erschließen und latenzempfindliche Workloads im Rechenzentrum zu bewältigen. Das Unternehmen sagte, das Ziel dieser neuen Lösungen sei es, systemweite Leistungsengpässe in datenzentrierten Anwendungen zu beheben.

Die Verbreitung von Daten und das Mainstreaming spezialisierter Workloads – wie künstliche Intelligenz (KI) und maschinelles Lernen (ML) – erfordern speziell entwickelte Beschleuniger, die Seite an Seite mit Allzweck-CPUs auf demselben Motherboard oder innerhalb desselben Racks arbeiten, während einen gemeinsamen Speicherplatz teilen. CXL 2.0-Interconnect ist der Schlüssel, um solche Cache-kohärenten Systemtopologien zu ermöglichen.

Das erste Produkt im neuen Portfolio von Astera Labs ist das intelligente Retimer-Portfolio von Aries Compute Express Link (CXL 2.0) (PT5161LX, PT5081LX) für CXL.io-Konnektivität mit niedriger Latenz, das bei strategischen Kunden aktiv getestet wird. Der CEO des Unternehmens, Jitendra Mohan, sagte:„Mit unserer Expansion in das CXL-Ökosystem macht Astera Labs einen weiteren großen Schritt, um zweckgerichtete Lösungen anzubieten, die komplexe heterogene Computing- und zusammensetzbare Disaggregation-Systemtopologien erschließen.“

Die CXL 2.0-Spezifikation wurde im November 2020 vom CXL-Konsortium veröffentlicht. CXL ist eine offene Verbindung nach Industriestandard, die Kohärenz und Speichersemantik bietet, die eine Konnektivität mit hoher Bandbreite und geringer Latenz zwischen Hostprozessor und Geräten wie Beschleunigern, Speicherpuffern und Smart . nutzt E/A-Geräte. Die CXL 2.0-Spezifikation bietet Unterstützung für das Umschalten für Fan-Out, um eine Verbindung zu mehr Geräten herzustellen; Speicherpooling für eine verbesserte Speichernutzungseffizienz und Bereitstellung von Speicherkapazität nach Bedarf; und Unterstützung für persistenten Speicher. All dies geschieht unter Wahrung der Industrieinvestitionen durch die Unterstützung der vollständigen Abwärtskompatibilität mit CXL 1.1 und 1.0.

Der Präsident des CXL-Konsortiums, Barry McAuliffe, sagte:„Als frühes Mitglied des CXL-Konsortiums hat Astera Labs seine Konnektivitätsexpertise zur Weiterentwicklung des CXL-Standards beigetragen. Es ist großartig zu sehen, dass seine erste CXL-Siliziumimplementierung zur Unterstützung eines schnell wachsenden CXL-Ökosystems auf den Markt kommt.“

Neue PCIe 5.0-Lösungen in Zusammenarbeit mit Intel

Astera Labs kündigte außerdem die Verfügbarkeit eines neuen Low-Latency-Modus in seinem Aries-Smart-Retimer-Portfolio für PCIe-Konnektivität mit skalierbaren Intel Xeon-Prozessoren an. Diese Entwicklung war das Ergebnis einer engen Zusammenarbeit mit der Intel Corporation, um die Latenz bei PCIe-Links auf unter 10 ns weiter zu reduzieren und die Leistung bei datenzentrierten Workloads zu verbessern. Astera Labs behauptete, es sei der erste Anbieter, der eine robuste PCIe 5.0-Interoperabilität mit skalierbaren Intel Xeon-Prozessoren mit dem Codenamen „Sapphire Rapids“ demonstrierte.

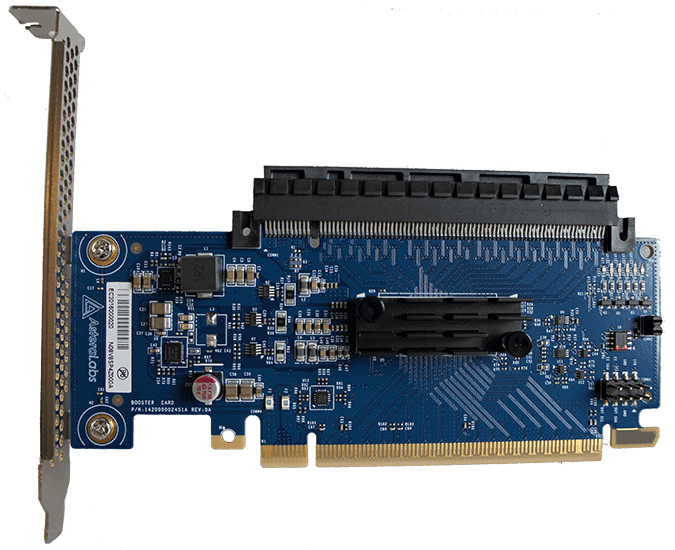

Zur gleichen Zeit wird auch eine neue Plug-and-Play-Smart-Retimer-Add-In-Karte für PCIe/CXL-Anwendungen namens Equinox eingeführt. Die Karte und die zugehörige speziell entwickelte Firmware wurden ebenfalls in Zusammenarbeit mit Intel entwickelt und vereinfachen die Entwicklung von PCIe 5.0-fähigen Systemen mit den neuesten skalierbaren Xeon-Prozessoren von Intel. Dies stellt den Übergang von Astera Labs dar, benutzerfreundliche Plug-and-Play-Boards anzubieten, um komplexe Systemtopologien schnell zu implementieren.

„PCIe Gen5 und CXL sind grundlegende Technologien für heterogene Rechenworkloads und Rechenzentrumsarchitekturen heute und morgen“, sagte Zane Ball, Corporate VP und General Manager für Rechenzentrumstechnik und Architektur bei Intel. „Intel arbeitet mit führenden Anbietern von Ökosystemen wie Astera Labs zusammen, um die PCIe- und CXL-Interconnect-Latenz auf der kommenden Intel Xeon Scalable-Plattform mit dem Codenamen ‚Sapphire Rapids‘ und weiteren Plattformen deutlich zu reduzieren.“

Verwandte Inhalte:

- Retiming von USB4 über USB-C

- Hochleistungs-Interconnects mit mehreren PCIe-Generationen aufbauen

- Xilinx zielt auf die Auslagerung von Rechenzentren mit „zusammensetzbarer“ Hardware ab

- Wie Edge-Supercomputing die große Datenflut verändern wird

Eingebettet

- Rechtliche Probleme beim Cloud-Computing und deren Lösungen

- DATA MODUL:Kundenorientierte Digital Signage-Lösungen auf der ISE

- Mikrochip:Taktpuffer erfüllen DB2000Q/QL-Standards plus PCIe Gen 4 und 5 Low-Jitter-Spezifikationen

- Apacer:PCIe NVMe Gen3 SSDs, der nächste logische Schritt für industrietauglichen Speicher

- Swissbit:hardwarebasierte Sicherheitslösungen zum Schutz von Daten und Geräten

- TECHWAY:Kintex-7 FPGA PCIe-Plattform zur Steigerung der Datenratenleistung mit 12 HSS-Links

- Strategie und Lösungen der Armee für zustandsorientierte Instandhaltung

- Die Vorteile der Anpassung von IIoT- und Datenanalyselösungen für EHS

- Bekämpfung von Überschwemmungen in städtischen Gebieten mit IoT-Netzwerklösungen

- Wie das Internet der Dinge die Lieferkette verändert:Teil 2, Zukünftige Lösungen