Die Bedeutung der Zuverlässigkeitsüberprüfung bei KI/ML-Prozessoren

Mit der Einführung von künstlicher Intelligenz und maschinellem Lernen in eine Vielzahl von Anwendungen ist die Zuverlässigkeitsüberprüfung von KI/ML-Prozessoren von entscheidender Bedeutung, da Ausfälle schwerwiegende Folgen haben können für die Gültigkeit und Legitimität der KI/ML-Technologie.

In den letzten Jahren hat die Zahl der Unternehmen, die künstliche Intelligenz (KI) und maschinelles Lernen (ML) in einer Vielzahl von Anwendungen einsetzen, rasant zugenommen. Tatsächlich zeigen Studien, dass 2019 ein Rekordjahr für Unternehmen war, die KI und ML einführten, und dass diese Unternehmen diese beiden Funktionen als die am dringendsten benötigten ansehen, um ihre Geschäftsstrategien und -ziele zu erreichen. Diese wachsende Akzeptanz ist in erster Linie auf die Verbesserung der Algorithmen, Fortschritte im Hardwaredesign und die Zunahme des Datenvolumens zurückzuführen, das durch die Digitalisierung von Informationen entsteht.

Um jedoch das Wachstum von KI/ML zu unterstützen und aufrechtzuerhalten, müssen Unternehmen dem Markt weiterhin beweisen, dass die Ergebnisse, die sie mit KI/ML-Technologien erzielen, vertrauenswürdig sind. Dieses Vertrauen beginnt mit dem Design und der Verifizierung der integrierten Schaltkreise (ICs), die der KI/ML-Funktionalität zugrunde liegen.

Klassifizierung von KI und ML

Die KI-Verarbeitung kann grob in Rechenzentrums-/Cloud-basiert oder eingebettet eingeteilt werden, je nachdem, ob sie auf einer Cloud-/Rechenzentrums-Site oder auf der Endbenutzerseite durchgeführt wird (durch Einbetten eines dedizierten KI-Chips oder einer KI-Coprozessor-Engine mit ein System-on-Chip (SOC) in Geräten oder am Rand). Edge bezieht sich in diesem Zusammenhang auf einen lokalen Server oder eine Maschine, die näher am Gerät ist als ein Rechenzentrum oder eine Cloud.

In Bezug auf die Zielanwendung kann ein Edge-Gerät in Training (ML) oder Inferenz eingeteilt werden. In der Vergangenheit wurde der Trainingsteil auf der Cloud-Site durchgeführt, wobei der Inferenzteil entweder in der Cloud oder auf dem Edge-Gerät verarbeitet wurde. Mit der Entwicklung neuer Hochleistungs-Edge-Computing-Lösungen erleben wir einen Paradigmenwechsel, da immer mehr Trainingsaktivitäten auf die Edge-Seite verlagert werden.

KI/ML-Chipdesign

KI/ML-Chips in Edge-Computing-Lösungen oder eingebettet in lokale Geräte sind für den Einsatz in bestimmten Umgebungen wie Unternehmen, Automobil, Industrie, Gesundheitswesen, Internet der Dinge (IoT) usw. konzipiert. Einige dieser Anwendungen sind geschäftskritisch, d Jeder Fehler kann in der realen Welt katastrophale Folgen haben. Betrachten Sie beispielsweise fortschrittliche Fahrerassistenzsysteme (ADAS), die in Autos verwendet werden. Wenn ein ADAS-Prozessor beim Lesen von Daten vom Sensor und beim Ziehen einer Schlussfolgerung mehr als eine vorgegebene Latenzzeit erfährt, kann dies zu einer Kollision führen.

Die in KI/ML-Anwendungen verwendeten ICs zeichnen sich durch große parallele Recheneinheiten, hohe Verlustleistung und komplexe Schaltungen aus, die maximale Leistung bei einem strengen Leistungsbudget liefern können. Während einige Unternehmen traditionelle Zentraleinheiten (CPUs) für KI-bezogene Aufgaben verwenden, argumentieren einige Branchenexperten, dass der Einsatz von CPUs aufgrund der verteilten Natur modernster KI-Algorithmen nicht sehr effizient ist. Diese Algorithmen eignen sich gut für Parallel-Computing-Lösungen, wie sie von Grafikprozessoren (GPUs) bereitgestellt werden. Aufgrund ihrer rekonfigurierbaren Natur haben feldprogrammierbare Gate-Arrays (FPGAs) auch Interesse für den Einsatz als Beschleuniger für KI-Chips geweckt.

ASICs in KI/ML-Anwendungen

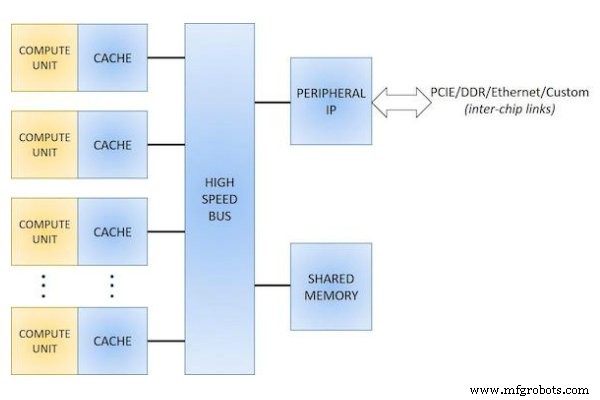

Insgesamt besteht ein wachsender Konsens darüber, dass sich die kniffligen Probleme von KI und ML nicht für eine einheitliche Designlösung eignen. Um dieses Problem zu bekämpfen, entwickeln viele Unternehmen ihre eigenen anwendungsspezifischen ICs (ASICs), die sie in Verbindung mit dem Software-Stack optimieren, um den besten Wert für eine bestimmte KI/ML-Anwendung zu erzielen (Abbildung 1).

Abbildung 1. Blockschaltbild für ein ASIC-KI-Chipdesign.

Diese Unternehmen beanspruchen verschiedene Vorteile aus der Verwendung dieser ASICs, wie z CPU), geringerer Stromverbrauch und schnellere Entwicklungszeit.

Heterogene Computer

Auch der Einsatz von heterogenem Computing hat zugenommen – Systeme, die eine Kombination verschiedener Rechenkerntypen verwenden, um das Beste aus unterschiedlichen Fähigkeiten zu kombinieren. In einem System, das beispielsweise eine Kombination aus CPU und GPU verwendet, kann heterogenes Computing von Vorteil sein, indem die parallelen Aufgaben auf die GPU ausgelagert werden, während die CPU Aufgaben wie die von Natur aus serielle Prozesssteuerung übernimmt.

Ein gemeinsamer Aspekt verschiedener Klassen von KI-Prozessoren besteht darin, dass sie für hohe Leistung und geringe Latenz optimiert sind und oft Multiplikatoren für die Leistung von Tera-Operationen pro Sekunde (TOPS) bieten. Um sich in diesem hart umkämpften Markt einen Vorteil zu verschaffen, ist die Energieeffizienz (gemessen an der Leistung pro Watt) genauso wichtig wie der reine Durchsatz. Die Energieeffizienz wird oft durch die Verwendung einer Kombination aus einer oder mehreren Designtechniken wie Power- und Clock-Gating, dynamische Spannungs- und Frequenzskalierung, Multi-Vt-Designs usw. erreicht.

Die Gewährleistung des zuverlässigen Designs und der Verifizierung dieser komplexen ICs ist von entscheidender Bedeutung, da Schaltungsausfälle in diesen Chips schwerwiegende Folgen für die Gültigkeit der Technologie und die Legitimität der von ihnen gelieferten Ergebnisse haben können.

KI/ML-IC-Zuverlässigkeitsprüfung

Die Verifizierung der Zuverlässigkeit ist bei KI/ML-Chips aufgrund der Größe und Komplexität dieser Designs mit Transistorzahlen im Millionenbereich – manchmal sogar im Milliardenbereich – eine enorme Herausforderung. NVIDIAs TESLA-P100-GPU beispielsweise verfügt über eine atemberaubende Transistorzahl von 15,3 Milliarden, während Intels Loihi-IC 128 neuromorphe Kerne und 3 X-86-Kerne mit 2,07 Milliarden Transistoren enthält. Und da die Zuverlässigkeitsanforderungen für jede Anwendungsumgebung unterschiedlich sind, müssen Designer die geltenden Anforderungen verstehen und sicherstellen, dass diese erfüllt werden, indem sie ihre Designs anhand klar definierter Zuverlässigkeitsanforderungsspezifikationen testen.

Methoden zur Überprüfung der Designzuverlässigkeit

Traditionell verwendeten Konstrukteure eine Vielzahl von Methoden, um die Konstruktionszuverlässigkeit sicherzustellen, einschließlich manueller Inspektions- und Simulationstechniken, wobei sie sich hauptsächlich auf das Fachwissen und die Erfahrung ihres Konstruktionsteams stützten. Eine manuelle Inspektion ist jedoch für diese großen und komplexen KI/ML-Chips kein praktikabler Ansatz, da sie zeitaufwändig und anfällig für menschliche Fehler ist und eine ausreichende Abdeckung praktisch unmöglich ist. Herkömmliche SPICE-ähnliche Simulationsansätze sind für diese ICs aufgrund ihrer mangelnden Skalierbarkeit für große Designs ebenfalls nicht praktikabel.

Um Kapazitäts- und Laufzeitprobleme zu überwinden, partitionieren viele Designteams ein Design manuell und verifizieren verschiedene Blöcke des geistigen Eigentums (IP) unabhängig durch Simulation oder herkömmliche Tools. Es gibt jedoch viele Interaktionen zwischen verschiedenen IP-Blöcken in einem Design (z. B. zwischen verschiedenen Rechenkernen und dem Bus oder Link oder Speicher mit hoher Bandbreite), und die Interaktionen zwischen Schnittstellen werden während eines manuellen Partitionierungsprozesses oft übersehen. Herkömmliche IC-Verifizierungstools haben Probleme mit übermäßig langen Laufzeiten, um diese komplexen Designs zu verifizieren, was oft Tage dauert, um große Designs zu verifizieren, und möglicherweise die Markteinführungszeit verzögern.

Die Mängel in jedem dieser Prozesse verdeutlichen die Notwendigkeit einer umfassenden automatisierten Electronic Design Automation (EDA)-Lösung, die die Rechenleistung mehrerer CPUs und Geräte gleichzeitig nutzen kann. Mit automatisierter, qualifizierter Zuverlässigkeitsüberprüfung können Produktdesign- und Überprüfungsteams schneller auf Zuverlässigkeitsüberprüfungen und -behebungen eingehen und ihre Gesamtdurchlaufzeit (TAT) von Tagen auf Stunden reduzieren.

Die Calibre PERC-Zuverlässigkeitsplattform

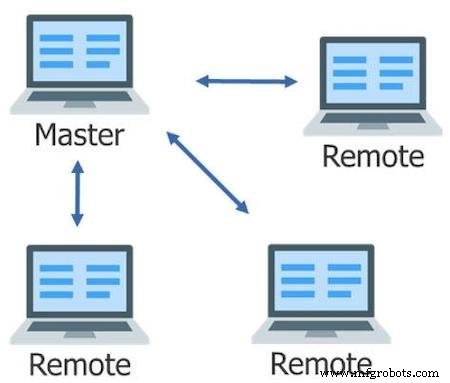

In den letzten Jahren ist eine neue Klasse von Tools zur Überprüfung der IC-Zuverlässigkeit entstanden, die diese Prozessprobleme lösen. Tools wie die Zuverlässigkeitsplattform Calibre™ PERC™ nutzen eine Vielzahl von Funktionen und Funktionen, um eine schnelle, gießereiqualifizierte Zuverlässigkeitsüberprüfung zu ermöglichen. Beispielsweise nutzt die Calibre PERC-Zuverlässigkeitsplattform die Multi-Threaded (MT) und Multi-Threaded Flexible (MTflex) Skalierung der Calibre Plattform, die Aufgaben auf mehrere CPUs und/oder Remote-Maschinen verteilt, um eine schnelle und effiziente Ausführung von Verifizierungsprozessen zu ermöglichen auf großen und komplexen Chips wie AI/ML-ICs (Abbildung 2).

Abbildung 2. Multithreaded, flexible Skalierung verteilt Aufgaben auf mehrere Remotes für eine schnellere Gesamtausführung.

Über diese grundlegenden, aber wesentlichen Mechanismen hinaus bietet die Calibre PERC-Zuverlässigkeitsplattform eine innovative Verarbeitung, die sowohl Netzlisten- als auch Layout-Informationen aus einem Design kombiniert, um schnell und präzise eine Vielzahl potenzieller Zuverlässigkeitsprobleme zu bewerten. Indem es Designern ermöglicht, die Anfälligkeit eines Designs für Leistung und Betriebsfehler effizient und sicher zu reduzieren, trägt dieser Ansatz zur erweiterten Zuverlässigkeitsüberprüfung dazu bei, das kontinuierliche Wachstum und die Einführung vertrauenswürdiger KI/ML-Technologie zu unterstützen.

Zuverlässigkeit auf Transistorebene

Die meisten ML/AI-Designs verwenden mehrere Leistungsdomänen für eine Vielzahl von Zwecken, z für ausgewählte IPs unabhängig nach oben oder unten schalten oder hohe Stromanforderungen mit mehreren Spannungsreglern erfüllen. Der Skylake-Prozessor von Intel enthält beispielsweise neun primäre Leistungsbereiche.

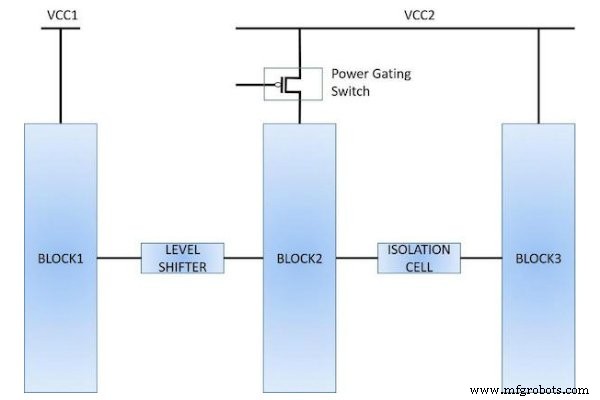

Die Implementierung eines Designs mit mehreren Leistungsdomänen erfordert die Verwendung spezieller Schaltungselemente wie Spannungsregler, Kopf- und Fußschalter, Pegelumsetzer, Isolationszellen und Zustandserhaltungszellen. Diese Elemente stellen eine einzigartige Reihe von Herausforderungen für die Zuverlässigkeitsüberprüfung dar. Designer müssen beispielsweise überprüfen, ob an jeder Domänenschnittstelle geeignete Level-Shifter- oder Isolationszellen verwendet werden und dass sie richtig angeschlossen sind (Abbildung 3).

Abbildung 3. Die Verwendung spezieller Elemente (wie Pegelumsetzer, Isolationszellen und Power-Gating-Schalter) in einem Low-Power-Design erfordert spezielle Verifikationstechniken.

Sie müssen auch sicherstellen, dass sie die geeigneten Gerätetypen in verschiedenen Leistungsbereichen verwenden, wie z. B. Dickoxidgeräte für die Hochspannungsversorgung. Die Überprüfung dieser Bedingungen erfordert sehr spezifische Kenntnisse und Prozesse.

Die Unified Power Format-Technik

Das Unified Power Format (UPF) ist eine weit verbreitete Technik, die es Designern ermöglicht, während des gesamten Entwurfsablaufs eine konsistente Beschreibung der Leistungsabsicht zu verwenden. Herkömmliche UPF-basierte Verifizierungsabläufe werden jedoch verwendet, um IPs auf Logik- oder Gate-Ebene zu validieren, aber sie haben nicht die Möglichkeit, die endgültigen Implementierungen auf Transistorebene zu validieren, insbesondere die Wannen- und Bulk-Verbindungen.

Die Calibre PERC-Zuverlässigkeitsplattform kann die UPF-Datei für ein Design lesen und UPF-Informationen nutzen, um verschiedene Analysen auf Transistorebene durchzuführen, z . Durch die Verwendung der Calibre PERC-Zuverlässigkeitsplattform in Verbindung mit den UPF-Daten können Entwickler Geräteinteraktionen programmgesteuert bewerten, um eine wiederholbare und deterministische Zuverlässigkeitsüberprüfung zu ermöglichen.

Lebenslange Zuverlässigkeit von KI/ML-Chips

Die Betriebssicherheit ist ein kritischer Aspekt für die meisten KI/ML-Chips, von denen erwartet wird, dass sie während ihrer gesamten Lebensdauer ohne Störungen oder Ausfälle funktionieren. Einige Probleme der elektrischen Zuverlässigkeit, wie z. B. Bias-Temperatur-Instabilität (BTI) und EOS, manifestieren sich möglicherweise nicht als sofortige Ausfälle, können jedoch im Laufe der Zeit zu einer schnellen Verschlechterung und Alterung führen, wenn sie nicht vor der Herstellung behoben werden. Die Zuverlässigkeitsüberprüfung kann dazu beitragen, einen robusten Betrieb über einen längeren Zeitraum sicherzustellen, indem sie auf verschiedene Probleme wie Punkt-zu-Punkt-Widerstand, positive und negative BTI, Stromdichte und Elektromigration (EM) überprüft, die alle zu Leistungseinbußen oder katastrophalen Ausfällen führen können.

Betrachten Sie den Fall, in dem ein Hochspannungsdomänengerät ein Dünnoxidgerät ansteuert, das nicht für die Hochspannung ausgelegt ist. Während des Entwurfs versäumt es der Designer, einen High-Low-Level-Shifter einzufügen. Auch wenn dieser Zustand zunächst nicht unbedingt die Funktionalität beeinträchtigt, wird das Dünnoxidgerät im Laufe der Zeit jedoch belastet, was schließlich zu einem Ausfall führt. Die tatsächliche Ausfallzeit hängt vom Spannungswert, der Zeit, in der die Versorgung EIN gegenüber AUS ist, und den Prozessparametern ab.

EM (die Wanderung von Atomen in einem Leiter aufgrund von elektrischem Strom) ist ein weiteres wichtiges Problem, das die langfristige Robustheit von Verbindungen beeinflusst, die in AI/ML-ICs verwendet werden. Diese Migration verursacht die Bildung von Hohlräumen und Hügeln auf den Drähten. Die Hohlräume verursachen eine erhebliche Erhöhung des Widerstands, während die Hügel Kurzschlüsse erzeugen können, die beide zu Stromkreisausfällen führen. Der EM-Effekt hängt von vielen Faktoren ab, wie der Länge und Breite der Metallleitung, dem Verbindungsmaterial, der Betriebstemperatur, unidirektionalen vs. bidirektionalen Strömen usw.

Gießereien bieten Konstruktionsunternehmen EM-Grenzwerte für den maximalen Strom, den die Drähte verarbeiten können, basierend auf den erwarteten Einsatzbedingungen für das Produkt. Beispielsweise wären die EM-Grenzwerte für einen in einem Mobiltelefon verwendeten IC deutlich niedriger als für einen in einer industriellen Umgebung verwendeten IC. Einige Unternehmen haben engagierte Teams, die aktiv mit der Gießerei zusammenarbeiten, um geeignete Spezifikationen zu definieren, Teststrukturen zu erstellen und Produktqualifizierungen für EM-Toleranz durchzuführen. Offensichtlich ist es schwieriger, diese Grenzen für ein Produkt zu definieren, das in mehreren Umgebungen verwendet werden könnte, daher entwerfen Designer diese Chips normalerweise für die ungünstigsten Betriebsbedingungen. In allen Fällen ist es entscheidend, das Design gegen die von der Gießerei definierten EM-Grenzwerte zu testen und zu validieren, dass das Design EM-Effekten standhält.

Das Versäumnis, die verschiedenen Zuverlässigkeitsprobleme während der Pre-Silicium-Verifizierungsphase zu erkennen und zu korrigieren, kann zu einer Vielzahl von Auswirkungen führen, darunter mehrere Tape-Out-Spins, Verzögerungen bei der Markteinführung des Produkts, Verlust des Kundenvertrauens, erhebliche negative Marktreaktionen, Produktrückrufe und sogar katastrophale Folgen wie Körperverletzung oder Verlust des Lebens. Das Identifizieren und Beheben von Zuverlässigkeitsverletzungen vor dem Tape-Out minimiert das Risiko von Schaltungsfehlfunktionen oder Ausfällen, die sich als kostspielig erweisen können.

Analyse und Management der KI/ML-Zuverlässigkeit sind entscheidend

Der jüngste Erfolg und die Erweiterung der KI/ML-Funktionalität basieren weitgehend auf den Fortschritten in der Halbleitertechnologie. Bei der Entwicklung dieser neuen Designs muss sich die Hardware-Design-Community der Notwendigkeit bewusst sein, die Zuverlässigkeitsaspekte eines Designs zu analysieren und zu verwalten, wie z Die spezifischen Zuverlässigkeitsprobleme und Anforderungen dieser großen, komplexen Chips können Designunternehmen dabei helfen, sicherzustellen, dass ihre Produkte während ihrer gesamten Lebensdauer wie beabsichtigt funktionieren. Dies wiederum führt zu Vertrauen in die Ergebnisse, die durch den Einsatz von KI/ML-Anwendungen in den breiteren Märkten erzielt werden, und unterstützt deren fortgesetzte Nutzung und Expansion.

Branchenartikel sind eine Inhaltsform, die es Branchenpartnern ermöglicht, nützliche Nachrichten, Nachrichten und Technologien mit All About Circuits-Lesern auf eine Weise zu teilen, für die redaktionelle Inhalte nicht gut geeignet sind. Alle Branchenartikel unterliegen strengen redaktionellen Richtlinien, um den Lesern nützliche Neuigkeiten, technisches Know-how oder Geschichten zu bieten. Die in Branchenartikeln zum Ausdruck gebrachten Standpunkte und Meinungen sind die des Partners und nicht unbedingt die von All About Circuits oder seinen Autoren.

Internet der Dinge-Technologie

- Die Bedeutung der elektrischen Sicherheit

- Welche Rolle spielt der Zuverlässigkeitsingenieur?

- Der Schlüssel zum Erfolg bei Zuverlässigkeit

- Die Bedeutung von Kernkompetenzen

- Die nicht-technische Seite der Zuverlässigkeit

- Die Bedeutung von Trends bei der Zuverlässigkeit von Elektromotoren

- Die Bedeutung der routinemäßigen Wartung von Geräten

- Die Bedeutung der schnellen Bearbeitung in der Fertigung

- Die Bedeutung der Ursachenanalyse

- Die Bedeutung der Notfallplanung