In-Situ-Aufzeichnungsgerät mit Ladungsteilung (CSIR) zur Echtzeit-Untersuchung des Plasma-Ladeeffekts in FinFET-BEOL-Prozessen

Zusammenfassung

Ein neuartiges Gerät zur Überwachung plasmainduzierter Schäden im Back-End-of-Line (BEOL)-Prozess mit Ladungsteilungsfähigkeit wird erstmals vorgeschlagen und demonstriert. Dieser neuartige Ladungsteilungs-In-Situ-Rekorder (CSIR) kann die Menge und Polarität von Plasmaladungseffekten während des Herstellungsprozesses von fortschrittlichen Fin-Feldeffekttransistor-(FinFET)-Schaltungen unabhängig verfolgen. Es zeigt nicht nur die Echtzeit- und In-Situ-Plasma-Ladepegel an den Antennen an, sondern trennt auch den positiven und negativen Ladeeffekt und bietet zwei unabhängige Messwerte. Da CMOS-Technologien in Zukunft auf feinere Metallleitungen drängen, bietet das neue Ladungstrennungsschema ein leistungsstarkes Werkzeug für die BEOL-Prozessoptimierung und weitere Verbesserungen der Gerätezuverlässigkeit.

Hintergrund

Plasmaunterstützte Prozesse werden häufig bei der Herstellung von Fin-Feldeffekttransistor-(FinFET)-Schaltungen verwendet, die aus vielen Strukturen mit hohem Aspektverhältnis und feinen Metallleitungen bestehen [1]. Während der Herstellung können Ätz- und Abscheidungsschritte zur Realisierung dieser 3D-Zusammensetzungen zu erheblichen plasmainduzierten Belastungen der FinFET-Bauelemente führen [2,3,4]. Mit fortschreitender CMOS-FinFET-Technologie verringern sich die Metalllinienbreite und der Abstand stärker als ihre Höhe, was die Notwendigkeit der Bildung von Gräben mit hohem Seitenverhältnis, die durch extrem feine Linien definiert sind, erhöht. Dies fördert unvermeidlich die Schwere der Plasma-induzierten Schäden (PID) an den Transistoren, und ihre entsprechende Auswirkung auf die Schaltungszuverlässigkeit wird zu einem der Hauptanliegen bei der Entwicklung von FinFET-Technologien [5,6,7]. Beim Bilden kleiner Kontakte, Vias und feiner Metallleitungen werden im Allgemeinen starke Leistung und hochselektives Plasma angewendet [8]. Darüber hinaus kann beim Ätzen der Bulk-Fin das Sputtern von reaktiven Ionen auf der Fin-Oberfläche zu Defekten in der Bulk-Finne führen, die für die Eigenschaften der Transistoren kritisch sind [9]. Um Fin-Metal-Gate- und dichte Verbindungsstrukturen zu ermöglichen, werden in fortgeschrittenen FinFET-Technologien häufiger komplexe Metallstapel verwendet [10, 11]. Außerdem hohe k Gate-Dielektrikum, das in fortgeschrittener Technologie verwendet wird, führt normalerweise zu einem verstärkten spannungsinduzierten Trapping nach dem Plasmaprozess [12,13,14]. Während der Plasmaladung kann der Entladungspfad durch schmale Finnen und zum Substrat zu ungleichmäßigeren Spannungsniveaus über einen ganzen Wafer führen [15]. Es ist bekannt, dass die plasmainduzierte Belastung des Gate-Oxids des Transistors zu einer weiteren Verschlechterung der dielektrischen Integrität des Gates führt [16, 17].

Die plasmainduzierte Beschädigung des Gatedielektrikumsfilms kann in sehr ungleichmäßigen Ladeszenarien zu einer Leistungsverschlechterung führen, sogar zu einem Ertragsverlust [18,19,20] als Folge von Zuverlässigkeitsfehlern [21, 22]. Daher werden bei fortschrittlichen FinFET-Technologien im Allgemeinen Testgeräte mit vergrößerten Antennenstrukturen zur Überwachung von PID-Effekten verwendet, die Rückkopplungen für die weitere Prozessoptimierung liefern.

Das gebräuchlichste und am weitesten verbreitete Maß für PID ist die Time-to-Breakdown-Charakteristik der Testmuster mit großen Antennenstrukturen. Der latente Schaden an diesen PID-Mustern wird typischerweise durch die Messung der zeitabhängigen Degradation der Gatedielektrikumsschichten widergespiegelt, wodurch die Echtzeit-Rückkopplung der Plasmaprozesse nicht gegeben wird [23]. Außerdem können herkömmliche Testgeräte die Quellen und die Polarität der plasmainduzierten Laderate und/oder des maximalen Potentialaufbaus an der Antenne nicht erkennen. In unserer vorherigen Studie wurde ein PID-Rekorder mit einem durch eine Antennenstruktur gekoppelten Floating-Gate mit in-situ-Detektionsfunktion vorgeschlagen [24, 25]. In dieser Arbeit haben wir einen überarbeiteten PID-Rekorder mit einer Ladungsteilungsfunktion vorgeschlagen. Durch eine Vorwärtsdiode und eine Rückwärtsdiode, die mit einer gemeinsamen Antennenstruktur verbunden sind, bietet das neue Design getrennte Pfade für positive und negative Ladungen. Daher können Ladepegel beider Polaritäten unabhängig aufgezeichnet werden. Dieser neue Ladungsteilungs-In-Situ-Rekorder (CSIR), der nur kleine Antennen benötigt, ermöglicht zukünftige Studien des Plasma-Ladeeffekts in Middle-End-of-the-Line-(MEOL)-Prozessen.

Methoden

Plasma-Ladepolarität

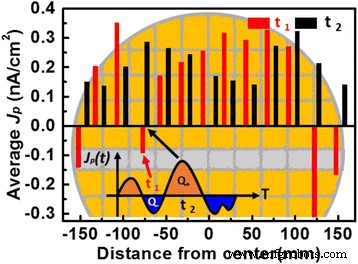

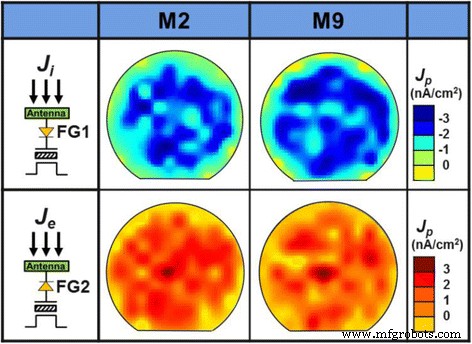

Frühere Studien berichteten, dass beim Ätzprozess bei der Bildung von Poly- oder Metallschichten die Plasmainhomogenität sowie die Variationen des Antennenpotentials zu drastischen Unterschieden in der Laderate oder sogar zu Polaritätsänderungen an verschiedenen Stellen führen können [24, 25]. Sowohl die Makroumgebung in der Plasmakammer als auch Mikromuster können die Verteilung der Ladungsraten auf einem Wafer beeinflussen [26]. Die Plasmaladerate beim Back-End-of-Line-(BEOL)-Ätzen variiert nämlich räumlich und zeitlich. Während der Hochfrequenz-(RF)-Plasmaprozesse sammelt die Oberfläche des Wafers einen Ladestrom, J p , die sich aus einem Ionenstrom J . zusammensetzt ich und ein Elektronenstrom J e [26]. Der Ionenstrom ist zeitlich nahezu konstant und wird durch die Ionendichte J . bestimmt ich und die Böhm-Geschwindigkeit [26]. Da das Plasmapotential V p (t ) ist höher als das Gatepotential V G die meiste Zeit fließt der Elektronenstrom nur während der kurzen Zeiträume, in denen das Plasmapotential nahe seinem Minimum ist. Während Q FG Prozess kann die Gatespannung über viele HF-Zyklen zunehmen oder abnehmen, je nachdem welche Komponente der Ströme größer ist, bis eine stationäre Gatespannung erreicht wird, wenn der Tunnelstrom J . ausgleicht p an der Antenne. Wie in Abb. 1 gezeigt, ist die Verteilung der Plasmaladungsrate J P (x ,y ,t ), über den Wafer während des Ätzprozesses in verschiedenen Stadien Änderungen sowohl in der Größe als auch in den Polaritäten, wo es wie in Gl. (1) wobei J e die Elektronenstromdichte darstellt und J ich repräsentiert die Ionenstromdichte.

$$ {J}_{\mathrm{p}}={J}_{\mathrm{e}}+{J}_{\mathrm{i}}\dots $$ (1)

Verteilung der plasmainduzierten Ladungsrate in der Mittellinie des Wafers während des Ätzprozesses zu verschiedenen Zeitpunkten. Die Polarität der Plasmaladung an einem bestimmten Ort kann sich im Laufe der Zeit ändern

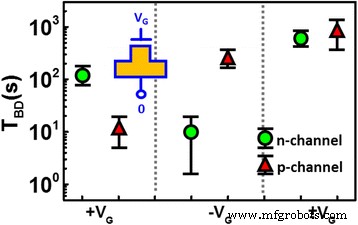

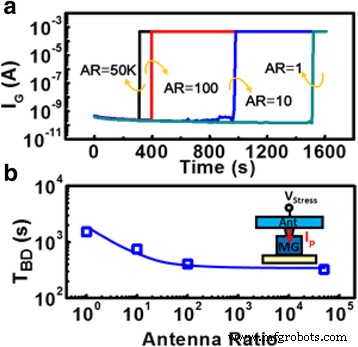

Die unterschiedlichen Polaritäten der Plasmaladung führen entweder zu einer positiven oder negativen Antennenladung, Q P , gesammelt zu einer anderen Zeit und an einem anderen Ort. Zur Klarstellung zum Zeitpunkt t 1 , ein negatives J p führt zu negativer Antennenladung Q −. Bei t 2 , ein positives J p induziert eine positive Antennenladung Q+ an der identischen Stelle auf dem Wafer, wie in 1 dargestellt. Somit kann sich während des Ätzprozesses zu unterschiedlichen Zeiten positive oder negative Ladung an derselben Antenne ansammeln. Aus früheren Berichten [27] wurden die Spitzenwerte von J e und J ich liegen bei − 0,15 und 0,35 mA/cm 2 , bzw. Es wurde festgestellt [28, 29], dass DC- und AC/bidirektionaler Gate-Belastung auf n-Kanal- und p-Kanal-FinFET zu unterschiedlichen latenten Schäden am Gatedielektrikumsfilm führt. An konventionelle FinFET-Testproben werden hohe Spannungsbelastungen mit positiver oder negativer DC-Bias bzw. AC-Spannung mit einer Schaltfrequenz von 0,1 Hz angelegt. Wie in Abb. 2 gezeigt, ist die Zeit bis zum Zusammenbruch (T BD ) eines Transistors, der durch positive, negative und Gate-Spannung in beiden Richtungen belastet wird, verglichen. Die Ergebnisse deuten darauf hin, dass die Belastung des DC-Gates die Proben stärker beschädigt, während die Belastung des AC-Gates zu weniger schweren Schäden an diesen Transistoren führt, wie die längere T . andeutet BD für Proben, die bidirektionalen Belastungen ausgesetzt sind. Abbildung 2 zeigt auch, dass die Oxiddegradation nicht nur von der Ladepolarität abhängt, sondern auch von der Art der Wannen unter den n-Kanal- und p-Kanal-Transistoren, die vermutlich durch die unterschiedlichen Entladepfade dieser Tests verursacht werden Geräte während des Prozesses. Daher herkömmlicher PID-Detektor, der T . verwendet BD da der Indikator für die Schadensschwere die Plasmaladung während des Prozesses nicht widerspiegeln kann. Andererseits zeichnet der in unserer früheren Arbeit vorgeschlagene Plasma-Laderekorder den Spannungspegel auf, indem er Elektronen zu/von einem schwebenden Gate (FG) injiziert oder ausstößt, das durch eine ladungssammelnde Antenne gekoppelt ist. Die aufgezeichneten Daten, Floating-Gate-Ladung (Q FG ), wird nach der Herstellung gelesen [24, 25]. Die Aufzeichnung wird dann durch die Schwellenspannungsverschiebung am Lesetransistor gemessen, dessen Kanal von demselben schwebenden Gate gesteuert und geleitet wird. Das erhöhte Potential an der Antenne mit Q P durch Plasmaladung kann während der Bildung einer einzelnen Metallschicht sowohl eine positive als auch eine negative Antennenspannung induzieren. Außerdem werden für unterschiedliche Metallschichten unterschiedliche Herstellungsparameter verwendet. Beispielsweise können die Ätzzeit, die verwendete Chemikalie und die Kammertemperaturen variieren. Diese Parameter können die Antennenladungsverteilung über einen Wafer während des Ätzens beeinflussen. In anderen Fällen unterliegt ein Transistor mit Verbindungen zu mehreren Metallschichten noch komplexeren Plasmaladesequenzen, wie in Abb. 3a dargestellt.

Zeit bis zum Zusammenbruch (T BD ) von n-Kanal- und p-Kanal-FinFETs, die durch positive, negative und positive + negative Ladung an den Gate-Elektroden belastet werden. T BD von Geräten mit unterschiedlichen Polaritätsbelastungen legt nahe, dass der auf dem Gate-Dielektrikum akkumulierte Schaden nicht nur von der Ladepolarität, sondern auch von den Wells unter den entsprechenden FinFETs abhängt

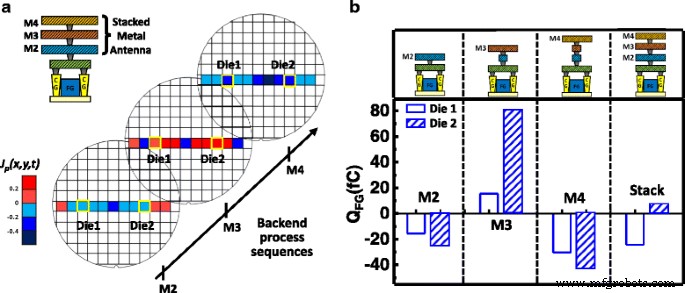

a Der Plasmaladeeffekt für die verschiedenen Metallschichten variiert an verschiedenen Stellen über den Wafer. b Die positiven und negativen Ladungen können sich in den gestapelten Metallschichten gegenseitig kompensieren

In verschiedenen Stadien des BEOL-Prozesses kann der Plasmaladestrom an einer bestimmten Antenne zwischen Ionen- und Elektronenstrom umschalten, d. h. das Netto Q P kann auch von positiv zu negativ wechseln. Die Aufnahmen an Proben mit Antenne bestehend aus Metall 2, Metall 3, Metall 4 und mehreren Metallschichten sind in Abb. 3b zusammengefasst. Die Daten deuten auf eine Nettoladung einer einzelnen Metallschicht [24] bei einer bestimmten Änderung der Polarität von Schicht zu Schicht hin. Darüber hinaus ist der Mittelungseffekt des Q FG der Proben mit Antennenstrukturen aus mehreren Metallschichten wird durch die Messdaten in Abb. 3b weiter unterstützt. Sowohl mit positivem als auch mit negativem V G auf der Antenne das letzte Q FG wird dann durch Elektroneninjektion und Elektronenemission in/aus dem FG, die sequentiell erfolgen können, herausgemittelt. Dieser Kompensationseffekt begrenzt den Rekorder, um die realen Stressbedingungen anzuzeigen, denen ein Gerät während Plasmaprozessen ausgesetzt ist. Das überarbeitete CSIR soll das Problem angehen, positive und negative Aufladungseffekte einzeln störungsfrei zu erfassen und detailliertere Daten zur Aufladungssituation in der Plasmakammer liefern.

Testmuster für Ladungstrennung

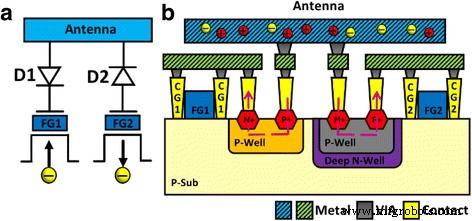

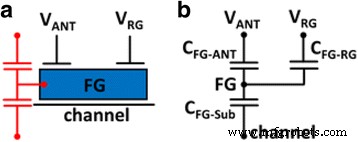

In dieser Forschung kann die positive Ionenladung und die negative Elektronenladung an der Antenne mit einem neuen vorgeschlagenen Ladungsteilungs-In-situ-Rekorder (CSIR) getrennt werden, wie in Abb. 4a dargestellt. Ein CSIR besteht aus zwei Floating-Gates, FG1 und FG2 die die unterschiedlichen Ladewirkungsarten getrennt aufzeichnen. Die Antennenstruktur ist über eine Vorwärtsdiode (D1) bzw. eine Rückwärtsdiode (D2) mit den beiden Koppelgates verbunden. In der linken Hälfte der Struktur fließen die positiven Ladungen in das Kopplungsgatter 1 (CG1 ) bis D1. Wenn CG1 positiv geladen ist, wird die Spannung über die Kontaktschlitze auf beiden Seiten an das Floating Gate gekoppelt. Das Floating Gate wird negativ geladen, wenn Elektronen vom Substrat injiziert werden. Die rechte Hälfte der Struktur hingegen ist der negative Ladepfad, wodurch Strom von der Antenne in das Kopplungsgatter 2 fließen kann (CG2 ) bis D2, was zu positivem Q . führt FG . Abbildung 4b zeigt ferner die Querschnittsansicht des CSIR mit On-Chip-pn-Dioden, die die positiven und negativen Ladepfade zu den separaten Kopplungsgates CG1 . leitet und CG2 , die das Potential an der Antenne an den FG1 . koppeln und die FG2 , bzw.

a In-situ-Aufzeichnungsgerät zur Ladungsteilung mit zwei getrennten Floating-Gates durch Anschließen an eine Vorwärtsdiode (D1) und eine Rückwärtsdiode (D2) zum Erfassen der Elektronen-/Ionen-Ladung. b Querschnittsdarstellung des neuen Ladungsteilungs-In-Situ-Rekorders mit On-Chip-pn-Dioden, der die positive und negative Ladung zu den getrennten Kopplungsgates leitet, CG1 und CG2

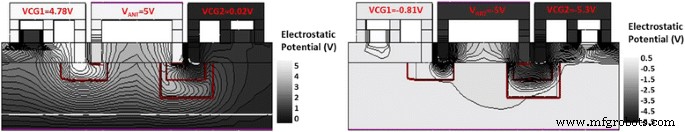

Wenn die linke Hälfte des Rekorders im CSIR unter einer positiv geladenen Antenne aktiviert ist, ist die rechte Hälfte inaktiv, da die Ladung durch die Sperrdiode blockiert wird und umgekehrt. Beide On-Chip-Dioden bestehen aus einer n+/p-Wanne. Damit D2 eine negative Spannung in seiner p-Wanne aufrechterhalten kann, muss die p-Region von einer tiefen n-Wanne umgeben sein, die den Ladepfad direkt zum Substrat blockiert. Die simulierte Potentialverteilung auf dem Querschnitt in einem CSIR unter positiven und negativen Ladeperioden der Antenne ist in Abb. 5a bzw. b gezeigt. Unter der Annahme, dass das Potenzial an einer Antenne 5 V erreicht, fließt durch die Diode links positive Ladung zum Steuergate links, was zu einer hohen positiven Spannung (V CG1 ). Gleichzeitig wird positive Ladung durch die Diode rechts blockiert, was zu einem V . nahe Null führt CG2 . Die Potentialdifferenz an den beiden Steuergates wird durch die simulierten Potentialkonturen in Fig. 5a verifiziert. Die Auswirkung negativer Aufladung auf die Antenne ist in Abb. 5b dargestellt. Simulierte Potenzialprofile verifizieren, dass die pn-Dioden auf dem Chip das Potenzial effektiv zu CG1 . leiten und blockieren können und CG2 , kostenlos, wie vorgesehen. Auf diese Weise können unabhängig voneinander positive und negative Ladungseffekte erzielt werden, die verschiedenen Quellen bei der Plasmabehandlung entsprechen, wodurch Ladungskompensation und Interferenzprobleme am Detektor vermieden werden.

Simulierte Potentialverteilung im CSIR mit positiver und negativer Antennengatespannung. Die Vorwärts- und Rückwärts-pn-Dioden trennen erfolgreich die Antennenladungspolarität

Ergebnisse und Diskussion

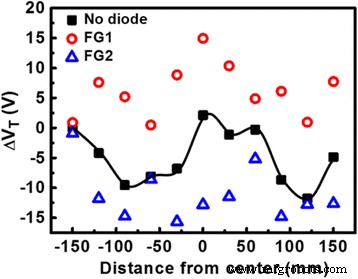

Die gemessene Schwellenspannungsverschiebung (ΔV T ) auf einem von FG1 gesteuerten Gerät mit Durchlassdiode und das von FG2 mit Sperrdiode und Proben ohne Diode sind in Fig. 6 verglichen. Daten entlang der Mittellinie eines Wafers zeigen, dass ein Recorder mit einem einzelnen Floating-Gate selbst innerhalb der Verarbeitung einer einzelnen Metallschicht einer Ladungsneutralisation unterliegt. Der Mittelungseffekt eines Rekorders ohne Diode beweist, dass die Spitzenladeraten nicht wahrheitsgetreu wiedergegeben werden. Andererseits können die Messwerte des neuen CSIR unabhängig voneinander positive und negative Ladepegel liefern. Um den Plasmaladungseffekt bei der Bildung von Metall 2 (M2) weiter zu untersuchen, wurde die gesammelte Ladung auf FG1 und FG2 des CSIR jedes Chips kann unabhängig durch Gl. (2),

$$ {Q}_{\mathrm{FG}}={C}_{\mathrm{T}}\times \Updelta {V}_{\mathrm{T}}\times {\alpha}_{\mathrm {RG}}\dots $$ (2)wo Q FG ist die Ladung im Floating Gate. C T ist die Gesamtkapazität des Floating Gates, wie in Abb. 7 dargestellt. ΔV T ist die Schwellenspannungsverschiebung, die am Lesegate des Rekorders erkannt wird, während α RG ist das Kopplungsverhältnis vom Lesetor.

Verteilung von Delta V T auf FG1 mit Durchlassdiode und FG2 mit Sperrdiode und FG ohne Diode entlang der Mittellinie eines Wafers

a Das schematische Diagramm eines Kapazitätsnetzwerkmodells in einem CSIR-Gerät. b Die Gesamtkapazität des Floating Gate besteht aus allen genannten Kapazitäten in Reihe plus der parallel

Wenn die Floating-Gate-Ladung anfänglich null ist und Q FG den Sättigungspegel erreicht, wenn das elektrische Feld über der dielektrischen Gate-Schicht auf Null reduziert wird, kann das endgültige Antennen-Gate-Potential am Ende eines Plasmaprozesses wie folgt ausgedrückt werden:

$$ {V}_{\textrm{ANT}}=\frac{V_{\textrm{FB}}-\frac{Q_{\textrm{FG}}}{C_{\textrm{T}}}}{ \alpha_{\mathrm{ANT}}}\dots $$ (3)wobei V ANT ist das Antennen-Gate-Potential durch Plasmaladung und α ANT repräsentiert das Kopplungsverhältnis zum Floating-Gate vom Antennen-Gate. V FB ist die Flachbandspannung vom Metallgate zum Finnensubstrat. Bei einer gegebenen Prozesszeit beträgt die durchschnittliche Plasmaladestromdichte J p kann dann durch Gl. (4).

$$ {J}_{\mathrm{p}}=\frac{V_{\mathrm{ANT}}\times {C}_{\mathrm{ANT}}}{A_{\mathrm{ANT}}\times \Delta t}\dots $$ (4)wo Δt ist die Dauer eines Plasmaprozesses [28, 29] und C ANT ist die Gesamtkapazität der Metallantenne, während A ANT ist der Ladebereich einer Antenne. Alle in den obigen Berechnungen verwendeten Parameter sind in Tabelle 1 zusammengefasst.

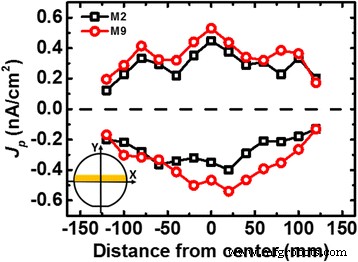

Die Verteilung der positiven und negativen Ladungsraten über einen Wafer während der Verarbeitung der oberen (Metall 9) und unteren Metallschichten (Metall 2) wird in Abb. 8 weiter verglichen. Dies impliziert, dass die Ladung auf der Antennenstruktur bei höheren Metallen stärker ausgeprägt ist Niveaus (Metall 9), denn auf Metall 9 verursacht seine höhere Plasmaenergie J p größer als J . sein p von Metall 2 in Bezug auf die Größe. Außerdem legen die Daten nahe, dass sowohl die Elektronen- als auch die Ionenladeraten in beiden Fällen um das Zentrum herum ihren Höhepunkt erreichen. Die zur Wafermitte hin geschlossenen Chips erfahren erwartungsgemäß ein hohes Ladungsniveau, was auf den längeren Entladungsweg während der Plasmabehandlung zurückzuführen ist. Es wurde gefunden, dass dieser Lokalisierungseffekt sowohl für Bedingungen mit stärkerer Elektronen- als auch für Ionenladungsdominantere identisch ist. Die projizierte Plasmaladerate, J P (x,y ), gemittelt über die Bildung einer einzelnen Metallschicht, Metall 2 (M2) und Metall 9 (M9), werden in Fig. 9 weiter verglichen. Diese Waferkarten zeigen, dass die Elektronenladungsrate außer an den Rändern auf einem Plateau zu sein scheint , während die Ionenladeraten im mittleren Abschnitt des Wafers eine stärkere Variation zeigten. Zukünftig sollen diese Wafermaps unter unterschiedlichen Prozessbedingungen Einblicke in die Plasmakammer oder weitere Optimierungsrichtlinien durch eine bessere Kompensation der Aufladungseffekte liefern.

Vergleich der positiven und negativen Ladungsrate in der Mittellinie eines Wafers für Metall-2- und Metall-9-Prozesse. Die Ladungsraten sind um das Zentrum herum am höchsten, was bedeutet, dass die plasmainduzierten Schäden in der Mitte des Wafers schwerwiegender sind

Die projizierte Elektronen- und Ionen-Ladungsrate, J e (x ,y ) und J ich (x ,y ) werden von den ladungsteilenden Aufzeichnungsgeräten über die Ätzfläche während der Bildung von Metall 2 Metall 9 erhalten

Antennenverhältniseffekt

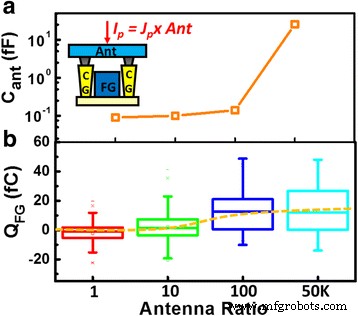

Herkömmliche PID-Überwachungsgeräte sind in der Regel so konzipiert, dass sie den PID-Effekt verstärken, indem sie die Gates des Transistors direkt mit einer großen Antenne verbinden und die Belastungsniveaus durch Erhöhung des Gesamt-Q . bewerten P erwartet, durch eine kleine Kanalregion entladen zu werden [30, 31]. Das Antennenverhältnis (AR) ist proportional zur Spannungsstromdichte durch das Gatedielektrikum während Plasmaprozessen [32]. Großes Q P auf der Antenne ist dafür bekannt, latente Schäden und/oder Fallen in der dielektrischen Schicht zu induzieren, die letztendlich zu einer Verschlechterung der Zuverlässigkeit führen [33]. Wie erwartet, erhöht eine höhere AR bei herkömmlichen FinFETs die Stresspegel erheblich, was zu einer stärkeren TBD . führt Verschlechterung, d. h. Geräteausfall innerhalb einer kürzeren Betriebsdauer, siehe Abb. 10. Andererseits wird in einem CSIR der Plasmaladepegel als Floating-Gate-Ladung aufgezeichnet, Q FG , zeigt einen sehr geringen Antenneneffekt. Es reagiert nämlich nicht auf eine zunehmende Antennenfläche, wie aus den in Fig. 11 zusammengefassten Daten hervorgeht

a Die Zeit-bis-Zusammenbruch-Eigenschaften I G gegenüber der Zeit der herkömmlichen PID-Detektoren mit zunehmender Antennengröße. b T BD nimmt drastisch ab, wenn AR 1000 überschreitet

a Wenn die Kapazität der Antenne zunimmt, V CG wird unabhängig von der AR. b Q FG gesättigt, wenn der AR 100× überschreitet

Beim neuen CSIR auf Floating-Gate-Basis beeinflusst das Antennenverhältnis (AR) das Spitzenpotential an den Kopplungsgates während des Plasmaladens. Bei skalierten Technologien wird erwartet, dass sich die parasitären Kapazitäten an der Verbindungs- und Kopplungsstruktur verringern, was zu einer geringeren AR-Empfindlichkeit der Aufzeichnungsergebnisse führt. Die Gründe, die zu einem so offensichtlichen Unterschied des AR-Effekts zwischen CSIR und herkömmlichen Detektoren führen, sind wie folgt. Bei diesen Floating-Gate-Recordern wird die auf der Antenne angesammelte Ladung Q P wird nicht durch den Kanalbereich abgeführt. Q . erhöht P erhöht V CG , was zu einer Elektroneninjektion oder -ejektion in/aus den Floating-Gates führt. Wie in der simulierten Kapazität in Abb. 11a gezeigt, ist die Kapazität der Antenne C Ameise , steigt proportional zur Antennenfläche, A Ameise . Da der Gesamtladestrom direkt proportional zur Antennenfläche ist, beeinflusst ein erhöhter AR in einem CSIR das Potenzial an der Antenne nicht. Messdaten zeigen, dass das Q FG das Niveau bleibt für SCIR mit AR über 100× ungefähr gleich.

Diese Funktion spart nicht nur den Testmusterbereich, sondern ermöglicht auch das Auffinden von J P (x ,y ) mit höherer räumlicher Auflösung zur Untersuchung des Mustereffekts auf PID. Außerdem kann ein Detektor mit kleiner Antenne das Design von Testmustern zum Verständnis von PID in Middle-End-of-the-Line (MEOL) und Kontaktprozessen erleichtern.

Schließlich ist in Tabelle 2 eine Leistungszusammenfassung des neuen CSIR zur Überwachung von PID in einem fortschrittlichen BEOL-FinFET-Prozess zusammengefasst. Der Erfassungsbereich des traditionellen Detektors ist AR, während der Erfassungsbereich des neuen In-Situ-Rekorders auf der Floating-Gate-Länge basiert. Außerdem kann die Fläche neuer In-Situ-Rekorder sehr klein sein. Am wichtigsten ist, dass das neue CSIR das Echtzeit-Feedback des Plasmaprozesses und separate Ebenen der Ionenladung und der Elektronenladungsrate unabhängig voneinander bereitstellen kann.

Schlussfolgerungen

Ein neuartiger In-Situ-Rekorder mit Ladungsaufspaltung (CSIR) zur Überwachung plasmainduzierter Schäden wird erstmals vorgeschlagen und demonstriert. Das CSIR bietet ein leistungsstarkes Werkzeug zum gleichzeitigen Verständnis der Elektronenladungs- und Ionenladungsraten in einer Plasmakammer. Wafer-Maps können weitere Untersuchungen zwischen der Korrelation zur Gerätezuverlässigkeit und diesen individuellen Ladeeffekten erleichtern.

Änderungsverlauf

Nanomaterialien

- Zebrafisch:Ein vielversprechendes Echtzeit-Modellsystem für die nanotechnologisch vermittelte neurospezifische Wirkstoffabgabe

- Substitutionsdoping für Alumosilikat-Mineral und überlegene Wasserspaltungsleistung

- Folatrezeptor-gerichtete Bioflavonoid-Genistein-beladene Chitosan-Nanopartikel für eine verbesserte Antikrebswirkung bei Gebärmutterhalskrebs

- Die Wirkung von Kontakt-Nichtgleichgewichtsplasma auf die strukturellen und magnetischen Eigenschaften von Mn Х Fe3 − X О4 Spinellen

- Auswirkung einer In-situ-Annealing-Behandlung auf die Mobilität und Morphologie von TIPS-Pentacen-basierten organischen Feldeffekttransistoren

- In-situ-Synthese von bimetallischen Wolfram-Kupfer-Nanopartikeln durch thermisches Hochfrequenzplasma (RF)

- Elektrisch feldunterstützte präzise In-situ-Abscheidung von elektrogesponnenen γ-Fe2O3/Polyurethan-Nanofasern für magnetische Hyperthermie

- In-situ-Elektrospinnen von Jod-basierten Fasernetzen für antibakterielle Wundverbände

- Ein tragbarer triboelektrischer Nanogenerator zur Überwachung der Atmung in Echtzeit

- ReS2 Charge Trapping Synaptic Device für Gesichtserkennungsanwendung