Die Optimierung der Programmierung von kapazitiven 1T DRAM basierend auf dem Dual-Gate-TFET

Zusammenfassung

Das größere Volumen des Kondensators und der höhere Leckstrom des Transistors sind zu den inhärenten Nachteilen des traditionellen dynamischen Direktzugriffsspeichers (DRAM) mit einem Transistor (1T) und einem Kondensator (1C) geworden. In letzter Zeit wird der Tunnel-FET (TFET) aufgrund des geringen Sperrstroms und des hohen Schaltverhältnisses in DRAM-Zellen verwendet. Die Dual-Gate-TFET (DG-TFET) DRAM-Zelle mit kondensatorloser Struktur hat die überlegene Leistung – höhere Retentionszeit (RT) und schwache Temperaturabhängigkeit. Aber die Leistung einer TFET-DRAM-Zelle hängt von der Programmierbedingung ab. In diesem Papier wird die Richtlinie zur Programmierungsoptimierung ausführlich mit dem Simulationstool Silvaco Atlas diskutiert. Sowohl die Schreib- als auch die Leseoperationen des DG-TFET-DRAM hängen vom Band-zu-Band-Tunneln (BTBT) ab. Während des Schreibvorgangs werden die Löcher, die von BTBT stammen, der von Gate2 gesteuert wird, in einer Potentialmulde unter Gate2 gespeichert. An Gate2 wird eine kleine negative Spannung angelegt, um Löcher für lange Zeit zu halten, während „1“ gehalten wird. Der von Gate1 gesteuerte BTBT beeinflusst hauptsächlich den Lesestrom. Unter Verwendung der optimierten Programmierbedingungen erhält der DG-TFET-DRAM das höhere Stromverhältnis zwischen dem Lesen von „1“ und dem Lesen von „0“ (10 7 ) und RT von mehr als 2 s. Die höhere RT reduziert die Bildwiederholfrequenz und den dynamischen Stromverbrauch des DRAM.

Hintergrund

Der dynamische Direktzugriffsspeicher (DRAM) ist zu einer integralen Speicherzelle im Mobil- und Computersystem geworden [1, 2, 3]. Mit der Schrumpfung der Bauelementgeometrien ist das große Kondensatorvolumen ein inhärenter Nachteil für die herkömmliche DRAM-Zelle mit einem Transistor (1T) und einem Kondensator (1C), was ihre großflächige Anwendung einschränkt. Die kondensatorlose 1T-DRAM-Zelle auf Basis des Floating-Gate-Transistors hat den potentiellen Vorteil gegenüber dem herkömmlichen 1T-1C-DRAM für das High-Density-Packaging von Speicher gezeigt [4]. Beim Floating-Gate-Transistor werden die Ladungen im Substratbereich durch das Fowler-Nordheim-Tunneln im Floating-Gate-Bereich gespeichert. Und der Lesevorgang hängt von der thermionischen Emission ab [5, 6], die dem Metall-Oxid-Halbleiter-Feldeffekttransistor (MOSFET) entspricht. Dadurch weist der Lesestrom des DRAM mit Floating-Gate-Transistor eine starke Temperaturabhängigkeit auf. Darüber hinaus führt die thermionische Emission dazu, dass der unterschwellige Hub (SS) des Transistors höher als 60 mV/dez ist, wodurch der hohe Leckstrom und der Stromverbrauch zu den größten Herausforderungen werden [7,8,9].

In letzter Zeit wurde der Tunnel-Feldeffekttransistor (TFET) als vielversprechender Kandidat für zukünftige elektrische Geräte mit geringer Leistung angesehen [10,11,12]. Der Hauptleitungsmechanismus von TFET ist das Band-zu-Band-Tunneln (BTBT) anstelle der thermionischen Emission, wodurch mehrere Vorteile erzielt werden, wie z [13, 14]. Bisher konzentrierten sich große Forschungsarbeiten zu TFET hauptsächlich auf die Untersuchung der Geräteleistung einzelner TFETs und einige einfache Schaltungen bestehen aus den TFETs. Das hohe I an /Ich aus des TFET ermöglicht es, für die DRAM-Zelle zu dienen [15]. Insbesondere kann der niedrige Leckstrom im Sperrzustand den Lesestrom „0“ und den Stromverbrauch der DRAM-Zelle reduzieren. Die Forscher haben einen Dual-Gate-TFET (DG-TFET)-DRAM mit kondensatorloser Struktur entworfen [16]. Beim DG-TFET DRAM basiert die Ladungsspeicherung während des Schreibvorgangs auf dem BTBT zwischen Kanal und Drain, der hauptsächlich von Gate2 erzeugt wird. Gleichzeitig fördert das Tunneln von Elektronen die Ansammlung von Löchern im Kanalbereich unter Gate2. Gate1 ist hauptsächlich für den Lesebetrieb zuständig. Der Lesestrom des DGTFET DRAM beruht hauptsächlich auf dem BTBT zwischen dem Source-Bereich und dem Kanalbereich. Es gibt einige Forschungsgruppen, die gezeigt haben, dass der Lesestrom von DG-TFET-DRAM eine schwache Abhängigkeit von der Temperatur hat. Und DG-TFET-DRAM kann eine Retentionszeit erreichen, die höher ist als die Zielvorgabe (64 ms) [17]. Aber das aktuelle Verhältnis von Messwert „1“ zu Messwert „0“ und RT ist aufgrund der nicht optimierten Programmierbedingungen nicht der optimale Wert.

Die Leistung von TFET-DRAM, insbesondere das Stromverhältnis zwischen dem Lesen von „1“ und dem Lesen von „0“, hängt stark von der Programmierbedingung ab. Gate2 beeinflusst hauptsächlich den BTBT während des Schreibvorgangs, der den Speicherbereich von Ladungen und Potentialmulden unter Gate2 dominiert. Gate1 regelt den BTBT während des Lesevorgangs, was hauptsächlich den Lesestrom „1“ beeinflusst. Die richtigen Vorspannungen von Gate1 und Gate2 können dazu führen, dass DGTFET-DRAM das höhere Stromverhältnis erhält. Es gibt ein wenig Literatur, die den Einfluss der Programmierbedingungen auf den Lesestrom untersucht. In diesem Papier wird eine detaillierte Richtlinie zur Optimierung der Programmierung vorgeschlagen, einschließlich Schreib-, Halte- und Leseoperationen. Durch Anwenden der optimierten Programmierbedingungen erhält der DG-TFET DRAM die optimale Leistung – das Lesestromverhältnis von bis zu 10 7 und die RT von mehr als 2 s. Und bei Anwendung der optimierten Programmierspannung ist der Strom „0“ viel niedriger als in Referenz [16, 18] angegeben, was für die Reduzierung des Stromverbrauchs hilfreich ist.

Methoden

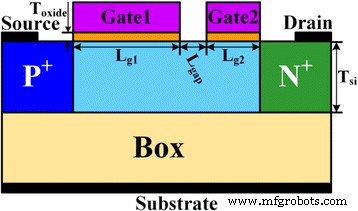

Die in dieser Arbeit untersuchte Struktur des DG-TFET ist in Abb. 1 dargestellt. Die Dotierungskonzentration der beiden P + Quelle und N + Abfluss beträgt 1 × 10 20 /cm 3 . Der intrinsische Kanal ist in zwei Segmente unterteilt:Gate1 und Gate 2, und zwischen Gate1 und Gate2 besteht eine kurze Lücke. Gate1 und Gate2 sind N + Polysilizium und P + Polysilizium bzw. Das P + Polysilizium-Gate2 kann die physikalische Quelle für die Ladungsspeicherung erstellen und beibehalten und den herkömmlichen TFET-basierten DRAM ersetzen, der ein P + . verwendet Taschenbereich als Speicherbereich. Während für ein N + Polysilizium Gate1 ist die Lochkonzentration im Unterlappungsbereich zwischen Gate1 und Gate2 gering, was für den Lesevorgang hilfreich ist. Also ein P + Polysilizium Gate2 hat einen tieferen Speicherbereich, der eine längere Retention ermöglichen könnte, während ein N + Polysilizium-Gate1 wird ausgewählt, um den Tunnelmechanismus während des Lesevorgangs zu steuern [18].

Schema einer DG-TFET DRAM-Zelle. Diese Abbildung zeigt das Schema einer Dual-Gate-TFET (DGTFET)-DRAM-Zelle, einschließlich Gate1, Gate2, Source, Drain und Kanal. In diesem Design sind die Source-Region und die Drain-Region P + Doping und N + Doping bzw. Gate1 und Gate2 sind N + Polysilizium und P + Polysilizium bzw.

Die detaillierten Geräteparameter in den Simulationen sind wie folgt:die Dicke des Bulk-Siliziums (T si ) beträgt 20 nm; die Länge von Gate1 (Lg1 ) und Gate2 (Lg2 ) sind 400 nm bzw. 200 nm; die Länge der Lücke (L Lücke ) zwischen Gate1 und Gate2 beträgt 50 nm; die Dicke des Gateoxids (HfO2 ) (T Oxid ) beträgt 3 nm. Die optimierten Programmierbedingungen sind in Tabelle 1 aufgeführt. Die Optimierungsrichtlinien der Programmierbedingungen werden in den folgenden Abschnitten ausführlich diskutiert.

Die gesamte Analyse wird im Silvaco-Atlas-Tool unter Verwendung des nichtlokalen BTBT-Modells durchgeführt [19]. Der nichtlokale BTBT berücksichtigt die nichtlokale Erzeugung von Elektronen und Löchern, sodass er Tunnelprozesse genauer modellieren kann. Die Tunnelmodellparameter werden gemäß den experimentellen Daten in der Referenz [20] kalibriert. Darüber hinaus werden auch physikalische Modelle wie Shockley-Read-Hall-Rekombination, Fermi-Statistik sowie Dotierung und elektrische feldabhängige Mobilität verwendet. Nach den Ansätzen von [16, 18] werden die Elektronen- und Lochlebensdauern auf 100 ns festgelegt. Die Standardtemperatur beträgt 300 K.

Ergebnisse und Diskussion

Das Funktionsprinzip der DG-TFET-DRAM-Zelle unterscheidet sich von dem des herkömmlichen DRAM. Sowohl der Schreib- als auch der Lesevorgang basieren auf dem BTBT, aber jeder von ihnen hat eine andere Funktion. Der BTBT während des Schreibens von „1“ führt dazu, dass die Löcher in der Potenzialmulde unter Gate2 gespeichert werden, die den Lesestrom „1“ erhöhen können. Während des Lesevorgangs hängt der Drainstrom hauptsächlich vom BTBT nahe der Sourceseite ab. Darüber hinaus fungieren die beiden Gates auch als unterschiedliche Rollen:Gate1 und Gate2 bestimmen hauptsächlich den Lese- bzw. Schreibvorgang.

Schreibvorgang

Während des Schreibens von „1“ verstärkt Gate2 mit der negativen Vorspannung das Energieband des Kanals unter Gate2, was die Barrierenbreite verringert und den BTBT zwischen Kanal und Drain erzeugt. Und diese negative Gate2-Vorspannung induziert auch eine tiefe Potentialmulde unter Gate2. Aufgrund des Tunnelns von Elektronen vom Kanal zum Drain wird der Kanalbereich unter Gate2 vollständig verarmt und viele Löcher sammeln sich in diesem Potentialtopf an. Während des Schreibens von "0" bewirkt Gate2 mit der positiven Vorspannung, dass sich die Löcher aus der Potentialmulde ausstoßen, die an der Drain-Seite rekombiniert [21].

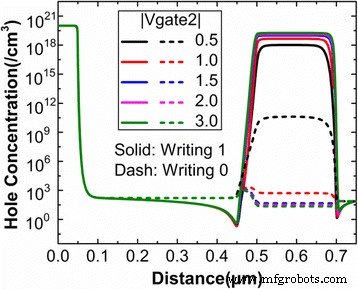

Im Allgemeinen bleibt der Absolutwert der Gate2-Spannung beim Schreiben von „1“ und Schreiben von „0“ unverändert. Abbildung 2 zeigt die Variation der Lochkonzentration mit der Gate2-Spannung nach dem Schreibvorgang. Wenn die Gate2-Spannung 0,5 V beträgt, ist die Lochkonzentration nach dem Schreiben von „0“ aufgrund des Vorhandenseins einer Potenzialmulde höher, was für den Zustand „0“ nachteilig ist. Wenn der Absolutwert der Gate2-Spannung höher als 1 V ist, weist die Lochkonzentration sowohl nach dem Schreiben von „0“ als auch nach dem Schreiben von „1“ keine offensichtliche Variation auf. Es deutet darauf hin, dass BTBT für das Schreiben von „1“ gesättigt ist und dass alle beim Schreiben von „1“ angesammelten Löcher nach dem Schreiben von „0“ aus dem Potentialtopf ausgestoßen werden. Und der Unterschied der Lochkonzentration zwischen dem Schreiben von „1“ und dem Schreiben von „0“ ist sehr offensichtlich, was für die Unterscheidung zwischen dem Zustand „1“ und dem Zustand „0“ von Vorteil ist.

Lochkonzentrationen auf der Oberfläche des Kanals nach dem Schreibvorgang. Diese Abbildung zeigt die Variationen der Lochkonzentration mit den verschiedenen Gate2-Spannungen. Die Schnittlinie verläuft an der Oberfläche des Bauelements vom Sourcebereich zum Drainbereich. In dieser Figur stellen die durchgezogene Linie und die gestrichelte Linie die Lochkonzentration dar, nachdem „1“ bzw. „0“ geschrieben wurde

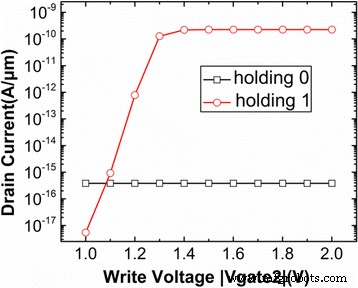

Aber die Gate2-Vorspannung während des Schreibvorgangs kann nicht nur durch die Lochkonzentration bestimmt werden. Abbildung 3 zeigt, dass die Gate2-Vorspannung während des Schreibvorgangs den signifikanten Einfluss auf den Drainstrom nach dem Haltevorgang hat. Die Einstellung der Programmierspannung während des Haltevorgangs wird im nächsten Abschnitt besprochen. Abbildung 3 zeigt, dass der Drain-Strom nach dem Haltevorgang keine offensichtliche Variation aufweist, wenn der Absolutwert der Schreibspannung höher als 1,3 V ist. Daher werden -1,3 und 1,3 V als optimale Gate2-Spannung während des Schreibens von "1" und . angesehen „0“ schreiben.

Drainstrom des DG-TFET nach dem Halten von „0“ und Halten von „1“. Diese Abbildung zeigt die Variation des Drainstroms nach dem Halten von „0“ und dem Halten von „1“ in Bezug auf die Schreibspannung

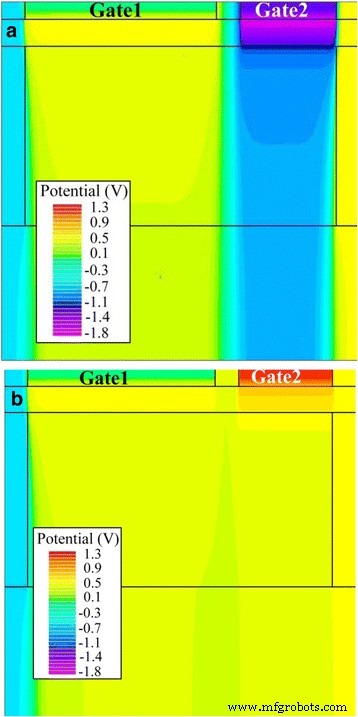

Abbildung 4a, b zeigt jeweils die Potentialkontur nach dem Schreiben von „1“ und Schreiben von „0“, wenn der Absolutwert der Schreibspannung 1,3 V beträgt. Offensichtlich wird nach dem Schreiben von „ 1”, wie in Abb. 4 a gezeigt. Die angesammelten Löcher bleiben während des Schreibens von „1“ in dieser Potentialmulde erhalten. Die angesammelten Löcher entweichen jedoch während des Schreibens von „0“ aus dieser Potentialmulde.

Mögliche Konturen nach a Schreiben von „1“ und b Schreiben von „0“, wenn der Absolutwert der Gate2-Spannung 1,3 V beträgt. a , b Die möglichen Konturen nach dem Schreiben von „1“ bzw. dem Schreiben von „0“. Die Potenzialkonturen in dieser Abbildung werden extrahiert, wenn der Absolutwert der Gate2-Spannung auf 1,3 V eingestellt ist

Haltevorgang

Der Halteprozess wird hauptsächlich verwendet, um die Zurückhaltung der Gebühren zu ändern. Üblicherweise wird die Nullvorspannung während des Haltevorgangs verwendet, um den Stromverbrauch zu reduzieren [22]. Während des Haltevorgangs werden die angesammelten Löcher im potentiellen Bohrloch aufgrund der Verringerung der potentiellen Bohrlochtiefe allmählich wieder kombiniert. Daher besteht der Hauptzweck der Optimierung des Haltevorgangs darin, eine Rekombination von Löchern während des Haltens von "1" zu vermeiden. Bei diesem Design wird an Gate2 eine kleine negative Vorspannung angelegt, um Löcher in der Potentialmulde zu halten, nachdem „1“ gehalten wurde, während die Potentialmulde nach dem Halten von „0“ an Löchern verarmt ist.

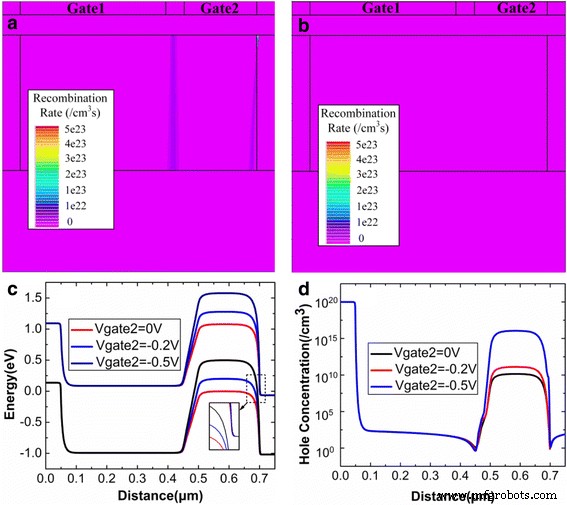

Bei der negativeren Gate2-Spannung (–0,5 V) während des Haltevorgangs wird die Rekombination von Löchern nach dem Halten von „1“ eliminiert, wie in Abb. 5a, b gezeigt. Die Eliminierung der Lochrekombination ist vorteilhaft für das Halten von Löchern während des Haltens von "1". An Gate2 wird eine kleine negative Vorspannung angelegt, um die Tiefe der Potentialmulde zu erhöhen und Löcher lange zu halten, was für die Haltezeit des DGTFET-DRAM von Vorteil ist. Während „0“ gehalten wird, kann eine negative Gate2-Vorspannung das Energieband des Kanalbereichs unter Gate2 hochziehen, was verhindern kann, dass Elektronen, die von BTBT zwischen Source und Kanal kommen, zur Drain-Seite fließen. Daher kann Gate2 mit einem negativen Wert den Lesestrom „0“ reduzieren. Gate2 mit negativerer Spannung (–0,5 V) verringert jedoch den Tunnelabstand nahe der Drain-Seite, wie in Fig. 5c gezeigt. Dieser verringerte Tunnelabstand bewirkt, dass der BTBT während des Haltens von "0" nahe der Drain-Seite ist, was die Ansammlung von Löchern in der Potentialmulde während des Haltens von "0" fördert, wie in Fig. 5d gezeigt. Die negativere Gate2-Spannung (–0,5 V) während des Haltens von "0" verschlechtert also den Zustand "0". Um die Lochrekombination und den BTBT während des Haltens von "1" bzw. des Haltens von "0" zu eliminieren, wird daher –0,2 V als optimale Gate2-Vorspannung während des Haltevorgangs angesehen.

Rekombinationsrate in der DG-TFET-DRAM-Zelle nach dem Halten von „1“, wenn die Gate2-Spannung a . ist 0 V und b –0,5 V; c Energiebanddiagramm und d Lochkonzentration nach dem Halten von „0“. a , b Die Rekombinationsrate nach dem Halten von "1", wenn die Gate2-Spannung auf 0 V bzw. -0,5 V eingestellt ist. c Das Energieband des Geräts vom Source-Bereich zum Drain-Bereich. d Die Lochkonzentration des Geräts nach dem Lochen von „0“. Das Energieband und die Lochkonzentration werden bei 3 nm unter dem Gate-Oxid extrahiert

Lesevorgang

Anschließend wird auch die Optimierung des Lesebetriebs untersucht. Der Lesevorgang basiert stark auf dem BTBT zwischen den P + Quelle und Kanal. Während des Lesens von „1“ fördert Gate1 hauptsächlich den BTBT auf der Source-Seite, während Gate2 mit der hohen Spannung die Energiebarriere senkt, die dem Fluss von Elektronen vom Kanal zum Drain widersteht. Während des Lesens von „0“ ist es jedoch erforderlich, dass Gate2 mit der kleinen Spannung in der Lage ist, den Elektronenfluss vom Kanal zum Drain zu verhindern. Daher ist die Optimierung der Gate1- und Gate2-Spannungen für den Lesevorgang sehr wichtig.

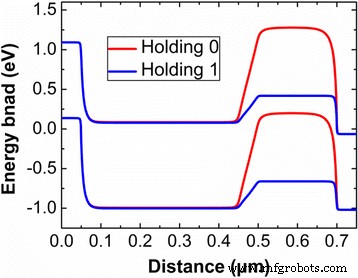

Abbildung 6 zeigt die verschiedenen Energiebanddiagramme nach dem Halten von „1“ und Halten von „0“. Beim Lesen von „1“ und Lesen von „0“ werden an den Gate-Seiten die gleichen Spannungen angelegt. Da die positiven Gate-Bias während des Lesevorgangs verwendet werden, wird das Energieband immer dann abgelegt, wenn „1“ oder „0“ gelesen wird. Das Energieband des Kanals unter Gate2 ist nach dem Halten von „0“ höher als das nach dem Halten von „1“, und dieses Energieband ist auch beim Lesen von „0“ höher als beim Lesen von „1“. Die höhere Energie des Kanals unter Gate2 schafft eine wirksame Barriere, um Elektronen zu widerstehen, die in Richtung der Drain-Seite fließen, was den Lesestrom „0“ verringert.

Energiebanddiagramm nach a „1“ halten und b „0“ halten. a , b Das Energieband des Geräts nach dem Halten von „1“ bzw. „0“. Das Energieband wird bei 3 nm unterhalb des Gate-Oxids extrahiert

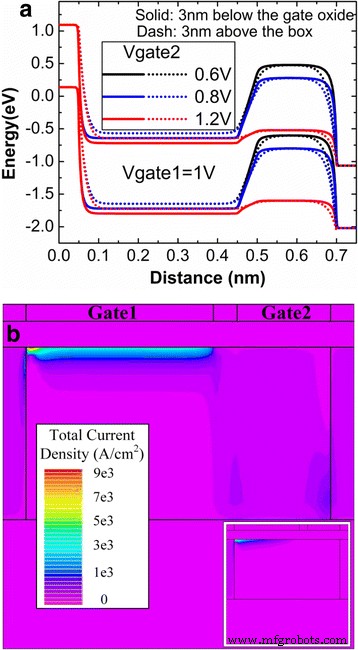

Während des Lesevorgangs wird die Drain-Vorspannung auf 1 V eingestellt, damit der Drain-Strom im DG-TFET gelesen werden kann. Behalten Sie zunächst die Gate1-Spannung von 1 V bei und ändern Sie die Vorspannung von Gate2, um die optimale Gate2-Spannung auszuwählen. Da die Gate2-Spannung hauptsächlich den Lesestrom „0“ beeinflusst, wird die Optimierung der Gate2-Spannung durch den „0“-Lesemechanismus analysiert. Abbildung 7a zeigt die Variation des Energiebandes mit der Gate2-Spannung nach dem Lesen von „0“. Wenn die Gate2-Spannung niedriger ist (0,6 oder 0,8 V), wird der Kanal unter Gate2 vollständig erschöpft. Wenn die Gate2-Spannung jedoch auf 1,2 V ansteigt, kann das Pulldown-Energieband des Kanals unter Gate2 keine wirksame Barriere bilden, um zu verhindern, dass Elektronen zur Drain-Seite fließen. Abbildung 7b und ihr Einschub zeigen jeweils die Gesamtstromdichte nach dem Lesen von „0“, wenn die Gate2-Spannung 1 V und 0,8 V beträgt. Die offensichtliche Stromdichte ist deutlich im Kanalbereich unter Gate2 zu finden, wenn die Gate2-Spannung 1 V beträgt ergeben den höheren Messwert „0“ Strom. Daher gelten 0,8 V als optimale Gate2-Spannung für den Lesevorgang.

a Energiebanddiagramm und b Gesamtstromdichte nach dem Lesen von „0“. a , b Das Energieband bzw. die Gesamtstromdichte nach dem Lesen von „0“. Das Energieband wird bei 3 nm unterhalb des Gate-Oxids extrahiert

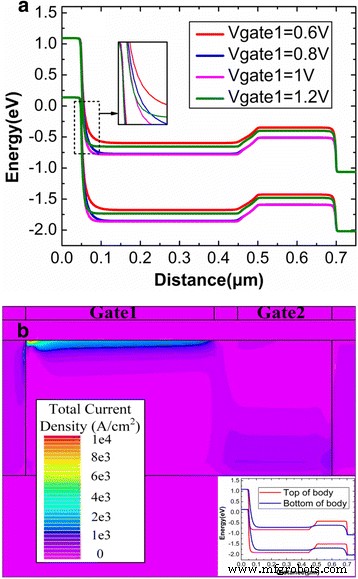

Schließlich wird auch die Optimierung des Gate1-Bias durchgeführt. Abbildung 8a zeigt die Variation des oberen Energiebandes mit der Gate1-Spannung. Die Breite der BTBT-Barriere auf der Source-Seite nimmt mit zunehmender Gate1-Spannung allmählich ab, aber dieser abnehmende Trend beginnt sich zu sättigen, wenn die Gate1-Spannung höher als 1 V ist. Und die Gate1-Spannung von 1 V kann keinen starken Einfluss auf das Lesen von „0“ haben ”-Betrieb, der in Abb. 7b demonstriert wurde. Daher wird 1 V als optimale Gate1-Vorspannung während des Lesevorgangs angesehen.

a Energiebanddiagramm und b Gesamtstromdichte nach dem Lesen von „1“. a , b Das Energieband bzw. die Gesamtstromdichte nach dem Lesen von „1“. Das Energieband wird bei 3 nm unterhalb des Gate-Oxids extrahiert

Durch die obige Analyse wird der tiefe Potentialtopf nur am oberen Ende des Kanals unter Gate2 gebildet, nachdem „1“ geschrieben wurde. Daher ist im Kanalbereich unter Gate2 das Energieband am oberen Ende des Kanals viel höher als das am unteren Ende des Kanals. Dies zeigt, dass während des Lesens von „1“ am oberen Rand des Kanals unter Gate2 eine Barriere vorhanden ist. Der Einschub von Abb. 8b zeigt das Energieband sowohl am oberen als auch am unteren Ende des Kanals nach dem Lesen von „1“. Es ist klar zu erkennen, dass zwischen Gate1 und Gate2 am oberen Ende des Kanals eine höhere Kanalbarriere existiert, diese Barriere am unteren Ende des Kanals jedoch nicht. Daher befindet sich der Leitungspfad beim Lesen von „1“ am oberen Ende des Kanals unter Gate1 und am unteren Ende des Kanals unter Gate2, was durch die Stromdichte in Abb. 8 deutlich demonstriert werden kann.

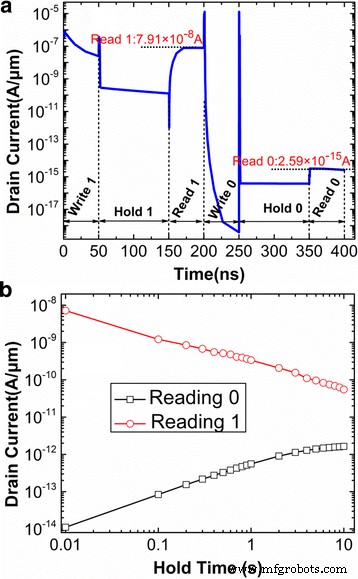

Unter Anwendung der obigen optimierten Programmierbedingung ist das Einschwingverhalten der DG-TFET-DRAM-Zelle in Fig. 9 gezeigt. Sowohl die Schreib- als auch die Lesezeit werden auf 50 ns eingestellt und die Haltezeit wird auf 100 ns eingestellt. In Fig. 9a beträgt das aktuelle Verhältnis des Messwerts „1“ zum Messwert „0“ bis zu 10 7 . , was viel höher ist als 10 2 ~10 3 in Referenz [16, 18, 23]. Wenn die Haltezeit auf 10 s ansteigt, überschreitet das Stromverhältnis immer noch 10. In Referenz [16], wenn die Haltezeit auf 2 s erhöht wird, beträgt das Stromverhältnis nur etwa 10. Daher ist die RT von DG-TFET DRAM mit der optimierten Programmierbedingung ist länger als 2 s. Somit bewirkt die optimierte Programmierbedingung, dass die DG-TFET-DRAM-Zelle nicht nur das höhere Lesestromverhältnis, sondern auch die größere RT erhält. Darüber hinaus ist der Lesestrom „0“ bei optimierter Programmierspannung viel geringer als in Referenz [16, 18, 22, 23], was es ermöglicht, Anwendungen mit geringerer Leistung zu erfüllen.

a Transiente Drain-Ströme in der Reihenfolge der Operation; b Änderung des Lesestroms mit der Haltezeit. a Der Übergangsstrom der DGTFET-DRAM-Zelle während der Schreib-, Halte- und Lesevorgänge. b Die Variationen des Lesens von „1“ und des Lesens von „0“ aktuell mit den unterschiedlichen Haltezeiten

Schlussfolgerungen

Die detaillierte Optimierungsrichtlinie der Programmierbedingungen für den DG-TFET DRAM wird in diesem Papier unter Verwendung des Silvaco-Atlas-Simulationstools vorgeschlagen. Während des Schreibens von "1" erzeugt Gate2 mit der negativen Spannung (–1,3 V) eine Potenzialmulde, und der BTBT zwischen Kanal und Drain sorgt dafür, dass sich die Löcher in dieser Potenzialmulde ansammeln. Während des Schreibens von „0“ lässt Gate2 mit der positiven Spannung (1,3 V) Löcher aus dem Potenzialtopf entweichen. Für den Haltevorgang wird die kleine negative Spannung (–0,2 V) an Gate2 angelegt, um die Löcher zu halten, was den Ablesestrom „1“ verbessern kann. Nach dem Halten von „0“ kann die Barriere des Kanals unter Gate2 den Elektronen widerstehen, die in Richtung der Drain-Seite fließen, um den Lesestrom von „0“ zu reduzieren. Zur Optimierung des Lesebetriebs wird die größere Gate1-Spannung (1 V) hauptsächlich verwendet, um BTBT an der Source-Seite während des Lesens von "1" zu verbessern, während eine geeignete Gate2-Spannung (0,8 V) verwendet wird, um dem Elektronenfluss während des Lesens in Richtung Drain zu widerstehen „0“. Durch die optimierten Programmierbedingungen erhält der DG-TFET DRAM das höhere Stromverhältnis (10 7 ) von „1“ zu „0“ und einer Verweilzeit von mehr als 2 s. Und der extrem niedrige „0“-Ablesestrom hilft bei der Reduzierung des Stromverbrauchs.

Nanomaterialien

- Die Vorteile von Fernüberwachung, Fernprogrammierung und vorausschauender Wartung

- Die Herausforderungen der Multicore-Programmierung und des Debuggens meistern

- Breadboarding und Programmierung des ATmega328P &ATtiny45 in Atmel Studio 7

- Einsatz von IoT-basierten Technologien auf der Baustelle

- Biometrisches Sicherheitssystem basierend auf dem menschlichen Herzschlag

- Kommentar:Die Methoden der Roboterprogrammierung verstehen

- Der Design- und Implementierungsprozess der Anlagenautomatisierung

- Füllen Sie die leere CNC-Programmierübung Mehrere Bögen

- Füllen Sie die leere CNC-Programmier-Fräsübung aus

- Füllen Sie die leere CNC-Programmierübung aus