Verbesserung der Leistung von a-IGZO-TFT-Geräten durch einen sauberen Schnittstellenprozess durch Ätzstopper-Nanoschichten

Zusammenfassung

Um die technologischen und wirtschaftlichen Hindernisse der amorphen Indium-Gallium-Zink-Oxid (a-IGZO)-basierten Display-Backplane für die industrielle Produktion zu überwinden, wird ein Clean-Etch-Stopper (CL-ES)-Prozess zur Herstellung von a-IGZO-basierten dünnen Filmtransistor (TFT) mit verbesserter Gleichmäßigkeit und Reproduzierbarkeit auf Glassubstraten der 8.5. Generation (2200 mm × 2500 mm). Im Vergleich zu einem a-IGZO-basierten TFT mit rückkanalgeätzter (BCE) Struktur, einer neu gebildeten ES-Nanoschicht (~ 100 nm) und einer gleichzeitigen Ätzung von a-IGZO-Nanoschicht (30 nm) und Source-Drain Elektrodenschicht werden zunächst in ein a-IGZO-basiertes TFT-Gerät mit CL-ES-Struktur eingeführt, um die Einheitlichkeit und Stabilität des Geräts für großflächige Anzeige zu verbessern. Die Sättigungselektronenmobilität von 8,05 cm 2 /V s und das V te Gleichmäßigkeit von 0,72 V werden auf dem a-IGZO-basierten TFT-Gerät mit CL-ES-Struktur realisiert. In den Zuverlässigkeitstests bei negativer Vorspannung bei Temperaturbeleuchtung und positiver Vorspannung bei thermischer Belastung unter a ± 30 V Vorspannung für 3600 s wurde die gemessene V te Verschiebung des CL-ES-strukturierten Geräts signifikant auf – 0,51 und + 1,94 V verringert, was viel niedriger ist als die des BCE-strukturierten Geräts (– 3,88 V, + 5,58 V). Die elektrische Leistung des a-IGZO-basierten TFT-Bauelements mit CL-ES-Struktur impliziert, dass der wirtschaftliche Übergang von einem siliziumbasierten TFT-Prozess auf einen Metalloxid-Halbleiter-basierten Prozess für die LCD-Herstellung sehr gut möglich ist.

Hintergrund

Dünnschichttransistor-(TFT)-Rückwandplatine mit höherer Auflösung und größerer Plattengröße ist in der Flachdisplayindustrie sehr erwünscht. Halbleitermaterial mit hoher Elektronenbeweglichkeit ist entscheidend, um die Leistung der TFT-Backplane zu verbessern. Insbesondere wird eine TFT-Rückwand auf Metalloxid-Halbleiterbasis als vielversprechender Kandidat angesehen, um die Einschränkungen der siliziumbasierten TFT-Rückwand in Bezug auf mechanische Flexibilität und Elektronenmobilität zu überwinden [1,2,3,4]. Obwohl eine TFT-Backplane auf Metalloxid-Halbleiterbasis vielversprechende Eigenschaften zeigt, wird die Prozessmethode mit einem kostengünstigen Prozess sowohl für die großtechnische Abscheidung als auch für die industrielle Anwendung noch benötigt [5].

Amorphes Indium-Gallium-Zink-Oxid (a-IGZO) ist ein ausgezeichneter Metalloxid-Halbleiter mit einer hohen Sättigungselektronenmobilität (~ 5–10 cm 2 /V s) und ein niedriger Ausschaltstrom (< 10 pA) [6,7,8,9,10]. Das gängige industrielle Herstellungsverfahren für a-Si:H-basierte TFT-Rückwandplatinen ist das Fünf-Masken-Rückkanalätzverfahren (BCE). Ein a-IGZO-Nanofilm weist jedoch eine sehr geringe chemische Beständigkeit gegenüber den typischen Ätzmitteln auf, die derzeit im BCE-Prozess verwendet werden. Insbesondere a-IGZO-Nanofilme würden in wenigen Sekunden vollständig geätzt, wenn sie einem Al-Ätzmittel ausgesetzt werden, das aus Phosphorsäure, Salpetersäure und Essigsäure besteht [11,12,13]. Dieses unkontrolliert schnelle Ätzen behindert die Einführung des BCE-Prozesses für a-IGZO-basierte TFT-Rückwandplatinen. Um a-IGZO in einer BCE-strukturierten Rückwand zu verwenden, wurde die Cu-Verdrahtungstechnologie als Ätzmittel im Cu-Verdrahtungsprozess entwickelt, die auf H2 . basiert O2 , ist gegenüber a-IGZO-Nanofilmen viel milder als diejenigen, die bei der Al-Verdrahtung verwendet werden [11, 13]. Leider wird der a-IGZO-Nanofilm während des Cu-Verdrahtungsprozesses immer noch beschädigt, selbst wenn ein milderes Ätzmittel verwendet wird. Noch mildere Ätzmittel verursachen Schäden an der Oberfläche des a-IGZO-Nanofilms, der den Rückkanal von TFT-Geräten bildet. Diese Schäden führen zu einem Zusammenbruch des stöchiometrischen molekularen Zusammensetzungsverhältnisses nahe der Oberfläche des a-IGZO-Nanofilms, was zu einer Verschlechterung der Gleichförmigkeit der großflächigen Anzeige und der Zuverlässigkeit der TFT-Vorrichtung führt. Bis heute wird ein konventioneller Sechs-Masken-Ätzstopper (CV-ES)-Prozess entwickelt, um eine a-IGZO-basierte TFT-Rückwand mit Ätzstopper-Schicht (ESL)-Struktur herzustellen [14, 15]. Dieses Sechs-Masken-ES-Verfahren kann jedoch zu einer negativen Wirtschaftlichkeit führen. Darüber hinaus würde diese erhöhte Anzahl von Dünnfilmschichten den Überlappungsbereich zwischen den Schichten erhöhen und zu einer erhöhten parasitären Kapazität und einem verringerten Öffnungsverhältnis führen [16,17,18]. Obwohl kürzlich über einen Fünfmasken-ES-Prozess berichtet wurde, der eine TFT-Rückwand unter Verwendung der Halbton- und Lift-Off-Technologie herstellt, ist dieser Prozess für die Herstellung von a-IGZO-basierten TFT-Rückwänden nicht zugänglich, da ihre aktive Schichtoberfläche immer noch ausgesetzt ist Prozesschemikalien wie Stripper und Photoresist im letzten Schritt, die eine erhebliche Kontamination von a-IGZO verursachen können und somit die Gerätequalität und die Produktionsausbeute reduzieren [19,20,21]. Daher bleibt das industrielle Herstellungsverfahren für a-IGZO-basierte TFT-Rückwandplatinen mit hoher Gleichmäßigkeit und Stabilität eine Herausforderung.

In diesem Papier schlagen wir einen sauberen Fünf-Masken-ES-Prozess (CL-ES) vor, indem wir ESL für die Herstellung einer a-IGZO-basierten TFT-Backplane einführen. Dieses neu entwickelte CL-ES-Verfahren ist hochgradig kompatibel mit dem bestehenden Verfahren für BCE-Geräte. Dieser CL-ES-Prozess ist so konzipiert, dass er die gleichen Masken wie der BCE-Prozess aufweist, was einen vernachlässigbaren Produktivitätsverlust der bestehenden AM-LCD-TFT-Backplane-FAB gewährleistet. Eine mit dem CL-ES-Prozess hergestellte a-IGZO-basierte Rückwand lagert nacheinander Gate-Isolator, IGZO-Nanoschicht und ES-Nanoschicht ab und bildet dann durch Trockenätzverfahren eine neue ESL-Maske. Dies könnte die Kontamination der a-IGZO-Nanoschicht und ihrer Grenzfläche durch Ätzmittel, Stripper und Lösungsmittel verhindern. Diese neu gebildete Nanomaske trägt dazu bei, die Gleichmäßigkeit und Stabilität des TFT-Geräts zu verbessern. Im Vergleich zu einem herkömmlichen BCE-strukturierten Bauelement zeigt ein a-IGZO-basiertes Bauelement mit CL-ES-Struktur verbesserte elektrische Leistungen, nämlich eine höhere Sättigungselektronenmobilität, ein hohes Öffnungsverhältnis und einen geringen Stromverbrauch.

Methoden/Experimental

Herstellung einer a-IGZO-basierten TFT-Backplane

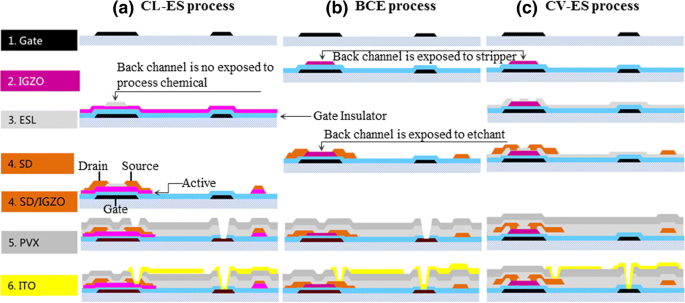

Die a-IGZO-basierte TFT-Backplane mit ES-Struktur, die über den CL-ES-Prozess hergestellt wurde, war wie folgt (Abb. 1).

(Farbe online) Schema von a CL-ES, b BCE und c CV-ES-Prozesse

Zunächst wurde eine Doppelschicht (Mo/Cu:30 nm/250 nm) für die Gate-Elektrode verwendet, da sie einen relativ niedrigen spezifischen Widerstand hat. Dann wurde ein Gate-Isolator, Siliziumnitrid (SiNx)/Siliziumoxid (SiOx) (300 nm/100 nm), durch ein plasmaunterstütztes chemisches Gasphasenabscheidungsverfahren (PECVD) abgeschieden. Dieser SiNx-Film soll die Oxidation der Cu-Metallisierung und die Diffusion von Cu-Ionen in den Gate-Isolator verhindern. Anschließend wurde ein dünner SiOx-Film abgeschieden. Die Abscheidungsbedingungen des PECVD-SiOx-Films waren 17 KW HF-Leistung, 1000 mTorr Druck, 1:55 SiH4 /N2 O-Gasverhältnis und 350 °C Temperatur. Dann wurde ein a-IGZO-Nanofilm bei 30 nm unter Verwendung von DC-Rotations-Magnetron-Sputtern abgeschieden. Das Ziel hatte einen Durchmesser von 171 mm, während die Zusammensetzung In2 . war O3 :Ga2 O3 :ZnO = 1:1:1 Mol-%. Die Sputterparameter für den a-IGZO-Nanofilm waren Systembasisdruck von 5~ 9 × 10 –7 Torr, HF-Sputterleistung von 10 KW, Sputterdruck von 5 mTorr Ar/O2 Gasgemisch (85% Ar-15% O2 ). Die Abscheidungstemperatur liegt bei Raumtemperatur. Der hergestellte a-IGZO-Film wird bei 330 °C für 1 h in sauberer, trockener Luft getempert.

Zweitens wurde eine Ätzstopper (ES)-Nanoschicht (SiOx) unter Verwendung des PECVD-Verfahrens abgeschieden. Gleichzeitig wird eine ES-Nanoschicht abgeschieden, um eine Kontamination in der a-IGZO-Schicht zu verhindern. Wie beim BCE-Prozess gibt es keine Schutzschicht für einen a-IGZO-Nanofilm vor dem S/D-Elektrodenstrukturierungsprozess, eine Oberflächenkontamination und eine Beschädigung des a-IGZO-Nanofilms durch S/D-Ätzmittel beim Bilden eines TFT-Kanals sind unvermeidlich. Die ES-Nanoschicht im CL-ES-Prozess kann den TFT-Kanal effektiv vor externer Kontamination und Beschädigung schützen. Die ES-Nanoschicht wurde mit einer Dicke von 100 nm abgeschieden. Die Abscheidungsbedingungen der SiOx-Dünnschicht waren 17 KW HF-Leistung, 1000 mTorr Druck, 1:66 SiH4 /N2 O-Gasverhältnis und 240 °C Temperatur. Die hergestellte ES-Nanomaske wurde durch Trockenätzen und Strukturieren geätzt. Während des Ätzprozesses wird CF4 und O2 Gas wurde mit einer Rate von 2000 sccm/800 sccm geliefert.

Drittens wurde Mo/Cu/Mo auch für die S/D-Elektrode verwendet. Um die S/D-Elektrode eines a-IGZO-TFT auszuwählen, wurde angenommen, dass die Austrittsarbeitsdifferenz zwischen Metall und a-IGZO einen Ohmschen Kontakt und die Materialien mit niedrigem Widerstand bildet. Wie beim Ätzstoppprozess beschrieben, werden während der Strukturierung der ES-Nanomaske die a-IGZO-Nanofilme, die nicht durch die Ätzstoppschicht geschützt sind, bereits durch Beschuss mit CF4<. geleitet /sub> Plasma. Daher wird mit Mo/Cu/Mo auf natürliche Weise ein ohmscher Kontakt gebildet [22]. Die S/D-Schichten wurden in einer Dicke von 30 nm/300 nm/30 nm mit den gleichen Sputterbedingungen wie die Gate-Elektrode abgeschieden. Darüber hinaus wurden mehrere dünne Filmschichten aus Mo/Cu/Mo und a-IGZO mit „H2 . stapelgeätzt O2 Cu-Ätzmittel auf Cu-Basis mit Fluoridzusatz” zur Vervollständigung der S/D-Elektrode. Das auf Cu hinzugefügte 30 nm Mo wurde gebildet, um eine Oxidation der Cu-Oberfläche durch einen Passivierungsfilm (SiOx) im nächsten Prozess zu verhindern und eine Plasmaschädigung der Cu-Oberfläche während des Trockenätzens zur Bildung von Passivierungslöchern zu verhindern.

Viertens wurde ein Passivierungsfilm, unterteilt in zwei Arten von Dünnfilmen, unter Verwendung des PECVD-Verfahrens abgeschieden. Die erste Passivierung bestand aus einem dünnen SiOx-Film. Der dünne Film war 250 nm dick. Die zweite Passivierung bestand aus einem dünnen SiNx-Film. Die Dicke des Dünnfilms betrug 200 nm.

Fünftens wurde als Pixelelektrode ein Indium-Zinn-Oxid-(ITO)-Film verwendet, der am häufigsten in der Display-Industrie verwendet wird. Der ITO-Film war 40 nm dick, und für die Abscheidung wurde Gleichstromsputtern verwendet. Dann wurde das abschließende Glühen in einer sauberen Trockenluftumgebung bei 230 °C für 1 h unter Verwendung eines Heißluftofens durchgeführt. Die elektrischen Eigenschaften von hergestellten a-IGZO-TFTs wurden mit dem Keysight 4082A Parametric Test System gemessen. Mit diesem Verfahren wird die gleiche Anzahl von Masken (TN-Produktstandard:fünf Masken) erhalten wie beim BCE-Verfahren, das in der Massenfertigung weit verbreitet ist.

Zum Vergleich wurde eine a-IGZO-basierte TFT-Backplane mit BCE-Struktur im BCE-Prozess hergestellt.

Charakterisierung

Die I-V-Messung des TFT wurde bei Raumtemperatur unter Verwendung eines Halbleitercharakteristikanalysators durchgeführt. Die Analysebedingung zur Bewertung der Stabilität des TFT unter negativem Gate-Bias-Temperatur-Beleuchtungsstress (NBTIS) war wie folgt. V gs und V ds wurden jeweils auf − 30 und 15 V fixiert, und die Temperatur des Substrats wurde bei 60 °C gehalten. Die Luminanz für NBITS wurde auf 5000 cd/m 2 . eingestellt . Die Dauer des Stresses zur Auswertung dauerte 3600 s an [23]. Thermischer Stress mit positiver Gate-Vorspannung (PBTS) wurde bei V . getestet gs von 30 V und V ds von 15 V und die Substrattemperatur wurde auf 60 °C eingestellt. Die Belastungsdauer für die Bewertung wurde 3600 s lang fortgesetzt [24].

Ergebnisse und Diskussion

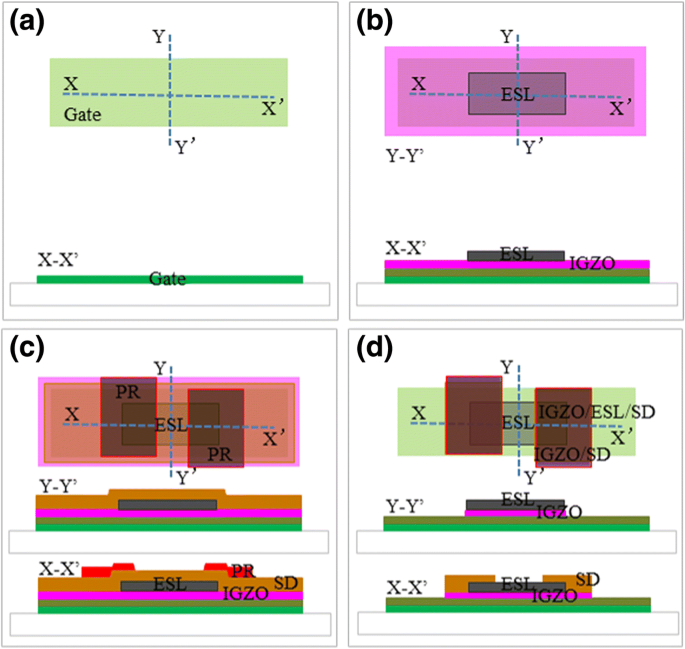

Ein über den CL-ES-Prozess hergestellter a-IGZO-basierter TFT zeigt die gleiche Maskennummer wie der BCE-Prozess (Abb. 1). Verglichen mit einem a-IGZO-basierten TFT mit BCE-Struktur weist ein a-IGZO-basierter TFT mit CL-ES-Struktur zwei Vorteile auf:(1) a-IGZO-basierte Rückwand, die unter Verwendung des CL-ES-Prozesses hergestellt wurde, scheidet einen Gate-Isolator ab, a-IGZO nano -Schicht und ES-Nanoschicht nacheinander, bildet dann eine ESL-Nanomaske durch ein Trockenätzverfahren. Diese neu gebildete ESL-Nanomaske mit 100 nm kann verhindern, dass ein a-IGZO-Nanofilm Ätzmittel, Stripper oder Fotolack ausgesetzt wird. Daher wird die Kontamination an Zwischenschichtgrenzflächen wirksam verhindert [25]. (2) Gleichzeitig wird der a-IGZO-Nanofilm nicht durch die ES-Schicht geschützt, sondern mit CF4 . beschossen Plasma während der ESL-Nanomaskenbildung, wird so zu einem Leiter. Dies bildet natürlich den ohmschen Kontakt zwischen der S/D-Elektrode des folgenden Prozesses und dem a-IGZO-Halbleiter. Für einen anderen Teil kann ein gleichzeitiges Ätzen von S/D- und a-IGZO-Nanoschichten eine Überlagerungstoleranz der ESL-(a-IGZO + S/D-Metallisierung)-Schicht sein, was die zwei Überlagerungsprozessfehler der a- IGZO-ESL- und ES-S/D-Metallisierungsschicht im konventionellen ESL-Prozess (Abb. 2). Die Überlagerungsanzahl der a-IGZO-, ES- und S/D-Schicht wird reduziert, was zu einer Verringerung der Größe des TFT-Bauelements führte, was die parasitäre Kapazität verringerte. Die planare Ergebnisstruktur ähnelt der BCE-Struktur (Abb. 3a, b).

(Farbe online) Schematische Darstellung des simultanen Bildungsverfahrens für TFT-Kanal und S/D-Elektrode im CL-ES-Prozess. a Der erste Schritt, der die Gate-Elektrode bildet. b Der zweite Schritt, der eine Ätzstoppschicht bildet. c Der dritte Schritt, der ein S/D-Fotomuster bildet. d Der vierte Schritt, der eine S/D-Elektrode und ein aktives Muster bildet

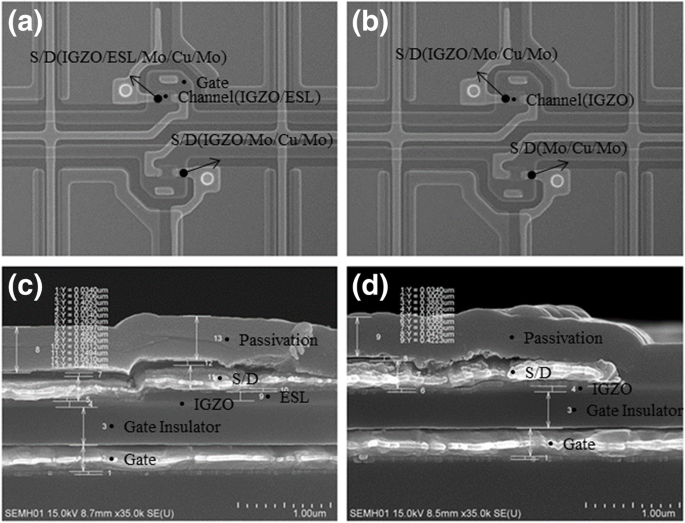

(Farbe online) REM-Bilder von a-IGZO TFT (a , b Ansicht von oben; c , d Seitenansicht) mit CL-ES-Struktur (a , c ) und BCE-Struktur (b , d )

Abbildung 3 zeigt die SEM-Bilder von a-IGZO-basierten TFTs mit CL-ES-Struktur (Fig. 3a, c) und BCE-Struktur (Fig. 3b, d). Aus der Draufsicht sind die Unterschiede zwischen CL-ES-Struktur und BCE-Struktur schwer zu erkennen (Abb. 3a, b). In der Seitenansicht befindet sich eine ES-Nanoschicht zwischen der a-IGZO-Nanoschicht und der S/D-Elektrodenschicht in CL-ES-Struktur (Abb. 3c). Währenddessen befindet sich auf der a-IGZO-Nanoschicht in BCE-Struktur eine Passivierungsschicht (Abb. 3d). Bei dem vorgestellten CL-ES-Verfahren wird eine a-IGZO-Nanoschicht mit einer Dicke von 30 nm abgeschieden. Außerdem ist die Beschädigung beim Nassätzen vernachlässigbar. Für den BCE-Prozess wird eine 70-nm-a-IGZO-Nanoschicht abgeschieden, da die a-IGZO-Schicht eine Kompensation für Ätzverluste benötigt. Der Unterschied zwischen den Dicken von a-IGZO-Nanoschichten in CL-ES- und BCE-Strukturen kann in den REM-Bildern beobachtet werden (Abb. 3c, d).

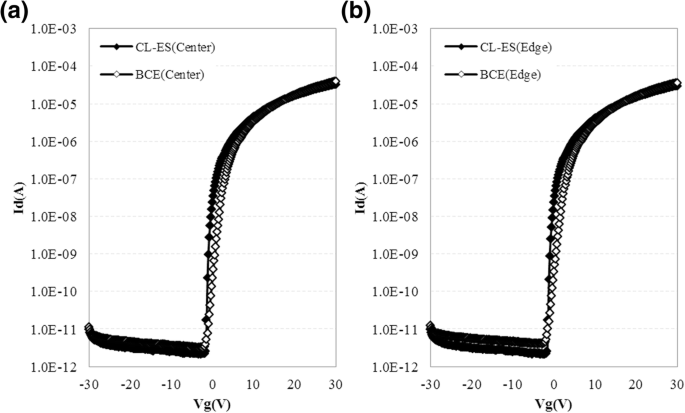

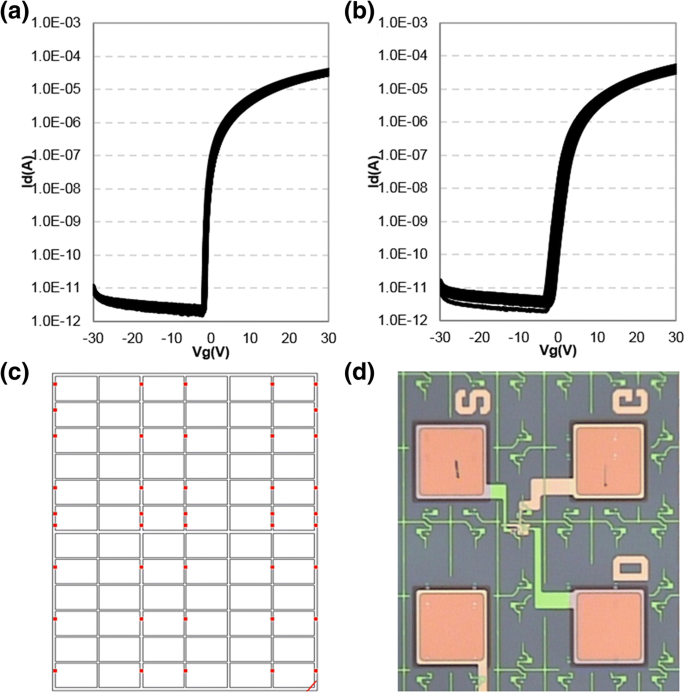

Die I-V-Eigenschaften von a-IGZO-basierten TFTs mit CL-ES-Struktur und BCE-Struktur werden verglichen (Abb. 4). Die Sättigungselektronenmobilität, die Schwellenspannung, der unterschwellige Spannungshubwert (SS) und weitere charakteristische Werte sind in Tabelle 1 zusammengefasst. Beachten Sie, dass die in Tabelle 1 zusammengefassten Werte die durchschnittliche Zahl sind, die von der Mitte und dem Rand eines Glassubstrats der 8,5 Generation abgeleitet wird . Der a-IGZO-basierte TFT mit CL-ES-Struktur realisiert V te von − 0,8 V, SS-Wert von 0,18 V/dec und Sättigungselektronenmobilität von 8,05 cm 2 /V s. Beim a-IGZO-basierten TFT mit BCE-Struktur sind die entsprechenden Ergebnisse V te von + 0,5 V, SS-Wert von 0,77 V/dec und Sättigungselektronenmobilität von 6,03 cm 2 /V s. Im Vergleich zur BCE-Struktur zeigt die CL-ES-Struktur verbesserte Geräteleistungen. Jedoch ist die Einschaltstromcharakteristik des a-IGZO-basierten TFT-Bauelements mit CL-ES-Struktur niedriger als bei einem BCE-strukturierten Bauelement. Dies liegt an der Tatsache, dass sich die TFT-Kanalstrukturen in CL-ES- und BCE-Strukturen unterscheiden. Im Allgemeinen ist die BCE-strukturierte TFT-Kanallänge der Abstand zwischen S/D-Metallelektroden, und die gemessene Kanallänge in dieser Studie beträgt 5 um [21]. In der CL-ES-Struktur stehen die Elektroden in Kontakt mit dem a-IGZO-Nanofilm, der an der Seite der ESL-Nanomaske gestreckt ist. Daher wird die Kanallänge durch den Abstand zwischen den a-IGZOs bestimmt, die an den Seiten des Ätzstoppers definiert sind, aber nicht durch den Abstand zwischen den Elektroden. Die Kanallänge des vorliegenden Geräts mit CL-ES-Struktur wird mit 10 um gemessen.

(Farbe online) Vergleich der I-V-Charakteristik von a-IGZO-TFTs mit CL-ES und BCE-Struktur in der Mitte (a ) und Kante (b ) aus Glassubstrat der 8.5-Generation

Wie in Tabelle 1 gezeigt, sind die gemessenen Werte von I an /Ich aus Verhältnis (~ 10 6 , siehe Tabelle 1) sind etwa zehnmal kleiner als der typische Wert (> 10 7 ) von a-IGZO-basierten TFTs. Dies liegt daran, dass die hier verwendeten Messgeräte für die Massenproduktion der 8.5-Generation verwendet werden. Für diese Messungen sind lange Kabel erforderlich, da die Größe der Industrieanlagen groß ist. Die langen Kabel führten zu einem erhöhten Messrauschen. Bei der folgenden Zuverlässigkeitsprüfung werden kleinere Messgeräte verwendet und die einzelnen TFT-Geräte als Messproben verwendet. Auf diese Weise wird das gemessene I an /Ich aus Verhältnisse sind alle obere 10 7 (siehe unten).

Der CL-ES-Prozess wurde sorgfältig entwickelt, um zu verhindern, dass die a-IGZO-Kanalschicht Ätzmitteln, Photoresist oder Stripper ausgesetzt wird. Während des Prozesses, der den CL-ES-Prozess, den Gate-Isolator, die a-IGZO-Nanoschicht und die ES-Nanoschicht herstellt, ist jede Zwischenschicht-Grenzfläche zu Reinigungszwecken nur mit DI-Wasser in Kontakt. Daher ist die chemische Kontamination in der Isolatorschicht und der a-IGZO-Nanoschicht vernachlässigbar [25, 26]. Der BCE-Prozess setzt jedoch nicht nur die Kanalschicht den Chemikalien aus, sondern beinhaltet auch eine Verunreinigung durch Cu-Ionendiffusion, da der a-IGZO-Kanal direkt dem Cu-Metall ausgesetzt ist. Dies wird auch bei Geräten mit CL-ES-Struktur vermieden. Der Kanalbereich des a-IGZO-Nanofilms wird durch die ESL-Nanomaske gut geschützt. Die geringe chemische Kontamination im CL-ES-Prozess kann zu einer geringen Ladungsträgerfallendichte an der Grenzfläche zwischen a-IGZO-Nanoschicht und Isolatorschicht führen, was zu einem ausgezeichneten SS-Wert führt. Diese geringe chemische Kontamination von a-IGZO-basierten TFT-Geräten über den CL-ES-Prozess trägt auch dazu bei, die Einheitlichkeit und Reproduzierbarkeit von a-IGZO-TFTs zu verbessern, die in der industriellen Produktion sehr wichtig sind [27, 28].

Abbildung 5 zeigt die gemessene I-V-Charakteristik von TFTs mit CL-ES-Struktur und BCE-Struktur, abgeleitet von 42 Messpunkten auf einem Substrat der 8,5 Generation. a-IGZO-basierter TFT mit CL-ES-Struktur hat ein V te Bereich von 0,72 V, während der von BCE-strukturierten Geräten 2,14 V beträgt (Tabelle 1). Mit anderen Worten, die Einheitlichkeit der Geräteleistung wird durch die CL-ES-Struktur deutlich verbessert.

(Farbe online) a CL-ES-Struktur. b Die I-V-Übertragungscharakteristik der TFTs der BCE-Struktur. c 42 Messpunkte. d das Foto von TFT. Alle gemessen auf einem Substrat der 8.5-Generation

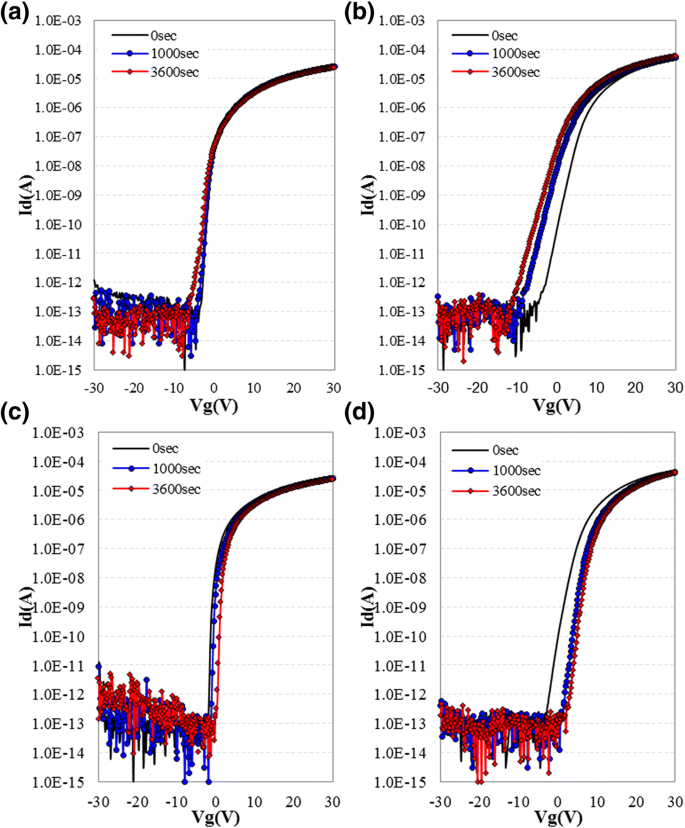

Abbildung 6a, b zeigen die I-V-Kennlinienverschiebung von CL-ES-strukturierten Geräten bzw. BCE-strukturierten Geräten, die bei NBTIS-Tests erhalten wurden. Die Ergebnisse der NBTIS-Tests sind in Tabelle 2 zusammengefasst. Unter den in Tabelle 2 beschriebenen Stressbedingungen beträgt die V te Verschiebung des CL-ES-strukturierten Geräts und des BCE-strukturierten Geräts sind – 0,51 bzw. – 3,88 V. Darüber hinaus sind die Ein-Strom-Verschiebung, die Aus-Strom-Verschiebung und die SS-Wert-Varianz des CL-ES-strukturierten Geräts alle niedriger als die des BCE-strukturierten Geräts (Tabelle 2); dies liegt daran, dass ein a-IGZO-basiertes Gerät mit CL-ES-Struktur die Kontamination von a-IGZO und eine niedrigere Ladungsträgerfallendichte des a-IGZO-TFT-Kanals effektiv verhindern kann. Insbesondere wenn man sich das Ergebnis der ersten 1000 s Belastung ansieht, wird bei CL-ES-strukturierten Geräten keine SS-Wertänderung beobachtet. Dieses Phänomen ist vergleichbar mit dem 0,16 V/dec-Anstieg des SS-Werts eines BCE-strukturierten Bauelements, da es zeigt, dass Defektstellen, die Trägerfallen auf der Oberfläche eines a-IGZO-Nanofilms bilden können, der den CL-ES-TFT-Rückkanal bildet, werden nicht zusätzlich durch elektrische und Beleuchtungsbelastung erzeugt. Diese Ergebnisse beweisen vollständig, dass ein CL-ES-strukturiertes Gerät viel stabiler ist als ein BCE-strukturiertes Gerät. Abbildung 6c, d zeigen die I-V-Kurvenverschiebung von CL-ES- und BCE-strukturierten TFTs, die aus PBTS-Tests erhalten wurden. Die detaillierten PBTS-Testergebnisse sind in Tabelle 3 zusammengefasst. Sowohl der CL-ES-strukturierte TFT als auch der BCE-strukturierte TFT haben während der PBTS-Bewertung im Ionenstrom abgenommen. Dies wird durch die Verschiebung von V . verursacht te in die positive Richtung. Während der PBTS-Auswertung, Restionenstromverhältnis [(letztes Ion/initiales Ion) × 100] des CL-ES-strukturierten TFT mit relativ kleiner V te positive Verschiebung (+ 1,94 V) liegt im Bereich von 88,2 %. Im Vergleich zum Restionenstromverhältnis des BCE-strukturierten TFT von 41,3% ist der CL-ES-strukturierte TFT deutlich überlegen. Dies zeigt den wichtigen Kapazitätsunterschied während des Entwurfs einer Gate-Drive-on-Array-(GOA)-Schaltung. Anders als bei NBTIS weist der SS-Wert von CL-ES-strukturierten TFTs keine signifikante Variation auf ((∆SS 0,06 V/dec) oder nimmt eher ab (∆SS − 0,86) wie bei BCE-strukturierten TFTs. Dies ist möglicherweise auf die Ladungsträger, sammeln sich im Innenraum und an der Grenzfläche zwischen Gate-Isolator und a-IGZO-Nanofilm durch positive Gate-Vorspannung an, füllen die Ladungsträgerfallenstelle in einem frühen Stadium, was zu einer Abnahme des Ladungsträgerfallenphänomens führt in der Nähe der Grenzfläche zwischen Gate-Isolator und a-IGZO-Nanoschicht eingeschlossene Ladungsträgerladung.Eine kleine Schwellenspannungsverschiebung von CL-ES-strukturierten TFTs bedeutet, dass die Grenzfläche und der Innenraum von a-IGZO bemerkenswert sauber sind weist darauf hin, dass die CL-ES-Struktur und der Prozess zu einer besseren Gerätezuverlässigkeit führen.

(Farbe online) Drift der I-V-Übertragungscharakteristik von CL-ES (a , c ) und BCE (b , d ) TFT von NBITS erhalten (a , b ) und PBTS-Tests (c , d )

Schlussfolgerungen

Zusammenfassend lässt sich sagen, dass ein neu entwickelter CL-ES-Prozess erfolgreich entwickelt wurde, um eine a-IGZO-basierte TFT-Backplane mit fünf Masken für eine fortschrittliche Anzeige herzustellen. Der CL-ES-Prozess hat die Vorteile einer Ätzstopper-Schichtstruktur, während er die gleiche Anzahl von Masken und ähnlichen Bauteilbereichen wie ein BCE-Prozess beibehält, wodurch das Problem einer erhöhten Maskenzahl und belegter Fläche bei herkömmlichen Ätzstopper-TFT-Bauelementen überwunden wird . Eine neu gebildete ESL-Nanomaske und ein gleichzeitiges Ätzen einer a-IGZO-Nanoschicht und einer S/D-Elektroden-Nanoschicht ermöglichen eine hohe Gleichmäßigkeit und Stabilität des Bauelements für großflächige Displays. In Bezug auf die elektrische Leistung sind die Reproduzierbarkeit und Zuverlässigkeit der Geräteleistung von a-IGZO-basierten TFTs mit CL-ES-Struktur viel besser als die von BCE-strukturierten Geräten. Das a-IGZO-basierte TFT-Gerät hat ein V te Verteilung über 42 Messpunkte TFTs auf dem Glassubstrat der 8,5er Generation von 0,72 V, Sättigungselektronenmobilität von 8,05 cm 2 /V s und SS-Wert von 0,18 V/dec. Gemäß den Ergebnissen der Zuverlässigkeitsbewertung von NBTIS und PBTS, V te Varianzen vor und nach Belastung von CL-ES a-IGZO-basierten TFTs betragen – 0,51 bzw. 1,94 V nach 3600 s Belastung. Die SS-Wertabweichungen betragen 0,33 und 0,06 V/Dez. Daher wird die vorgestellte CL-ES-Technik durch die Überwindung der technologischen und wirtschaftlichen Hindernisse den Weg für hochauflösende und großformatige Displayprodukte der nächsten Generation ebnen.

Abkürzungen

- a-IGZO:

-

Amorphes Indium-Gallium-Zink-Oxid

- AM-LCD:

-

Aktivmatrix-Flüssigkristallanzeige

- BCE:

-

Rückkanalätzung

- ESL:

-

Ätzstoppschicht

- GOA:

-

Gate-Laufwerk auf Array

- NBTIS:

-

Beleuchtungsstress bei negativer Vorspannungstemperatur

- PBTS:

-

Positiver Bias-Temperaturstress

- SiNx:

-

Siliziumnitrid

- SiOx:

-

Siliziumoxid

- SS:

-

Schwung unter der Schwelle

- TFT:

-

Dünnschichttransistor

- TN-LCD:

-

Twisted-nematische Flüssigkristallanzeige

Nanomaterialien

- Verwendung wasserfreier Technologien im Färbeprozess

- Hardware Boot Select Switch mit Pico

- Ausnutzung der Gesamtanlageneffektivität

- Strategien zur Verwaltung der Vermögensleistung

- Verwenden von Asset Performance Management zur Maximierung des Vermögenswerts

- Tauchbeschichtungsverfahren und Leistungsoptimierung für elektrochrome Drei-Zustands-Bauelemente

- Nanostrukturiertes Siliciumdioxid/Gold-Cellulose-gebundenes Amino-POSS-Hybrid-Komposit über den Sol-Gel-Prozess und seine Eigenschaften

- Herstellung von auf Nanoschalen basierenden periodischen 3D-Strukturen durch einen Schablonenprozess unter Verwendung von lösungsabgeleitetem ZnO

- Verwendung eines 3D-Druckers zur Verbesserung Ihres Fertigungsprozesses – Video

- Vorteile der Verwendung von VIA in Pads