Erhöhte Zuverlässigkeit von a-IGZO-TFTs mit einer reduzierten Merkmalsgröße und einer sauberen Ätzstopper-Schichtstruktur

Zusammenfassung

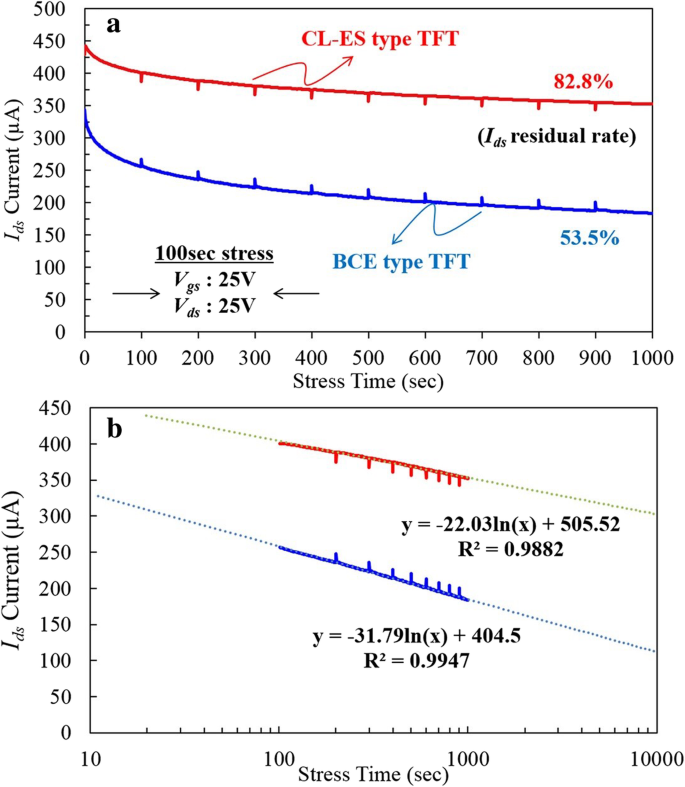

Die Auswirkungen von diffusem Cu + in amorphen Indium-Gallium-Zink-Oxid (a-IGZO) Dünnschichttransistoren (TFTs) auf die Mikrostruktur und Leistung während eines Clean Etch Stopper (CL-ES) Prozesses und eines Back Channel Etch (BCE) Prozesses untersucht und verglichen . Die mit einer sauberen Komponente gebildete CL-ES-Schicht, wie durch TOF-SIMS verifiziert, kann die a-IGZO-Schicht vor dem S/D-Ätzmittel schützen und Cu + . verhindern Diffusion, die dazu beiträgt, die Zahl der akzeptorähnlichen Defekte zu reduzieren und die Zuverlässigkeit der TFTs zu verbessern. Die hergestellten TFTs mit CL-ES-Struktur haben eine überlegene Ausgangsstabilität (letzter I ds /initial ich ds = 82,2% im Vergleich zu den BCE-strukturierten TFTs (53,5%), da sie einen besseren anfänglichen SS-Wert (0,09 V/dec vs 0,46 V/dec) und einen besseren endgültigen SS-Wert (0,16 V/dec vs 0,24 .) haben V/dec) nach der Bewertung der Hochstrombelastung (HCS). Insbesondere weist die Variation der Schwellenspannungen einen großen Unterschied auf (3,5 V für die CL-ES-TFTs und 7,2 V für die BCE-TFTs), was bedeutet, dass die CL-ES-strukturierten TFTs eine höhere Zuverlässigkeit aufweisen als die BCE-strukturierten TFTs. Daher wird erwartet, dass der CL-ES-Prozess die weit verbreitete Anwendung der a-IGZO-Technologie in der Halbleiterindustrie fördert.

Hintergrund

In letzter Zeit haben Display-Produkte nicht nur große Flächen und hohe Auflösungen betont, sondern auch ästhetisch ansprechende Außendesigns [1,2,3]. Schmale Blenden wurden als eines der wesentlichen Merkmale für diesen Designschwerpunkt übernommen [4]. Um dies zu realisieren, müssen die Hauptstromkreise, die das Display ansteuern, in das Panel integriert werden. Gate Drive IC on Array (GOA) ist eine relativ einfache und häufig verwendete Methode, bei der das Gate-Signal eine Zeile nach der anderen in das Panel eintritt und die V an bewegt sich jedes Mal nacheinander. GOA hat mehrere Vorteile, wie geringere Kosten (Beseitigung der G-IC-Kosten, Wegfall des G-IC-Bonding-Prozesses, erhöhte Nutzung des Glassubstrats usw.) und ästhetischer Effekt (schmale Blenden oder randlose Geräte) [5]. Im Gegensatz zu Einzelpixel-TFTs erfordern GOA-TFTs jedoch strengere Zuverlässigkeitsbedingungen, um einen höheren Ausgangsstrom und eine längere Einschaltdauer zu erreichen. Angesichts der in letzter Zeit zunehmenden Marktnachfrage nach hochauflösenden Produkten ist eine Verbesserung der Zuverlässigkeit der GOA-Leistung dringend und notwendig geworden [6].

Amorphes Indium-Gallium-Zink-Oxid (a-IGZO) wird aufgrund seiner hohen Sättigungselektronenmobilität (5~10 cm 2 /V s) und geringer Ausschaltstrom (< 1 pA) [7, 8]. Die Back Channel Etch (BCE)-Technologie wird häufig zur Herstellung von TFTs in der Industrie verwendet [9, 10]. BCE-strukturierte a-IGZO-TFTs haben zufriedenstellende Eigenschaften für einzelne Pixel-TFTs und die Größenreduktion von GOA-TFTs. Einige wichtige TFT-Eigenschaften, insbesondere die Ausgangsstromstabilität, können jedoch die für GOA-TFTs erforderliche Umgebung mit hoher Strombelastung (HCS) nicht erfüllen [11,12,13], hauptsächlich aufgrund von zwei Merkmalen des BCE-Prozesses [14]. Die erste besteht darin, dass die Oberfläche eines a-IGZO-Films (Rückkanal von a-IGZO-TFT) S/D-Ätzmitteln ausgesetzt wird, die traditionell aus HNO3 . bestehen , H3 PO4 , und CH3 COOH, die eine schnelle Ätzrate aufweisen, die für a-IGZO-Filme nicht kontrollierbar ist [15]. Ein mildes H2 O2 -basiertes Ätzmittel mit stabiler Ätzung und minimaler Beschädigung der a-IGZO-Filme kann für das Ätzen der S/D-Elektrode (Cu-Metall) verwendet werden, aber eine Beschädigung der Oberfläche des a-IGZO-Films ist immer noch unvermeidlich [16]. Zweitens kann der direkte Kontakt des S/D-Metalls (Mo/Cu/Mo) mit dem a-IGZO-Film den TFT-Rückkanal verunreinigen [17]. Glücklicherweise kann ein Clean-Etch-Stopper-(CL-ES)-Prozess verwendet werden, der weniger kompliziert und kostspielig ist und die Kontamination minimiert, um a-IGZO-basierte TFTs mit verbesserter Gleichmäßigkeit und Stabilität für großflächige Displays herzustellen [18]. Obwohl der CL-ES-strukturierte TFT eine verbesserte Leistung zeigt, stellt sich die Frage, wie das Ätzmittel mit dem a-IGZO-Film reagiert und wie Cu + Diffusion in a-IGZO-Filme beeinflusst die Mikrostruktur und die Leistung der Geräte bleibt unklar.

In dieser Studie wurden a-IGZO-GOA-TFTs mit reduzierter Strukturgröße und sauberer Rückkanalstruktur über einen CL-ES-Prozess durch Batch-Ätzen von mehrschichtigem a-IGZO/Mo/Cu/Mo hergestellt. Darüber hinaus ist der Einfluss des Ätzmittels und Cu + Diffusion auf die Mikrostruktur und Leistung von CL-ES-strukturierten a-IGZO GOA TFT-Bauelementen werden untersucht und mit denen von BCE-strukturierten a-IGZO GOA TFT-Bauelementen verglichen. Noch wichtiger ist, dass die Ätzstoppschicht des CL-ES-Bauelements als S/D-Ätzschutzschicht sowie als Cu + . dient Diffusionssperrschicht, die hilft, die Anzahl von Defekten zu reduzieren und die Zuverlässigkeit der Hochstrombelastungszuverlässigkeit, SS-Werte, Hochstrombelastung und Schwellenspannungsschwankungen usw. zu verbessern. Daher liefert diese Arbeit einen direkten Beweis und eine aufschlussreiche Demonstration, dass die verbesserte Die Leistung von CL-ES-strukturierten TFTs korreliert stark mit ihrer CL-ES-Struktur und ihren sauberen Komponenten und bestätigt, dass der CL-ES-Prozess ein effizienter Weg für die Massenproduktion von Displays mit zufriedenstellender Leistung sein könnte.

Experimentelle Methoden

Herstellung von a-IGZO GOA TFTs

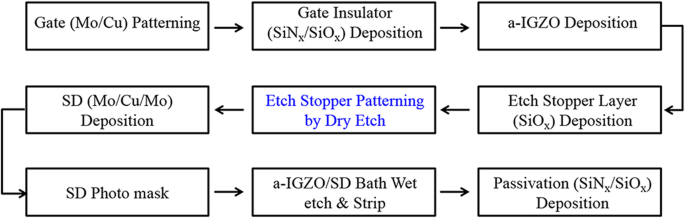

Die CL-ES-strukturierten a-IGZO-TFT-Bauelemente wurden über einen modifizierten fünfstufigen CL-ES-Prozess (Abb. 1) hergestellt, wie in unserer früheren Arbeit [15] beschrieben. Zuerst wurde die Gate-Elektrode mit Mo/Cu-Metall gebildet und der Gate-Isolator wurde mit einer SiNx/SiOx (3000 Å/1000 Å)-Doppelschicht unter Verwendung von PECVD bei 340 °C abgeschieden. Zweitens wurde ein a-IGZO-Film von 300 Å unter Verwendung von reaktivem DC-Magnetron-Sputtern bei Raumtemperatur mit einem Sauerstoffpartialdruck von 15% abgeschieden. Eine Ätzstoppschicht (SiOx, ESL) von 1000 wurde unter Verwendung von PECVD bei 240 °C abgeschieden und mit CF4 . reaktiv geätzt Plasma zum Strukturieren unter Verwendung der aktiven Photolithographiemaske des BCE-Prozesses als Ätzmaske. Für diesen Schritt wurde der a-IGZO-Film unter den ES-Schichtmustern vor der Exposition gegenüber dem CF4 . geschützt Plasma, während der Rest des a-IGZO-Films, der nicht durch die ES-Schichtmuster geschützt war, ebenfalls nicht geätzt wurde, sondern in einen leitfähigen Film umgewandelt wurde. Drittens wurden die Source-Drain-(S/D)-Elektroden (Mo/Cu/Mo-Dreifachschichten) durch Sputtern abgeschieden und unter Verwendung eines H2 . geätzt O2 Ätzmittel, das 0,2 Gew.-% eines Fluoridadditivs enthält, wobei die S/D-Photolithographiemaske und das ES-Schichtmuster als Ätzmaske dienen. Viertens wurde eine Passivierungsschicht von 3000 Å abgeschieden. Die nachfolgenden Prozesse waren denen einer typischen TFT-LCD-Backplane-Fertigung ähnlich.

Herstellungsprozess des a-IGZO GOA TFT

Zum Vergleich wurden a-IGZO-TFT-Bauelemente mit BCE-Struktur unter Verwendung des herkömmlichen BCE-Prozesses und derselben BCE-Maske hergestellt.

Charakterisierung

Die Morphologien, Mikrostrukturen und Zusammensetzungen der Proben wurden mit SEM (Camscan Mx2600FE), Röntgen-Photoelektronenspektroskopie (XPS, PHI Quantera II) und Flugzeit-Sekundärionen-Massenspektrometrie (IONTOF, TOF-SIMS 5) charakterisiert. . Elektrische Messungen wurden unter Verwendung eines Halbleitercharakteristikanalysators (Keysight 4082A) in einer dunklen Umgebung und bei 60 °C durchgeführt. Der Einfachheit halber wurde die HCS-Zuverlässigkeit über 1000 s mit V . bewertet gs bei 25 V und V ds bei 25 V. Während der Auswertung wurde der Zustand des GOA TFT durch Messung des I ds Strom in 1-s-Intervallen und der Trend des I ds Strom analysiert wurde. Das Ich d -V g Die Übertragungseigenschaften wurden ebenfalls in 100-s-Intervallen überwacht.

Ergebnisse und Diskussion

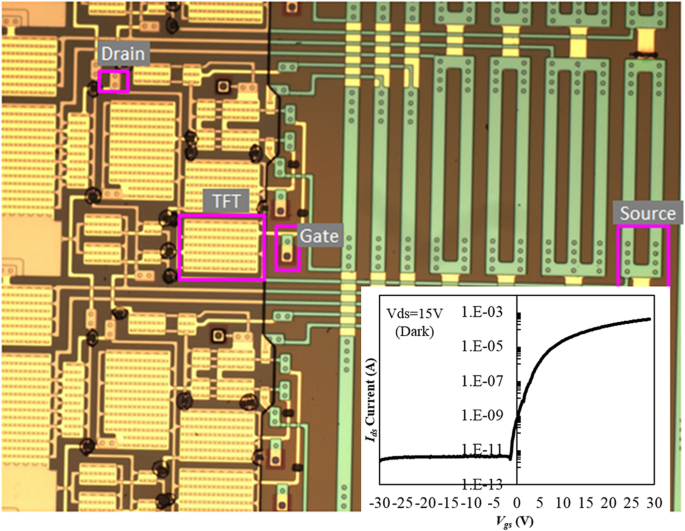

Das GOA-TFT-Gerät, das TFT-Kanäle sowie Gate-, Drain- und Source-Komponenten enthält, wie es durch den CL-ES-Prozess hergestellt wird, ist in Abb. 2 gezeigt. Um jede TFT-Charakteristik genau zu messen, wurden alle TFTs mit einem Laser getrennt, also unabhängig werden, so dass Gate, Source und Drain sich keinen Knoten mit irgendeinem anderen TFT teilen können. Wie durch die rote Linie in Abb. 2 gekennzeichnet, hat dieser TFT ein mehrkanaliges und getrenntes GOA-Strukturdesign mit einer Kanalbreite und -länge von 120 µm bzw. 10 µm, um die elektrischen Messungen zu erleichtern. Dieser TFT ist auch so konzipiert, dass er einen durchschnittlichen Stromfluss zu den einzelnen TFT-Kanälen hat, indem ein schwebendes Metallstück (in der Mitte der Kanäle) platziert wird, das jeden Kanal integriert. Vor der HCS-Zuverlässigkeitsbewertung wird die getrennte Betriebszuverlässigkeit zuerst durch Bewertung der elektrischen Interferenz des interessierenden TFT von den anderen peripheren TFTs bestätigt. In diesem Fall ist das Ich aus Der Rauschstrom der getrennten GOA-TFTs wird mit 3 pA gemessen (Kurve in Abb. 2 einfügen), was bestätigt, dass keine elektrischen Störungen von anderen GOA-Komponenten in der Nähe auftreten.

Fotos der GOA-TFTs, die elektrisch von den GOA-Schaltungen getrennt sind (Einfügen:I aus Rauschstrom zwischen dem interessierenden TFT und den anderen peripheren TFTs)

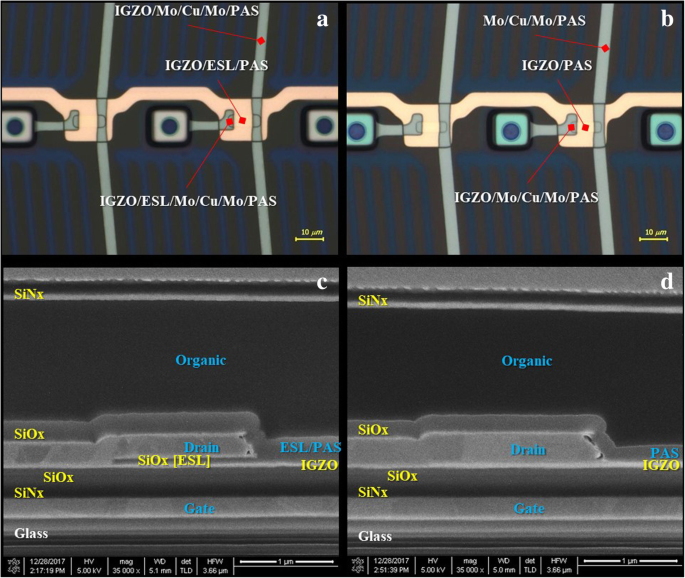

Mehrere Merkmalsgrößen der CL-ES-strukturierten TFTs und BCE-strukturierten TFTs werden gemessen und verglichen. Bei den CL-ES-strukturierten TFTs (Fig. 3a) betragen die Breite und Länge 4 µm bzw. 6 µm, ähnlich wie bei den BCE-strukturierten a-IGZO-TFTs in Fig. 3b. Im Allgemeinen ist der BCE-Prozess aufgrund seiner geringen Strukturgröße für die Oxid-TFT-Herstellung wünschenswert. Daher zeigen die erhaltenen CL-ES-strukturierten TFTs eine verringerte Strukturgröße und einen so hohen Integrationsgrad wie die BCE-strukturierten TFTs. Darüber hinaus ist die Querschnittsgröße der CL-ES-strukturierten TFTs ähnlich der der BCE-strukturierten TFTs (Abb. 3c, d), während die CL-ES-strukturierten TFTs eine ausgeprägte ES-Schicht aufweisen, die nicht beobachtet wird in den BCE-TFTs. Der CL-ES-Prozess bildet hauptsächlich ES-Muster, während der Batch-Ätzprozess auf mehrschichtigem a-IGZO/Mo/Cu/Mo mit ähnlichen Masken für die aktiven Muster und Source-Drain-Elektroden wie beim BCE-Prozess durchgeführt werden kann. Daher ist die Anzahl der beim CL-ES-Verfahren verwendeten photolithographischen Masken mit Ausnahme der ES-Muster die gleiche wie beim BCE-Verfahren. Dieser CL-ES-Prozess kann die erhöhte Anzahl von Masken des herkömmlichen ESL-Prozesses vermeiden und hat eine reduzierte Strukturgröße, was ihn für die Massenproduktion wirtschaftlich rentabel macht. Außerdem werden ohne die Verwendung der Halbtonbelichtung, ein Verfahren zur Vereinfachung des Verfahrens, das herkömmlich in der TFT-LCD-Industrie verwendet wird, die Verfahrenskomplikationen und die Herstellungskosten reduziert.

REM-Aufnahmen der a-IGZO-TFTs:a CL-ES-strukturierte TFT-Draufsicht, b BCE-strukturierte TFT-Draufsicht, c CL-ES-strukturierte TFT-Querschnittsansicht und d BCE-strukturierte TFT-Querschnittsansicht

Um die Oberflächendefekte der BCE-strukturierten TFTs während des BCE-Herstellungsprozesses weiter zu beobachten, wurde die Oberflächenzusammensetzung von a-IGZO-Filmen vor dem Tempern (Probe 1), nach dem Tempern (Probe 2) und nach der Exposition gegenüber H2 O2 Cu-Ätzmittel (Probe 3) wird mittels XPS untersucht. In den vollständig gescannten Spektren von a-IGZO-Filmen (Abb. 4a–c) existieren während des BCE-Herstellungsprozesses Peaks für In-, Ga-, Zn-, O- und C-Elemente. Wie in Abb. 4d gezeigt, zeigt der BCE-strukturierte TFT zwar keine signifikante Änderung in der Zusammensetzung der a-IGZO-Filme vor dem Tempern (Probe 1) und nach dem Tempern bei 330 °C für 1 h (Probe 2), aber signifikante Veränderungen sind beobachtet nach Exposition gegenüber nassen Chemikalien (Probe 3). Insbesondere Zink, das eine relativ niedrige Bindungsenergie mit Sauerstoff aufweist, wurde mit 4,82% in Probe 1 und 5,42% in Probe 2 gefunden, aber es ist auf 3,16% in Probe 3 gesunken. Indium weist eine minimale Variation in der Zusammensetzung zwischen . auf die unterschiedlichen Prozesse, und die relative prozentuale Änderung von Zn in Bezug auf In ist enorm, nämlich 44,1%, 46,0% bzw. 27,6% für die Proben 1, 2 bzw. 3. Ähnlich verhält es sich mit Gallium, das ebenfalls eine starke Bindungsaffinität zu Sauerstoff aufweist. Mit anderen Worten, während des Nassätzprozesses traten auf der freigelegten Rückseite des Oxidhalbleiters unerwünschte Defekte auf, einschließlich eines wesentlichen Verlustes von Zn und Ga. Die Gründe für dieses Phänomen können mit ihren unterschiedlichen Bindungsenergien an Sauerstoff und den unterschiedlichen Molekülstrukturen des a-IGZO-Films zusammenhängen [19].

XPS-Analyse der Oberflächenzusammensetzung der a-IGZO-Dünnschichten a vor dem Glühen, b nach dem Tempern und c nach Exposition gegenüber H2 O2 Cu-Ätzmittel während des BCE-Prozesses. d Entsprechende Atomprozentsätze für den obigen Prozess

Es ist bekannt, dass die chemische Beständigkeit von a-IGZO-Filmen gegenüber sauren Ätzmitteln sehr schwach ist [20]. Insbesondere der abrupte Verlust von Zn, von dem angenommen wird, dass er die Molekülstruktur von a-IGZO bestimmt, verursacht eine Schwächung der Oberflächenstruktur der a-IGZO-Filme. Darüber hinaus kann die Reduktion von Ga, das die Ladungsträgererzeugung durch seine starke Bindungsenergie mit Sauerstoff unterdrückt, die Wahrscheinlichkeit der Bildung von Sauerstoffleerstellen [Vo] erhöhen [21]. Daher können BCE-strukturierte GOA-TFTs Ätzschäden am TFT-Rückkanal selbst bei relativ mildem H2 . nicht vermeiden O2 -basiertes Cu-Ätzmittel.

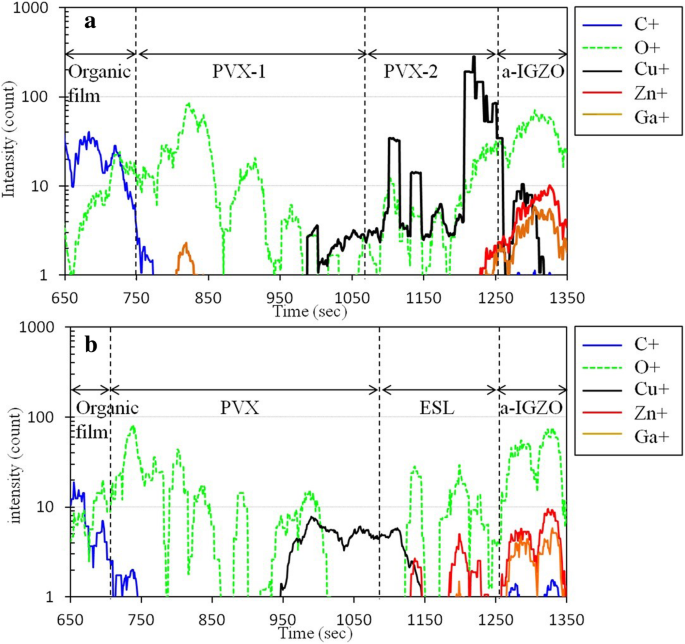

Um den Schutz der ES-Schicht zu bestätigen, wird die Zusammensetzung des a-IGZO-TFT-Kanalbereichs unter Verwendung von TOF-SIMS für Proben untersucht, die durch die BCE- und CL-ES-Prozesse (Clean Etch Stopper) hergestellt wurden (Abb. 5). Da Cu + in dem a-IGZO-Film Defekte vom Akzeptortyp erzeugen und Elektronen einfangen können, muss der a-IGZO-TFT-Kanal sauber sein, um die elektrische Stabilität zu erhöhen. Wie beobachtet, ist das Cu + Der in der BCE-Probe nachgewiesene Peak ist 20-mal höher als der der CL-ES-Probe. Darüber hinaus ist der Nachweisbereich von Cu + überlappt mit der Detektionsregion von Zn + und Ga + weitgehend (Abb. 5a). Diese Ergebnisse zeigten, dass die a-IGZO-Filme in den BCE-strukturierten TFTs durch Cu + . verunreinigt sind aufgrund des direkten Kontakts des a-IGZO-Films im TFT-Rückkanalbereich mit dem Cu-Metall. Für die CL-ES-strukturierten TFTs (Abb. 5b), Cu + wird nur im ES-Bereich nachgewiesen, was darauf hinweist, dass ein direkter Kontakt des a-IGZO-TFT-Kanalbereichs mit dem Cu-Metall vermieden wird. Überraschenderweise ist eine beträchtliche Menge an Zn + erscheint in der ESL. Das zerstreute Zn + wird durch die höheren Plasmabedingungen und Druckbedingungen der Vorbehandlung während der ESL-Abscheidung verursacht. Daher ist die ES-Schicht in CL-ES-strukturierten TFTs wesentlich, um die elektrische Stabilität zu verbessern, indem Oberflächenschäden und Kontamination der a-IGZO-Filme vermieden werden.

TOF-SIMS-Analyse der Kanalregionen von a-IGZO-TFTs, die über a . hergestellt wurden BCE und b die CL-ES-Prozesse

Die Bewertung der Hochstrombelastung (HCS) für die CL-ES- und BCE-strukturierten GOA a-IGZO-TFTs ist in Abb. 6a dargestellt. Für die gleichen Feature-Größen ist das anfängliche I ds Der Strom des CL-ES-strukturierten TFT beträgt 429 µA, was höher ist als der des BCE-strukturierten TFTs (343 µA). Nach der HCS-Bewertung für 1000 s wird das I ds Strom des CL-ES-strukturierten TFT beträgt 352 μA, ungefähr 82,2 % seines Anfangswertes. Im Gegensatz dazu ist das Ich ds Der Reststrom des BCE-strukturierten TFT ist auf 183 μA gesunken und behält nur noch 53,5% seines Ausgangswertes. Darüber hinaus wird durch Extrapolation (Abb. 6b) das I ds Der Reststrom des CL-ES-strukturierten TFT wird voraussichtlich 302,6 µA betragen und 70,5% seines Anfangswertes nach 10.000 µs beibehalten. Für den BCE-strukturierten TFT ist das I ds Der Reststrom sinkt stark auf 111,7 μA und behält nur 33,7% seines Anfangswertes bei. Daher kann der Integrationsgrad für den über den CL-ES-Prozess hergestellten GOA-TFT bei den gleichen Ausgangseigenschaften um bis zu 271% im Vergleich zu dem des BCE-Prozesses gesteigert werden.

a Experimentelle Daten für 1000 s und b Extrapolation für die HCS-Langzeitbewertung der CL-ES- und BCE-strukturierten GOA-TFTs

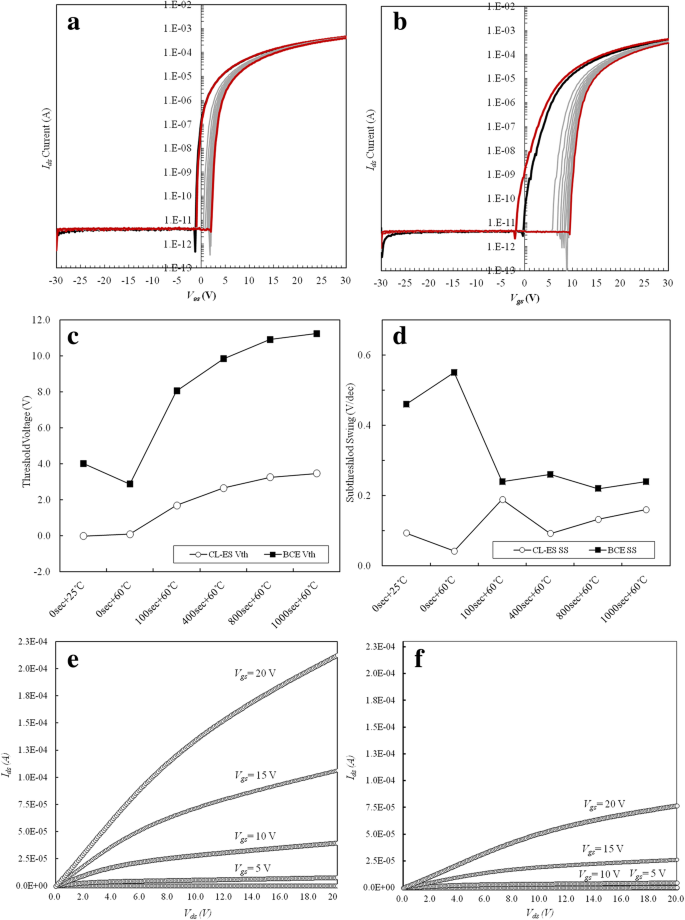

Außerdem ist das Ich -V Die Übertragungseigenschaften von sowohl CL-ES- als auch BCE-strukturierten GOA-TFTs während der HCS-Zuverlässigkeitsbewertung werden ebenfalls gemessen (Abb. 7 und Tabelle 1). Für CL-ES-strukturierte TFTs (Abb. 7a) beträgt die Schwellenspannung 0,0 V bei der anfänglichen HCS-Bewertung (25 °C) und 3,5 V nach der HCS-Bewertung bei 60 °C für 1000 s. Darüber hinaus verschiebt sich die Schwellenspannung bei einer Gesamtänderung (ΔV te ) von 3,5 V. Der Unterschwellenwert der Schwingung (SS) wird leicht von 0,09 auf 0,16 V/Dez erhöht. Für den BCE-strukturierten TFT ist die Schwellenspannung viel höher, nämlich 4,0 V bei 25 °C, und steigt auf 11,2 V nach HCS-Bewertung bei 60 °C für 1000 s an. Ein möglicher Grund für diese hohen Schwellenspannungen ist die Diffusion von Cu + in den a-IGZO-Film während des Nassätzprozesses des BCE-Prozesses. Cu + kann in a-IGZO-Filmen als Akzeptor-Defektstellen fungieren, und eine hohe Dichte von Cu + kann eine große Anzahl von Elektronen einfangen. Die eingefangenen Elektronen erzeugen ein abgeschirmtes Coulomb-Potential, das zum Phänomen der vorübergehenden Schwellenspannungsverschiebung führt. Im Allgemeinen können die Masse des Gate-Isolators und die neu gebildeten Defektstellen innerhalb der Masse der a-IGZO-Filme den SS-Wert von TFTs erhöhen [11]. Diese Ergebnisse erklären eindeutig die Abnahme des I ds Fehlerstrom in den BCE-strukturierten TFTs. Der SS-Wert des BCE-strukturierten TFT zeigt jedoch eine Tendenz, von 0,46 auf 0,24 V/dec zu sinken. Dieser abnehmende SS-Wert resultiert aus der Ansammlung von Elektronen in der Nähe der a-IGZO-Grenzfläche, wonach der Gate-Isolator schnell die hohen Niveaus der ursprünglich vorhandenen Einfangstellen vom Akzeptortyp auffüllen kann. Darüber hinaus werden die Fallenstellen schneller gefüllt, als sie durch das HCS erzeugt werden, und daher nimmt die Anzahl der eingefangenen Elektronen mit der Zeit allmählich ab. Dies stimmt mit dem sich positiv verschiebenden Verhalten der Schwellenspannung überein.

Ich -V Übertragungseigenschaften gemessen während der HCS-Bewertung von a die CL-ES und b die BCE-strukturierten GOA-TFTs. Verhalten von c die Schwellenspannung und d der unterschwellige Swing in Intervallen von 1000 s und V ds = 15 V. Die anfänglichen Messungen des I d -V d Ausgangscharakteristik für e die CL-ES- und f die BCE-strukturierten GOA-TFTs mit V gs = 0, 5, 10, 15 und 20 V

Was die Einheitlichkeit der Eigenschaften für CL-ES betrifft, da ESL einen aktiven Rückkanalschutz vor Cu + . bietet Kontamination und Ätzmittelschäden ist das Ergebnis im Vergleich zu BCE stabil. Darüber hinaus ist zu beachten, dass die Charakteristiken der Outputkurve für BCE keine Unterschiede aufweisen und eine CL-ES-Produktion und -Stabilität versprechen können (Tabelle 2, Abb. 7e, f).

Abbildung 7 c und d zeigen die Ergebnisse des unterschwelligen Ausschlags und des Schwellspannungsverhaltens zusammen mit dem Fortschritt der HCS-Bewertung. Im Allgemeinen nimmt der Swing-Wert unter dem Schwellenwert des GOA-TFT allmählich zu, wie für den CL-ES-strukturierten TFT zu sehen ist (Fig. 7d). Der TFT mit BCE-Struktur zeigt jedoch ein anormales Verhalten, wobei der unterschwellige Swing-Wert anfänglich zunimmt und anschließend während der HCS-Bewertung abnimmt. Der SS-Wert des BCE-strukturierten TFT steigt von 0,46 auf 0,55 V/dec, wenn die Substrattemperatur von 25 auf 60°C erhöht wird. Gleichzeitig verschiebt sich die Schwellenspannung negativ von 4,0 auf 2,9 V (Abb. 7c). Dieses abnormale Phänomen resultiert aus der Beschädigung der a-IGZO-Filmoberfläche durch das H2 . O2 Ätzmittel mit Fluoridzusatz. Wie bereits erwähnt, impliziert die Oberflächenschädigung der a-IGZO-Filme einen Mangel an Zn-, Ga- und Sauerstoffatomen, was zahlreiche Defektstellen einschließlich Sauerstoffleerstellen bildet. Es wird angenommen, dass diese Defektstellen als flache Donor-ähnliche Zustände aktiv sind, die nahe am minimalen Leitungsband liegen, und zur thermischen Anregung fähig sind und als Elektronenquellen für das Leitungsband wirken, was zu einer Degradation des a- IGZO TFT-Eigenschaften. Basierend auf den obigen Ergebnissen ist der CL-ES-strukturierte TFT mit kleinen akzepterähnlichen Zuständen und Sauerstoffmangel, die als flache Donor-ähnliche Zustände wirken, eine viel bessere Struktur als der BCE-strukturierte TFT.

Schlussfolgerung

Zusammenfassend zeigen wir, dass CL-ES-strukturierte GOA-TFTs mit einer verringerten Größe der Bauelemente und einer sauberen Ätzstoppschicht die Leistung und Stabilität des Bauelements erheblich verbessern können. Mit dem vorgeschlagenen CL-ES-strukturierten TFT-Herstellungsverfahren werden die Beschädigung und Kontamination des TFT-Rückkanals minimiert. Darüber hinaus kann der CL-ES-strukturierte TFT-Prozess bei gleichem Integrationsgrad wie der des BCE-strukturierten GOA-TFTs die Ziele des ästhetischen Designs und der Herstellungskosteneffizienz erfüllen. Der CL-ES-strukturierte GOA-TFT zeigt im Vergleich zum BCE-strukturierten GOA-TFT eine hervorragende elektrische Leistung, einschließlich eines viel höheren Restionenstroms (~ 187%), viel niedrigerer anfänglicher SS-Wert (0,09 V/Dez) und a viel geringere Schwankung der Schwellenspannung (3,5 V). Dies impliziert die Möglichkeit von GOA-Designs mit viel höherer Integration und Zuverlässigkeit. Die verbesserte Leistung und Stabilität legen nahe, dass der CL-ES-strukturierte TFT mit einem vereinfachten Prozess und einer sauberen Ätzstoppschicht die durch Sauerstoffmangel verursachten Donor-ähnlichen Defekte und die durch Cu + . verursachten akzeptorähnlichen Defekte erfolgreich überwindet Diffusion während des BCE-Prozesses. Daher ist eine saubere Oberflächenzusammensetzung für den a-IGZO-Kanalbereich in CL-ES-strukturierten TFTs wichtig für die Herstellung von a-IGZO-TFT-Backplanes mit hochzuverlässigen, hochauflösenden und schmalen Displays.

Abkürzungen

- TFT:

-

Dünnschichttransistor

- GOA:

-

Gate-Drive-IC auf Array

- a-IGZO:

-

Amorphes Indium-Gallium-Zink-Oxid

- LCD:

-

Flüssigkristallanzeige

- PEVCD:

-

Plasmaunterstützte chemische Gasphasenabscheidung

- ESL:

-

Ätzstoppschicht

- BCE:

-

Rückkanalätzung

- HCS:

-

Hohe Strombelastung

- SiOx:

-

Siliziumoxid

- SiNx:

-

Siliziumnitrid

- SS:

-

Schwung unterhalb der Schwelle

Nanomaterialien

- Entwerfen mit Bluetooth Mesh:Knoten und Funktionstypen

- MCUs bieten verbesserte Leistung, Konnektivität und Sicherheit

- Zuverlässigkeit steigern und Wartungsergebnisse verbessern mit maschinellem Lernen

- Unterschied zwischen Struktur und Klasse:Erklärt mit C++-Beispiel

- Frequenzmodulation und Absorptionsverbesserung von THz-Mikrobolometern mit Mikrobrückenstruktur durch spiralförmige Antennen

- Morphologie, Struktur und optische Eigenschaften von Halbleiterfilmen mit GeSiSn-Nanoinseln und gespannten Schichten

- Verbesserung der Leistung von a-IGZO-TFT-Geräten durch einen sauberen Schnittstellenprozess durch Ätzstopper-Nanoschichten

- Reduzierter Kontaktwiderstand zwischen Metall und n-Ge durch Einfügen von ZnO mit Argon-Plasmabehandlung

- Lateraler, doppelt diffundierter Metall-Oxid-Halbleiter-Transistor mit extrem niedrigem spezifischen On-Widerstand mit verbessertem Dual-Gate und partieller P-vergrabener Schicht

- IBM:Proaktive Gewährleistung von Zuverlässigkeit und Sicherheit mit EAM