Testmusterdesign für plasmainduzierte Schäden an einem intermetallischen Dielektrikum in FinFET-Cu-BEOL-Prozessen

Zusammenfassung

Verbindungen mit hoher Dichte, die durch fortschrittliche CMOS-Cu-BEOL-Technologien ermöglicht werden, führen zu eng platzierten Metallschichten. Metallleitungen mit hohem Seitenverhältnis erfordern umfangreiche Plasmaätzprozesse, die bei den Inter-Metal-Dielektrikum-(IMD)-Schichten zu Zuverlässigkeitsproblemen führen können. Diese Studie präsentiert neu vorgeschlagene Testmuster zur Bewertung der Wirkung des plasmainduzierten Ladungseffekts auf die Integrität von IMD zwischen eng platzierten Metallleitungen. Starke Korrelationen zwischen Plasma-Aufladungsintensitäten und Schäden in IMD-Schichten werden gefunden und umfassend analysiert.

Einführung

Cu-basierte Back-End-of-Line-(BEOL)-Prozesse wurden in großem Umfang verwendet, da Technologien in den Bereich unter 100 nm übergehen. Dicht gepackte Verbindungen bestehen aus Vias mit hohem Aspektverhältnis und Metallleitungen werden durch eine Reihe von plasmaunterstützten Ätzprozessen ermöglicht [1,2,3]. Es ist allgemein bekannt, dass Behandlungen mit hochenergetischem Plasma zu signifikanter Degradation und latenten Schäden in Gate-Dielektrikumstapeln von Transistoren führen können, von denen angenommen wird, dass sie der Hauptentladungspfad während prozessinduzierter Ladevorgänge sind. Um Bedenken hinsichtlich der Zuverlässigkeit der Gatedielektrikumsqualität zu vermeiden, stellen IC-Hersteller in der Regel Designerregeln und -richtlinien bereit, die die Größe und Länge von Verbindungsmetallschichten begrenzen [4, 5]. Bei einer erhöhten Anzahl von Metallschichten in den komplexen Verdrahtungssystemen ist es schwer, den Entladungspfad durch den dielektrischen Zwischenmetallfilm während des prozessinduzierten Ladens zu vermeiden. Mit der Einführung von Low-k-Material in BEOL-Prozessen [6, 7] wurden die Probleme mit der RC-Verzögerung gemildert und die Isolationsschichten können anfälliger für Ladungsspannungen sein [8, 9]. Die Schäden, die aus durch Plasmaladung induzierten Belastungen an kompakten Verbindungsstrukturen resultieren, die für die Realisierung der komplizierten BEOL-Verdrahtungen verantwortlich sind, können die Ausbeute und Zuverlässigkeit fortschrittlicher CMOS-ICs stark beeinträchtigen. In diese Studie integrieren wir die zuvor berichteten In-situ-PID-Rekorder [10,11,12] mit neu vorgeschlagenen differentiellen Testmustern zur Überwachung ihrer möglichen IMD-Schädigung, wenn ein zusätzlicher Entladungspfad unter fortschrittlichen Cu-BEOL-Prozessen möglich wird. Die vom Rekorder an verschiedenen Stellen über den Wafer gemeldeten Plasmaladungspegel können durch die neuen Testmuster mit Plasmaladungsschäden auf IMD-Filmen korreliert werden. Stressinduziertes Fehlerverhalten der IMD-Strukturen kann dann leicht durch diese Testmuster aufgedeckt werden, die in Standardteststrukturen für die routinemäßige Überwachung neuer Fehlermodi und möglicher IMD-Zuverlässigkeitsprobleme verwendet werden können.

Gerätestruktur und Methodik

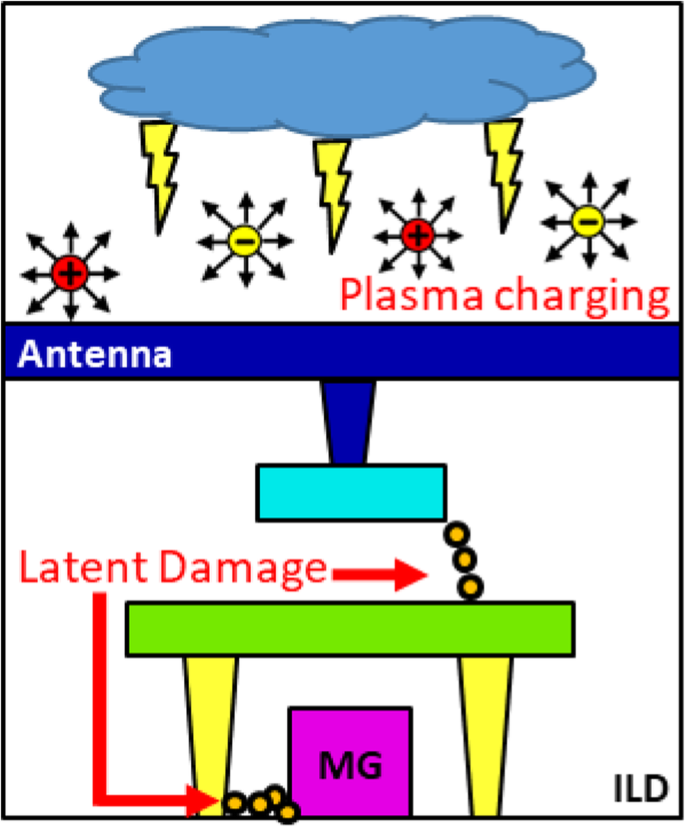

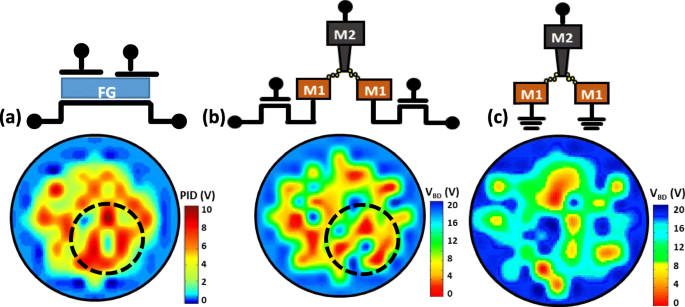

Die Ergebnisse der Fehleranalyse bei FinFET-integrierten Schaltungen deuten darauf hin, dass latente Schäden durch erhöhte Fallenzustände innerhalb der dielektrischen Zwischenmetallschichten zwischen zwei eng platzierten isolierten Verbindungsstrukturen auftreten können, wie in Abbildung 1 dargestellt. Da die Linienbreite und der Abstand zwischen Durchgangs- und Metallverbindungen CMOS-BEOL-Prozesse im Voraus aggressiv reduzieren, Ladungen sammeln sich auf großen Metalldrähten, dienen als Antennen, können sich durch IMD über Metalle und Vias/Gates und Metalldrähte entladen, was zu Hochfeld- und/oder Hochstrombelastungen auf diesen dielektrischen Filmen führt. Indem der In-situ-PID-Rekorder [10,11,12] neben den beiden differentiellen Testmustern auf jedem Chip platziert wird, können zunächst die Referenzplasmaladungspegel über einen 12-Zoll-Wafer ermittelt werden.

Plasmainduzierte Schäden in intermetallischen dielektrischen Schichten zwischen dicht gepackten Verbindungsmustern können zu einer latenten Verschlechterung der Isolationsintegrität führen

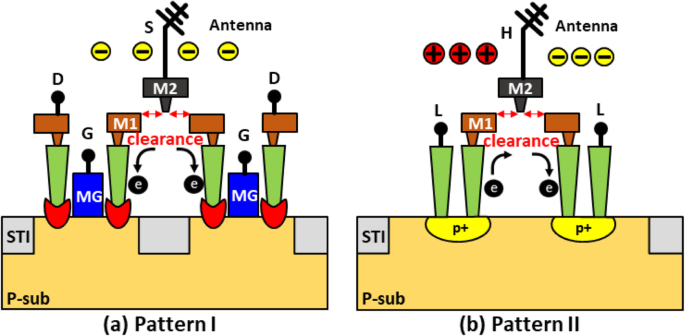

Um sicherzustellen, dass der Plasma-Ladestrom durch die dielektrische Schicht zwischen den Metallschichten fließt, wird der M2-Knoten auf dem Testmuster in Fig. 2 vor der Herstellung der Antennenstruktur isoliert. Zwei neue differentielle Testmusterdesigns, die darauf abzielen, die Wahrscheinlichkeit des Verursachens des latenten Schadens während der Plasmaladungsspannungen zu erhöhen, werden vorgeschlagen und in 2a, b dargestellt. Das Gerät mit Typ-I-Muster erfährt nur dann eine hohe Strombelastung, wenn Elektronen an seiner entsprechenden Antenne gesammelt werden. Dies liegt daran, dass der Entladestrom durch den n+/p-Übergang in Reihe auf dem leitfähigen Pfad gleichgerichtet wird. Während das Gerät mit Typ-II-Muster Belastungen I in beide Richtungen ausgesetzt ist [13]. Auf dieser Überwachungsvorrichtung werden nämlich sowohl die Ionenladung als auch die Elektronenladung registriert. Folglich werden die Proben in dieser Studie mit dem Standard-FinFET/Cu-BEOL-Prozess in einem 16-nm-Technologieknoten hergestellt. Die Antennenstrukturen auf einem PID-Rekorder sowie die auf jedem Chip platzierten Geräte mit Mustern vom Typ I und II sind alle mit einer großen Metallstruktur ausgestattet. Beide Arten von Überwachungsgeräten sind mit einer Differenzkonfiguration ausgestattet, die das Fehlausrichtungsrauschen, das zu Fehlermessungen bei den PID-Effekten führen könnte, verstärken und anschließend minimieren kann.

Illustrationen von neu vorgeschlagenen differentiellen Testmustern, die entwickelt wurden, um die Wirkung latenter Schäden durch Plasma-induzierte a . hervorzuheben negativ und b bidirektionale Spannungen, bei denen der Abstand zwischen den Metallschichten auf 14 nm

. eingestellt wirdExperimentelle Ergebnisse und Diskussion

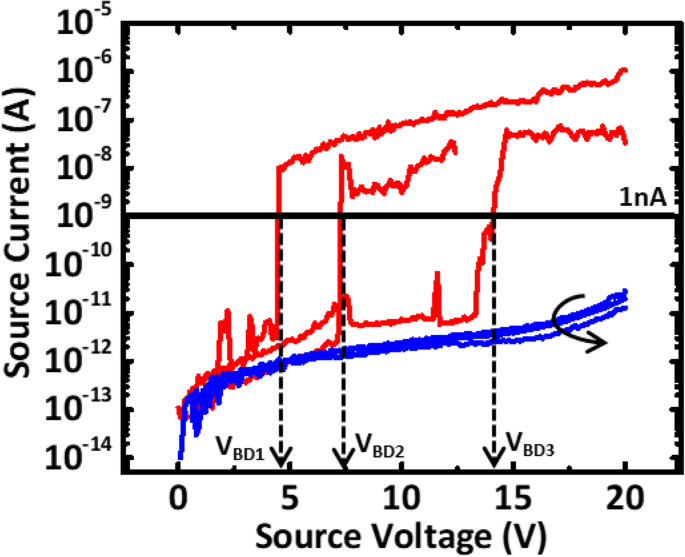

Die Daten in Abb. 3 werden durch Anlegen eines Spannungssweeps an Metall 2 von 0–20 V mit einer Wobbelrate von 0,7 V/s erhalten, während die Durchbruchspannung und der IMD-Leckstrom auf beiden Seiten einiger verschiedener Geräte mit Testmuster Ich kann dann abgerufen und verglichen werden. Bei der Herstellung der großen M3-Antenne von 82.000 μm 2 , wird erwartet, dass der Plasmaprozess eine Aufladung der Antenne induziert. Es wird erwartet, dass sich die angesammelte Ladung über den Pfad mit dem niedrigsten Widerstand entlädt. Die Daten zeigen, dass einige Proben einen frühen dielektrischen Durchschlag aufweisen, während die IMD bei anderen Geräten mit geringem Leckstrom relativ intakt bleibt.

Ableitstrom gemessen an Geräten mit differentiellen Testmustern, die an eine Metall-3-Antenne von 82.000 μm 2 . angeschlossen sind . V BD ist definiert als die Spannung, bei der der Strom 1 nA bei einer Durchgangslänge von 32 nm erreicht

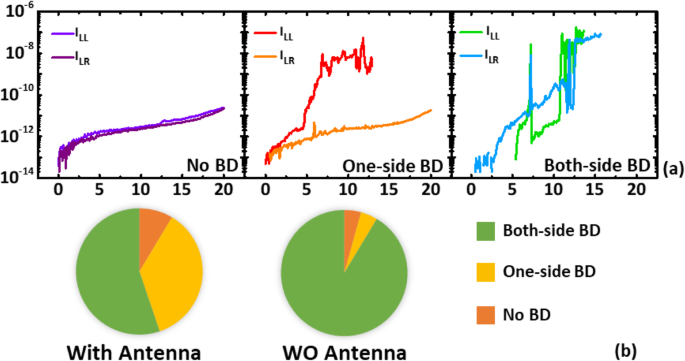

Bei einem Ladevorgang wird erwartet, dass die schwächere Seite dem dominanten Entladepfad dient, was zu einem ausgeprägteren Ungleichgewicht des Schadensniveaus zwischen links und rechts führt. Daher sind nur die Geräte mit großem V BD Unterschiede zwischen der linken und der rechten Seite sind wahrscheinlicher auf die Plasmaladung zurückzuführen. Daher ist das kleinere V BD in der IMD-Aufschlüsselung eines Paares wird als das Niveau registriert, das mit dem PID-Stressniveau korreliert. Abbildung 4a zeigt drei typische Arten von Eigenschaften, die auf Proben auf verschiedenen Chips auf einem Wafer gefunden werden. Diese Proben können in Gruppen ohne Aufschlüsselung auf einer Seite, einseitige Aufschlüsselung oder zweiseitige Aufschlüsselung eingeteilt werden. Der Teil der Geräte, der die besonderen Eigenschaften jeder Gruppe zeigt, ist im Tortendiagramm von Fig. 4b gezeigt. Wir haben festgestellt, dass bei Proben ohne Antenne eine viel geringere Änderung der einseitigen Durchschlagscharakteristika vorliegt. Symmetrisches Verhalten auf beiden Seiten findet sich bei den meisten Geräten, die keiner Plasmaladungsbelastung ausgesetzt waren. Diese weisen ferner darauf hin, dass die meisten der asymmetrischen Eigenschaften in einem Differentialpaar von Ladespannungen herrühren, wenn eine Antennenstruktur angebracht ist.

a Verschiedene Arten von Durchschlagseigenschaften der Testpaare über einen Wafer und b Vergleich des Prozentsatzes von Proben, die unterschiedliche Arten von Durchschlagseigenschaften auf Gerätepaaren über 60 Chips aufweisen

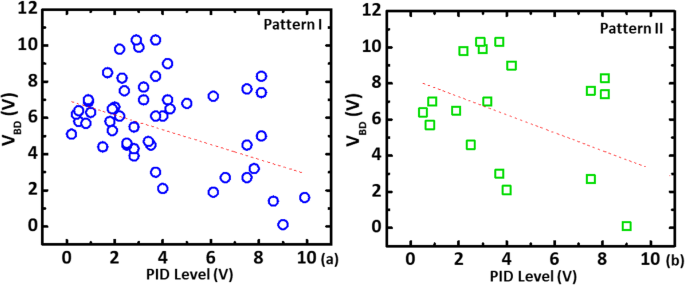

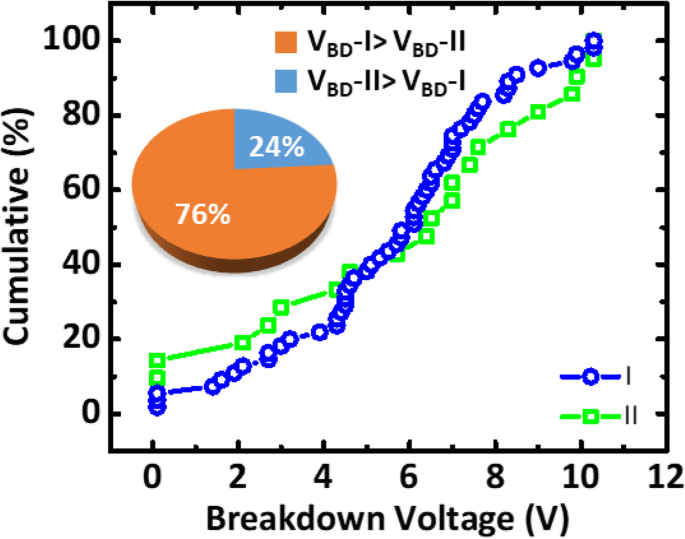

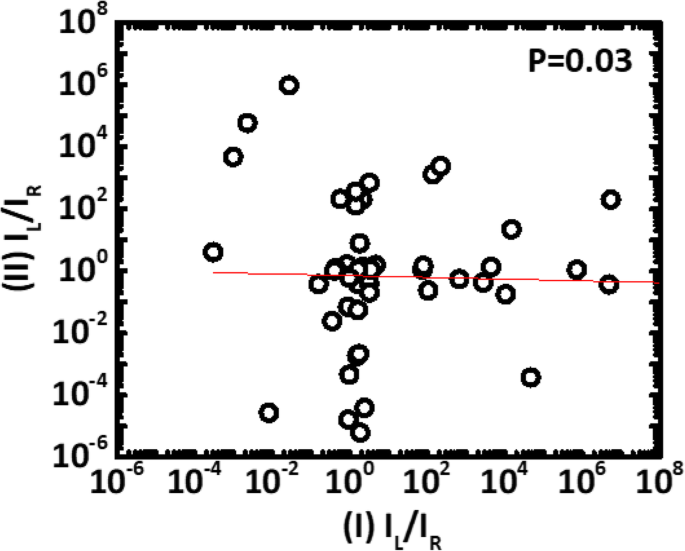

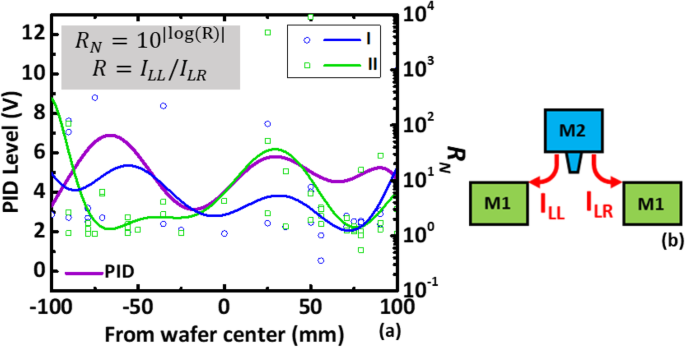

Verwenden des V BD erhalten durch das obige Verfahren, die Wafer-Maps des PID-Niveaus und V BD von Geräten der Muster I und II sind in Abb. 5 verglichen. Hohe Ähnlichkeit zwischen Wafer-Maps der V BD von beiden Arten von Überwachungsgeräten und die entsprechenden Referenzladestände werden vom PID-Rekorder erhalten, siehe Abb. 5a. Es wird angenommen, dass die PID-Spannung sowohl Elektronen- als auch Ionen-Ladungsereignisse während Metallprozessen aufzeichnet [14]. Es wurde jedoch festgestellt, dass Proben über einen Wafer hinweg überwiegend einer stärkeren Elektronenladung als einer Ionenladung unterliegen [14]. Wir glauben, dass zwischen den Wafern in Abb. 5a, b eine gewisse regionale Korrelation zu sehen ist. Während die Wafer-Map in Fig. 5c aus Muster II, die keine offensichtliche Ähnlichkeit mit der in Fig. 5a aufweist, darauf hindeutet, dass bidirektionaler Stress [15] zu sekundären Effekten auf die dielektrischen Schichten führen könnte, die weiterer Untersuchung bedürfen. Gemessene Durchbruchspannungen aus den neuen Testmustern gegenüber den Referenz-PID-Werten im Vergleich in Fig. 6 zeigen weiter, dass je höher der PID-Wert auf einem Chip ist, desto niedriger seine V BD die neuen Testmuster. Darüber hinaus sind signifikante negative Korrelationen zwischen V BD und Plasma-Ladeniveaus können hergestellt werden. Um die Wirkung von ein- und bidirektionalen Belastungen auf IMD-Schäden zu untersuchen, V BD gemessen von mit Typ-I- und Typ-II-Mustern entwickelt, ist in Abb. 7 zusammengefasst und verglichen. Die V BD Verteilung, die von Geräten auf 60 Chips über Wafer erhalten wird, zeigt, dass die Geräte, die bidirektionalen Ladebelastungen ausgesetzt waren, wahrscheinlicher einen IMD-Durchbruch bei einer niedrigeren Spannung zeigen. Dies könnte durch das asymmetrische Stressniveau erklärt werden, wenn sich die Polarität über eine IMD ändert [16]. Darüber hinaus ist der spannungsinduzierte Leckstrom (SILC), gemessen mit 10 V über der dielektrischen Schicht, ein weiterer Indikator für die Zunahme von Fallenzuständen [17] innerhalb des IMD-Films. Um den durch Prozessvariationen verursachten Variationseffekt von Chip zu Chip weiter zu minimieren, wird das Leckverhältnis von jedem Paar als Index verwendet, um den IMD-Schaden weiter zu bewerten. Abbildung 8 zeigt, dass es im Wesentlichen keine Korrelation zwischen dem Leckstromverhältnis der beiden Gerätetypen auf demselben Chip gibt. Das heißt, dass eine Fehlausrichtung zwischen Metall-1- und Via2-Schichten minimale Auswirkungen auf beide Muster hat. Habe festgestellt, dass das aktuelle Verhältnis R , definiert als ich LR /Ich LL , ist ein besserer Index, um Rauschen von Chip-zu-Chip-Variationen dieser Muster zu entfernen. Bei vollständig erwartungsfreien Geräten tritt die Hauptladebelastung rechts oder links auf, die völlig zufällig sein sollte. Hier finden sich einige Bias-Effekte auf die Stromverhältnisse, bei denen das Verteilungsmedium nicht bei 1 liegt. Um sicherzustellen, dass nur die Schäden berücksichtigt werden, die aus den Plasmaladungseffekten resultieren, R ist das normalisierte Stromverhältnis, wie in Abb. 9 beschrieben. Im Verteilungsdiagramm über die Wafermitte ist R N von Geräten des Typ-I-Musters folgt mit dem Plasma-Stress-Level von PID-Rekordern ziemlich nahe. Andererseits R N von Geräten, die für bidirektionale Belastungen anfällig sind, können durch die aufgezeichneten PID-Werte nicht vollständig erklärt werden. Dies könnte durch einen deutlich höheren R . verursacht werden N Pegel in Vorrichtungen des Musters II als Ergebnis von zusätzlichen Ionenladungsereignissen über dem Wafer.

Schemata und Wafer-Maps mit den Verteilungen von (a ) die PID-Spannung und VBD von (b ) Testmuster I und (c ).

Korrelationen zwischen VBD aus PID-Werten für a Muster I und b Muster-II-Samples bzw. [10,11,12]

Vergleich der kumulativen Verteilung von V BD von 60 Chips über den Wafer und der Teil der Proben, der höhere Durchbruchspannungen von Muster I im Vergleich zu Muster II zeigt

Das Leckstromverhältnis der linken und rechten Seite von Muster I und II zeigt, dass es bei diesen Proben keinen systematischen Fehlausrichtungseffekt gibt

a Normalisierte Stromverhältnisse von Muster-I- und Muster-II-Proben über die Wafermitte im Vergleich zu den entsprechenden PID-Werten und b links die Definition des Ableitstroms (I LL ) und rechts (ich LR )

Schlussfolgerungen

Der plasmainduzierte Ladungseffekt auf die Integrität von IMD-Filmen wird durch neu vorgeschlagene differentielle Testmuster auf fortschrittlichen FinFET-Cu-BEOL-Plattformen untersucht. Es wurde festgestellt, dass Schäden in Form von frühem Durchschlag und erhöhtem SILC in IMD-Schichten direkt mit den Plasmaladungsniveaus auf 12-Zoll-Wafern korreliert sind.

Verfügbarkeit von Daten und Materialien

Nicht zutreffend.

Nanomaterialien

- Eine Einführung in die Metallherstellung

- 6 wichtige Designüberlegungen für den 3D-Metalldruck

- Design for Manufacturability-Richtlinien – Teil 1

- 5 Tipps für die Blechkonstruktion

- 6 Tipps zur Optimierung Ihres Designs für ein Metallfertigungsprojekt

- Was ist Metallidentifizierung? - Tests und Tipps zur Identifizierung

- Optimieren von Designs für Metallfertigungsprojekte

- Überlegungen zum Impedanzdesign für starrflexible PCB

- Designtipps zum Biegen von Blech

- Designtipps für den 3D-Druck mit direktem Metall-Lasersintern