Ge-N-Kanal-MOSFETs mit ZrO2-Dielektrikum für verbesserte Mobilität

Zusammenfassung

Hochmobile Ge-nMOSFETs mit ZrO2 Gatedielektrikum werden demonstriert und mit Transistoren mit unterschiedlichen Grenzflächeneigenschaften von Ozon (O3 ) Behandlung, O3 Nachbehandlung und ohne O3 Behandlung. Es zeigt sich, dass mit O3 Behandlung, die Ge nMOSFETs mit ZrO2 Dielektrikum mit einem EOT von 0,83 nm erhält eine maximale effektive Elektronenmobilität (μ eff ) von 682 cm 2 /Vs, die höher ist als die der universellen Si-Mobilität bei mittlerer Inversionsladungsdichte (Q inv ). Auf der anderen Seite die O3 Nachbehandlung mit Al2 O3 Grenzschicht kann eine dramatisch verbesserte μ eff , erreicht etwa 50 % μ eff Verbesserung im Vergleich zur Si-Universalmobilität bei mittlerem Q inv von 5 × 10 12 cm −2 . Diese Ergebnisse zeigen die potenzielle Verwendung von ZrO2 Dielektrikum in Hochleistungs-Ge-nMOSFETs.

Hintergrund

GERMANIUM (Ge) hat im Vergleich zu Si-Bauelementen Vorteile einer höheren Trägermobilität und einer niedrigeren Verarbeitungstemperatur gezeigt. Diese machen Ge zu einer Alternative für Anwendungen von ultraskalierten CMOS-Logikbauelementen und Dünnfilmtransistoren (TFTs) als oberste Schicht in dreidimensionalen integrierten Schaltungen [1,2,3]. In den letzten Jahren wurden große Anstrengungen auf die Oberflächenpassivierung, das Gate-Dielektrikum und das Kanal-Engineering für Ge p-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistoren (MOSFETs) gerichtet, die zu einer signifikanten Verbesserung der elektrischen Leistung für die p-Kanal-Geräte.

Bei Ge-n-Kanal-MOSFETs ist jedoch eine geringe effektive Trägermobilität (μ eff ), die durch eine schlechte Grenzflächenschicht des Gatestapels verursacht wird, schränkt die Leistung der Vorrichtungen stark ein. Verschiedene Oberflächenpassivierungstechniken, einschließlich Si-Passivierung [1], Plasma-Nachoxidation [4] und InAlP-Passivierung [5] und mehrere High-κ-Dielektrika einschließlich HfO2 , ZrO2 [6,7,8], Y2 O3 [9] und La2 O3 [10] wurden in Ge-nMOSFETs untersucht, um die Elektronen μ . zu verstärken eff . Es wurde gezeigt, dass ZrO2 In den Ge-Kanal integriertes Dielektrikum kann eine robuste Schnittstelle bieten, da ein GeO2 Grenzschicht kann mit dem ZrO2 . reagieren und sich mit ihm vermischen Schicht [7]. Ein anständiges Loch μ eff wurde in Ge-p-Kanal-Transistoren beschrieben [6,7,8], während es noch viel Raum für Verbesserungen bei Elektronen μ . gibt eff für ihre Kollegen.

In dieser Arbeit werden Ge-nMOSFETs mit ZrO2 Gate-Dielektrikum werden hergestellt, um ein verbessertes μ . zu erreichen eff über Si im gesamten Bereich der Inversionsladungsdichte (Q inv ). Ge-Transistoren erzielen eine 50%ige Verbesserung des Elektronen μ eff im Vergleich zur Si-Universalmobilität bei einem mittleren Q inv von 5.0 × 10 12 cm −2 .

Experimentell

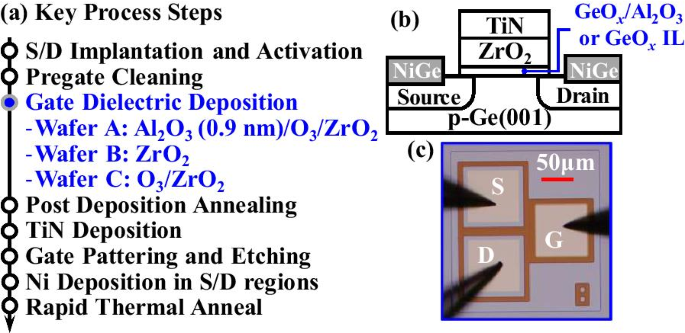

Die wichtigsten Prozessschritte zur Herstellung von Ge-nMOSFETs auf 4-Zoll-p-Ge(001)-Wafern mit einem spezifischen Widerstand von 0,136–0,182 Ω cm sind in Abb. 1a dargestellt. Die Source/Drain (S/D)-Regionen wurden mit Phosphorionen in einer Dosis von 1 × 10 15 . implantiert cm −2 und einer Energie von 30 keV, gefolgt von einem Dotierstoffaktivierungsglühen bei 600 °C. Nach der Vor-Gate-Reinigung wurden Ge-Wafer in eine Atomschicht-Abscheidungskammer geladen, um die dielektrische(n) Gate-Schicht(en) zu bilden:Al2 O3 /O3 Oxidation/ZrO2 , ZrO2 , oder O3 Oxidation/ZrO2 für Wafer A, B bzw. C. Für Wafer A 0,9 nm Al2 O3 wurde verwendet, um die Kanaloberfläche während O3 . zu schützen Oxidation. O3 Die Oxidation wurde bei 300 °C für 15 Minuten für beide Wafer A und C durchgeführt. Für alle Wafer war die Dicke von ZrO2 war ~ 3,3 nm. Anschließend wurde TiN(100 nm)-Gate-Metall über physikalisch reaktives Sputtern abgeschieden, und es wurden Lithografiemusterung und reaktives Ionenätzen verwendet, um die Gate-Elektrode auszubilden. Danach wurde eine 25 nm dicke Ni-Schicht in S/D-Gebieten abgeschieden. Schließlich wurde das Nachmetallisierungsglühen (PMA) bei 350 °C für 30 s durchgeführt, um das Ni-Germanid zu bilden und die Grenzflächenqualität zu verbessern. Schematische und Mikroskopbilder des hergestellten Transistors sind in Abb. 1b bzw. c gezeigt.

a Wichtige Prozessschritte zur Herstellung von Ge-nMOSFETs. b Querschnittsschema und c Mikroskopaufnahme der hergestellten Geräte

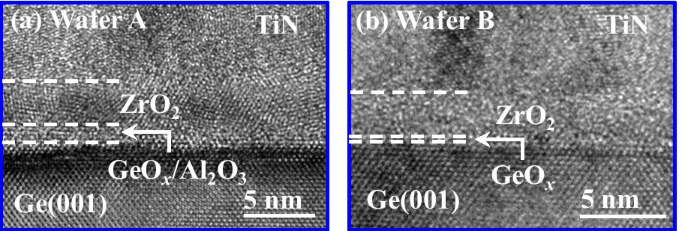

Abbildung 2a, b zeigen die hochauflösenden Transmissionselektronenmikroskop(HRTEM)-Bilder der Gatestapel auf den Wafern A bzw. B. Die einheitliche Dicke des Al2 O3 /GeOx Grenzschicht (IL) für Wafer A ist ~ 1,2 nm, was auf 0,2–0,3 nm GeOx . hinweist . Für das Gerät auf Wafer B ein ultradünnes GeOx IL wurde experimentell nachgewiesen [7].

HRTEM-Bilder von a TiN//ZrO2 /Al2 O3 /GeOx /Ge, b TiN/ ZrO2 /GeOx /Ge-Stapel für die Geräte auf den Wafern A bzw. B

Ergebnisse und Diskussion

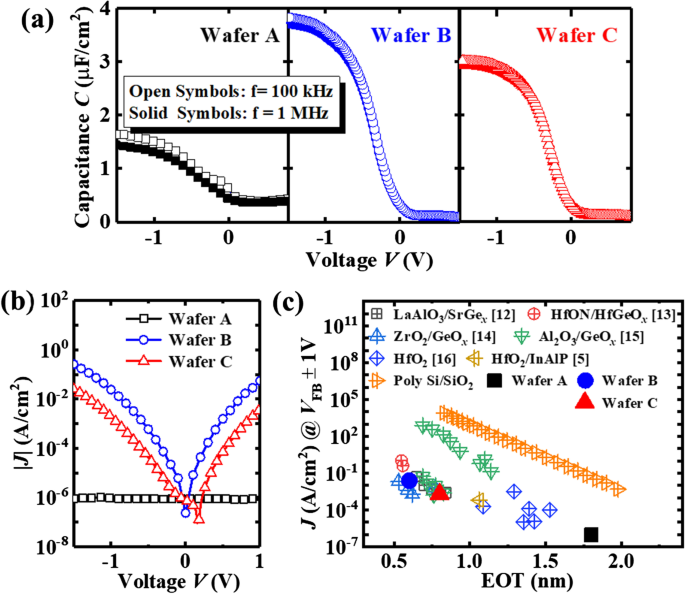

Die gemessene Kapazität (C ) und der Ableitstrom (J ) werden die Charakteristiken für Ge-MOS-Kondensatoren auf den Wafern A, B und C gemessen und in Fig. 3a bzw. b gezeigt. Die äquivalente Oxiddicke (EOT) der Bauelemente auf den Wafern A, B und C wird mit 1,79, 0,59 bzw. 0,83 nm extrahiert. Unter der Annahme des GeOx IL bietet eine zusätzliche EOT von ~ 0,25 nm für Wafer A und C durch Vergleich der Wafer B und C, dem 3,3 nm ZrO2 trägt einen EOT von ~ 0,6 nm mit einem κ-Wert von ~ 21,8 bei, was mit dem zuvor gemeldeten Wert von amorphem ZrO2 . übereinstimmt [11]. Diese abgeleiteten Ergebnisse bestätigen auch, dass die Dicke in GeOx IL auf Wafer B ist vernachlässigbar.

a Gemessenes C als Funktion der Spannung V Eigenschaften für Ge-pMOS-Kondensatoren auf den Wafern A, B und C. b J gegen V Kurven für die Geräte. c Benchmarking von J (extrahiert bei V FB ± 1 V) der Ge-MOS-Kondensatoren in dieser Arbeit im Vergleich zu Daten, die für ähnliche Vorspannungsbedingungen aus der Literatur erhalten wurden

Das GeOx /Al2 O3 IL für Wafer A und GeOx IL für Wafer C erzeugt die EOT von ~ 1,2 bzw. ~ 0,25 nm. Der EOT der Bauelemente kann weiter reduziert werden, indem die IL-Dicke verringert oder die Grenzflächenqualität verbessert und die Permittivität von ZrO2 . erhöht wird mit etwas Oberflächenpassivierung, z. B. NH3 /H2 Plasmabehandlung [6]. Abbildung 3c vergleicht J versus EOT-Eigenschaften für die Ge-nMOSFETs in dieser Arbeit mit Werten für andere berichtete Ge-Bauelemente [5, 12, 13, 14, 15, 16, 17]. Es wird auch beobachtet, dass die Ergebnisse mit dem berichteten Ge-MOS mit ultradünnem EOT übereinstimmen, das denselben Trends folgt, was darauf hindeutet, dass der in Fig. 3b gezeigte Unterschied des Leckstroms hauptsächlich auf den Unterschied des EOT zurückzuführen sein sollte.

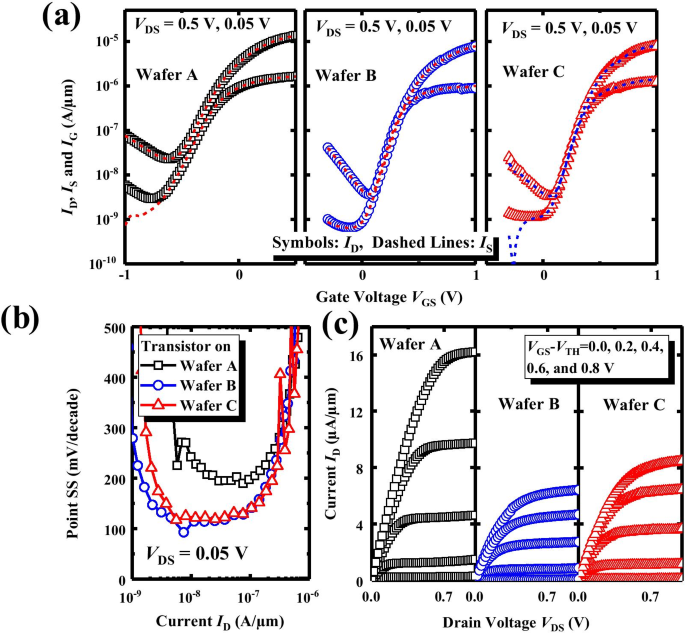

Abbildung 4a zeigt den gemessenen Drainstrom (I D ) und Quellstrom (I S ) gegen Gatespannung (V G ) Kurven von Ge nMOSFETs der Wafer A, B und C. Alle Transistoren haben eine Gatelänge L G von 4 μm und einer Gate-Breite W von 100 μm. Die Punkt-Unterschwellenschwingung (SS), definiert als dV G /d(logich D ), als Funktion von I D Kurven für die Transistoren in Fig. 4a berechnet und in Fig. 4b gezeigt. Es wird klargestellt, dass der Transistor auf Wafer A das verschlechterte I . aufweist D Leakage Floor und SS im Vergleich zu den Bauelementen auf den Wafern B und C. Abgesehen davon, dass die Erhöhung des EOT bei den Bauelementen auf Wafer A die Zunahme von SS mit sich bringen würde, sollten diese Phänomene teilweise der Tatsache zugeschrieben werden, dass das Bauelement mit dem Al 2 O3 eingefügte Schicht hat eine höhere Dichte an Grenzflächenfallen (D es ) innerhalb der Bandlücke des Ge-Kanals im Vergleich zu den Wafern B und C.

a Gemessen I D und ich S gegen V GS Kurven von Ge-nMOSFETs auf den Wafern A, B und C. b Punkt SS als Funktion von I D für die Transistoren. c Ich D –V D Eigenschaften zeigen, dass der Ge nMOSFET auf Wafer A einen höheren Treiberstrom hat als die Geräte auf den Wafern B und C

Abbildung 4c zeigt die gemessenen Ausgangseigenschaften, d. h. I D –V D Kurven für verschiedene Werte von Gate Overdrive |V G –V TH | der Geräte, die zeigen, dass der Ge-Transistor auf Wafer A im Vergleich zu den Geräten auf den Wafern B und C einen deutlich verbesserten Ansteuerstrom erreicht. Hier ist V TH ist definiert als V GS entspricht einem Ich D von 10 −7 A/μm. Unter Berücksichtigung der identischen Bedingungen für die S/D-Bildung ist das verstärkte I DS für Transistoren auf Wafer A bedeutet den höheren μ eff [18,19,20,21]. Die Al2 O3 Schicht hat nicht zum Abbau von D . geführt es Leistung nahe dem Leitungsband des Ge-Kanals.

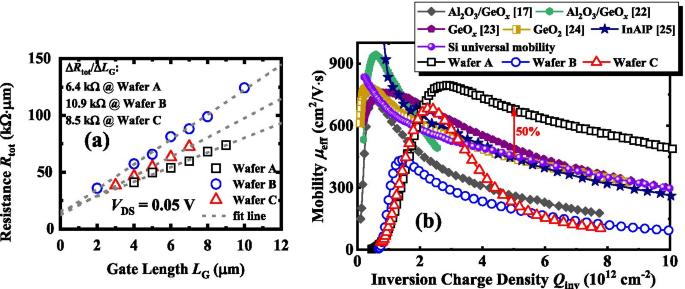

Abbildung 5a zeigt den Gesamtwiderstand R tot als Funktion von L G für die Ge nMOSFETs mit ZrO2 Dielektrikum mit einem L G im Bereich von 2 bis 10 µm. Die Werte von R tot werden bei einem Gate-Overdrive von 0,6 V und einem V . extrahiert D von 0,05 V. Der S/D-Widerstand R SD der Transistoren wird zu ~ 13,5 kΩ μm extrahiert, wobei die angepassten Linien verwendet werden, die sich am y . schneiden -Achse. Das ähnliche R SD stimmt mit dem identischen Prozess der PMA- und S/D-Bildung überein. Der Kanalwiderstand R CH Werte der Geräte werden durch die Steigung der angepassten Linien erhalten, d. h. ΔR tot /ΔL G , die zur Berechnung des μ . verwendet werden kann eff Eigenschaften von Ge-nMOSFETs. Um die Schnittstellenqualität zu bewerten, müssen Schnittstellenfallendichten (D es ) wurden nach der Hill-Methode [17] durch die folgende Gleichung extrahiert:

$$D_{{{\text{it}}}} =\frac{{2G_{{{\text{m}}\max }} /\omega }}{{qA\left[ {\left( {\ frac{{G_{{{\text{mmax}}}} }}{{\omega C_{{{\text{ox}}}} }}} \right) + \left( {1 - C_{{\ text{m}}} /C_{{{\text{ox}}}} } \right)^{2} } \right]}}$$wo q ist die elektronische Ladung, A ist die Fläche des Kondensators, G m,max ist der Maximalwert der gemessenen Leitfähigkeit mit der entsprechenden Kapazität C m , ω die Kreisfrequenz ist und C Ochse ist die Gate-Oxid-Kapazität. Das D es die berechneten Werte betragen 3,7, 3,2 und 2,3 × 10 12 eV −1 cm −2 für die Geräte auf den Wafern A, B bzw. C.

Es ist bekannt, dass die berechneten Werte dem Midgap D . entsprechen es . Das Gerät mit Al2 O3 IL auf Wafer A hat einen höheren Midgap D es verglichen mit den Vorrichtungen auf den Wafern B und C. Dies stimmt mit den Ergebnissen in den Fig. 1 und 2 überein. 3a und 4a und der höhere Midgap D es führt zu einer größeren Streuung der Verarmungskapazität in Wafer A, was einen höheren Leckstrom von I . verursacht DS im Vergleich zu den anderen beiden Wafern. Beachten Sie, dass der Wafer A das untere D haben sollte es in der Nähe der Leitungsbandlücke aufgrund ihres höheren μ eff über Wafer B und C.

a R tot gegen L G Kurven für Ge nMOSFETs auf den Wafern A, B und C. Die Anpassungslinie, die sich an der y-Achse schneidet, und die Steigung der linearen Anpassungslinien werden verwendet, um das R . zu extrahieren SD und R CH , bzw. b μ eff für die Ge-nMOSFETs in dieser Arbeit im Vergleich zu früher veröffentlichten Ergebnissen für ungespannte Ge-Transistoren. Die Geräte auf Wafer A zeigen das verbesserte μ eff als die Si-Universalmobilität im gesamten Bereich von Q inv

Es ist bekannt, dass μ eff ist der Flaschenhals für hohe Ansteuerströme und Transkonduktanz in Ge-nMOSFETs. Hier, μ eff kann berechnet werden durch \(\mu_{{{\text{eff}}}}} =1/[WQ_{{{\text{inv}}}}} (\Delta R_{{{\text{tot}}}} /\Delta L_{{\text{G}}} )]\), wobei ΔR tot /ΔL G ist die Steigung des R tot gegen L G wie in Abb. 5a gezeigt. Q inv erhält man durch Integration des gemessenen C inv –V G Kurven. In Abb. 5b vergleichen wir die μ eff gegen Q inv der Ge-nMOSFETs auf den Wafern A, B und C mit denen, die zuvor in [18, 22, 23, 24, 25] beschrieben wurden. Der extrahierte Peak μ eff Werte der Transistoren auf den Wafern A und C sind 795 und 682 cm 2 /V s bzw. der von Ge-nMOSFETs auf Wafer B beträgt 433 cm 2 /V s. Gen nMOSFETs mit Al2 O3 IL erreichen ein deutlich verbessertes μ eff im Vergleich zu den Transistoren auf Wafer B oder C, die Bauelemente in [18, 22,23,24,25] in einem hohen Feld und universelle Si-Mobilität im gesamten Q inv Palette. Bei einem Q inv von 5 × 10 12 cm −2 , 50 % μ eff eine Verbesserung wird in Vorrichtungen auf Wafer A im Vergleich zur universellen Si-Mobilität erreicht. Dies zeigt, dass durch den Schutz der Kanaloberfläche zur Verhinderung der Vermischung von ZrO2 und GeOx mit Al2 O3 , wird eine hochwertige Schnittstelle zwischen Gate-Isolator und Ge realisiert, um die Mobilitätseigenschaften zu verbessern, was auch in früheren Studien zu Ge-MOSFETs mit ultradünnem EOT berichtet wurde [26]. μ eff in Transistoren auf Wafer C ist höher als das Si-Universal bei einem Q inv von 2,5 × 10 12 cm −2 , obwohl es mit der Zunahme von Q . schnell abfällt inv Palette. Dies zeigt an, dass das verwendete O3 Oxidation vor ZrO2 die Abscheidung würde die Grenzflächenqualität bis zu einem gewissen Grad verbessern; es führt jedoch nicht zu einer ausreichend flachen Kanaloberfläche, um die Streuung der Oberflächenrauheit des Trägers bei hohem Q . effektiv zu unterdrücken inv aufgrund der Durchmischung von ZrO2 und GeOx , da berichtet wird, dass die Erzeugung von Sauerstoffleerstellen während der Vermischung die Rauhigkeit der Nahordnung (SRO) erhöhen würde [27]. Optimierung des O3 Oxidationsprozess oder Reduktion des Al2 O3 Die IL-Dicke kann dazu führen, dass der Ge-Transistor eine reduzierte EOT erreicht, während ein höherer μ . aufrechterhalten wird eff auf dem hohen Q inv .

Schlussfolgerungen

Die Auswirkungen der dielektrischen Struktur und Morphologie des Gates auf die elektrischen Eigenschaften von Ge-nMOSFETs werden untersucht. Ein Al2 O3 /ZrO2 Gate-Dielektrikum sorgt für deutlich verbessertes μ eff im Vergleich zur Si-Universalmobilität. μ eff kann durch Einfügen eines Al2 . verbessert werden O3 Schicht zwischen dem ZrO2 und Ge-Kanal, was jedoch unweigerlich zu einem größeren EOT führt. Al2 O3 -freie Gen nMOSFETs mit O3 Oxidation der Ge-Oberfläche vor ZrO2 Abscheidung einen Spitzenwert von μ . erreichen eff von 682 cm 2 /V s, das höher ist als das von Si bei ähnlichem Q inv .

Verfügbarkeit von Daten und Materialien

Die Datensätze, die die Schlussfolgerungen dieses Artikels unterstützen, sind im Artikel enthalten.

Abkürzungen

- Ge:

-

Germanium

- ZrO2 :

-

Zirkoniumdioxid

- Al2 O3 :

-

Aluminiumoxid

- O3 :

-

Ozon

- Si:

-

Silizium

- PMA:

-

Nachglühen des Metalls

- PDA:

-

Glühen nach der Abscheidung

- IL:

-

Grenzschicht

- TiN:

-

Titannitrid

- MOSFETs:

-

Metall-Oxid-Halbleiter-Feldeffekttransistoren

- ALD:

-

Atomlagenabscheidung

- HF:

-

Flusssäure

- µ eff :

-

Effektive Trägermobilität

- PPO:

-

Plasma-Nachoxidation

- SS:

-

Schwung unter der Schwelle

- MEZ:

-

Kapazitätsäquivalente Dicke

- EOT:

-

Äquivalente Oxiddicke

- Qinv:

-

Inversionsladungsdichte

- HRTEM:

-

Hochauflösendes Transmissionselektronenmikroskop

- Ni:

-

Nickel

- GeOx :

-

Germaniumoxid

- I DS :

-

Strom entziehen

- V GS :

-

Gate-Spannung

- V TH :

-

Schwellenspannung

Nanomaterialien

- Erzielen von Nachhaltigkeit mit Farbstoffen und Pigmenten

- KUHMUTE gestaltet Mobilität mit SLS-3D-Druck neu

- Vollständige Terahertz-Polarisationskontrolle mit erweiterter Bandbreite über dielektrische Metaoberflächen

- Compliance-freier ZrO2/ZrO2 − x /ZrO2 Resistiver Speicher mit steuerbarem Grenzflächen-Mehrzustands-Schaltverhalten

- Leitungsmechanismus und verbesserte Ausdauer bei HfO2-basiertem RRAM mit Nitridierungsbehandlung

- Dielektrische Verstärkung von atomschichtbeschichteten Al2O3/ZrO2/Al2O3-MIM-Kondensatoren durch Mikrowellenglühen

- Ge-pMOSFETs hoher Mobilität mit amorpher Si-Passivierung:Einfluss der Oberflächenorientierung

- 6 Möglichkeiten, wie wir Protocase Designer mit Version 4.6 verbessert haben

- Erzielen eines phänomenalen Finishs durch Metallisierung

- Verbesserte Verschleißfestigkeit mit Kupfer-Wolfram-Elektroden