Sollten nicht funktionierende Pads entfernt oder in Durchkontaktierungen von Hochgeschwindigkeits-Leiterplatten belassen werden?

Hochgeschwindigkeitssignale sind ein heißes Thema, das von der Kommunikationsbranche nicht vermieden werden kann. Mit der zunehmenden Menge an übertragener Information und der Übertragungsgeschwindigkeitsrate wurden Hochgeschwindigkeitssignale allmählich bedeutsam. Hochgeschwindigkeits-PCB ist eine Ladeplatine für Hochgeschwindigkeitssignale, und ihre Materialauswahl, Fertigungstechnologie und Routing-Design wirken sich alle auf die Qualität von Hochgeschwindigkeitssignalen aus. Non-Functional Pad, auch bekannt als NFP, ist eine technologische Methode zur Herstellung von Hochgeschwindigkeits-Leiterplatten, während die Einfügungsdämpfung einer der wichtigsten Parameter für die Signalqualität ist. NFP zu entfernen oder beizubehalten, war ein unvermeidliches Diskussionsthema zwischen Ingenieuren und Herstellern. Dieser Artikel analysiert den Einfluss von NFP auf die Einfügungsdämpfung von Hochgeschwindigkeitssignalen aus der Perspektive des Herstellungsverfahrens in einer experimentellen Methode und führt Sie zu der Antwort, ob Sie unbenutzte Pads entfernen oder behalten sollten.

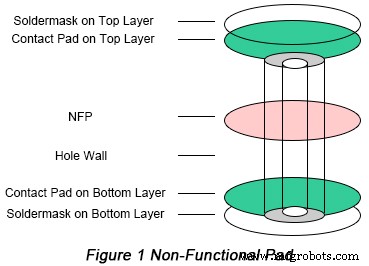

Einführung von NFP

Nicht funktionale Pads sind Pads auf internen oder externen Schichten, die nicht mit irgendwelchen aktiven leitfähigen Mustern auf der Schicht verbunden sind. NFP hat keinen Einfluss auf die elektrische Signalübertragung, kann aber die Kupferhaftung an der Lochwand verstärken. NFP kann in Abbildung 1 unten angezeigt werden.

Das Hinzufügen von NFP bedeutet, dass vor dem PTH-Kupfer (Plated Through Hole) Metallbefestigungspunkte bereitgestellt werden. Daher neigen viele Hersteller dazu, NFP hinzuzufügen, um eine bessere Wirkung des PTH-Kupfers im Prozess der mehrschichtigen Leiterplattenherstellung sicherzustellen .

Experimentdesign

In diesem Experiment wird das gleiche CCL-Material (Copper Clad Laminate) ausgewählt. Alle Leiterplatten enthalten 20 Schichten, zwischen denen das Routing auf der dritten und achtzehnten Schicht implementiert ist. Der Einfügungsverlust kann zwischen dem Hinzufügen von NFP (Schema 1) und dem Entfernen von NFP (Schema 2) verglichen werden, um sicherzustellen, ob NFP einen Einfluss auf die Signalqualität hat. Da im Prozess der Leiterplattenherstellung viele unsichere Elemente vorhanden sind, müssen die Schlüsselparameter abgesehen von der Einfügungsdämpfung überprüft werden, um sicherzustellen, dass keine anderen Einflussfaktoren in die Herstellung eingemischt werden.

Inspektion der beeinflussenden Elemente

• Prüfung der Impedanzkonsistenz

Beim Signalverlusttest wird aufgrund der inkonsistenten Impedanz tendenziell eine Signalreflexion erzeugt, die schließlich das Testergebnis des Einfügungsverlusts beeinflusst. Folglich hängt die Korrektheit des Einfügungsdämpfungstests direkt von der Qualität der Impedanzkonsistenz ab. Der charakteristische Impedanztest wird jeweils gemäß Schema 1 und Schema 2 durchgeführt und der erhaltene charakteristische Impedanzwert ist in der folgenden Tabelle zusammengefasst.

| Testschema | Testebene | Charakteristische Impedanz (Ohm) |

| Schema1 | 3. Ebene | 113.03 |

| Schema2 | 3. Ebene | 112.71 |

| Schema1 | 18. Ebene | 111,93 |

| Schema2 | 18. Ebene | 114.07 |

Basierend auf der obigen Tabelle ist ersichtlich, dass die Impedanzdifferenz zwischen zwei Schemata innerhalb von 5 % liegt, mit der Schlussfolgerung, dass der Einfluss der charakteristischen Impedanz auf den Verlusttest vernachlässigt werden kann.

• Elemente, die die Prüfung der Einfügungsdämpfung beeinflussen

Die Einfügungsdämpfung setzt sich aus dielektrischen Verlusten und Leiterverlusten zusammen. Da in zwei Schemata, die in diesem Experiment untersucht wurden, das gleiche Material und die gleichen Lightpainting-Grafiken verwendet werden, resultieren dielektrische Verluste und Leiterverluste nur aus der Leiterplattenherstellung. Als nächstes werden beide Punkte jeweils analysiert, um sicherzustellen, dass die Leiterplattenherstellung nicht beeinflusst wird.

a. Prüfung des dielektrischen Verlusts

Die Anwendung einer Klebefolie in mehrschichtigem Stapeln erzeugt eine gewisse Harzrezession, und eine unterschiedliche Menge an Harzrezession führt zu Unterschieden zwischen den dielektrischen Verlusten. Hinsichtlich der Ungewissheit der Harzrezession auf der Klebefolie muss nach dem Stapeln eine X-Querschnitt-Analyse durchgeführt werden, um den Einfluss aufgrund des Unterschieds in Bezug auf die Harzrezessionsmenge vollständig zu eliminieren.

Durch die Analyse kann zusammengefasst werden, dass die Kerndicke der oberen Schicht und der unteren Schicht der beiden Schemata 139,8 μm bzw. 135,2 μm beträgt. Nach dem Stapeln beträgt die Dicke der Klebefolie jeweils 257,4 μm und 251,9 μm. Der maximale Dickenunterschied liegt innerhalb von 6 μm, wodurch die Anforderungen an die Herstellungstoleranz erfüllt werden und die Einfügungsdämpfung nicht durch den dielektrischen Verlust beeinflusst wird.

b. Leiterverlustprüfung

Der Leiterverlust hängt also mit der Länge und Breite der Leitungen, der Oberflächenrauheit und der seitlichen Erosion während des Leiterplattenherstellungsprozesses in der Testschaltung zusammen. In den beiden Schemata dieses Experiments ist das Schaltungsdesign das gleiche, wobei der Einfluss der Leitungslänge eliminiert ist. Der Brauneffekt, die Konzentration der Ätzlösung und der Wasserdruck haben alle Einfluss auf die Oberflächenrauheit. Um diese komplizierten Elemente zu vermeiden, wird die Schaltungskonsistenz direkt anhand des Endergebnisses beurteilt.

Durch das Experiment wird die Übertragungsleitungsbreite mit 168 μm bzw. 166 μm bei der Anwendung von Schema 1 und Schema 2 und die Übertragungsleitungshöhe mit 18,3 μm und 18,9 μm gemessen. Die Oberflächenrauhigkeit bleibt bei 2,5 μm. Alle Daten weisen darauf hin, dass die Leiterverluste im Hinblick auf die Herstellung von Übertragungsleitungen grundsätzlich ähnlich sind, sodass der Einfluss der Leiterverluste auf die Einfügungsdämpfung eliminiert werden kann.

NFP-Einflussanalyse

Ausgehend von der Erzeugungsquelle des dielektrischen Verlusts und des Leiterverlusts, gekoppelt mit dem Erzeugungsprinzip der Einfügungsdämpfung, wird eine Reihe von Inspektionen in Bezug auf die Konsistenz der Leiterplattenherstellung implementiert, um sicherzustellen, dass nur eine Variable, nämlich NFP, in den beiden Schemata auftritt. Gemäß der FD-Methode (Frequency Domain) in IPC-TM650-2.5.5.12 werden Schema 1 und Schema 2 getestet, wobei das Ergebnis in Abbildung 2 unten angezeigt wird.

Als Ergebnis der einzigen Variablen, NFP, kann der Einfluss von NFP auf die Signaleinfügungsdämpfung ungefähr beurteilt werden. Schema 1 entfernt NFP, während Schema 2 NFP behält. Aus der obigen Abbildung ist ersichtlich, dass das Ergebnis des Einfügungsdämpfungstests für Schicht 03 oder Schicht 18 in Schema 1 insgesamt kleiner ist als in Schema 2, was darauf hinweist, dass das Hinzufügen von NFP die Einfügungsdämpfung des Signals verstärkt.

Basierend auf diesem Experiment bleibt die Einfügungsdämpfungsdifferenz zwischen zwei Schemata bei etwa 9%. Abbildung 3 ist eine primäre Einstufung auf einem bekannten Kommunikationsterminalmaterial.

Auf der Grundlage von Abbildung 3 ist ersichtlich, dass zwischen allen Materialklassen nur sehr geringe Unterschiede in der Einfügungsdämpfung auftreten. Wenn die in diesem Experiment untersuchte Einfügungsdämpfung nur in die Schwellenwertkategorie fällt, wird die Materialqualität durch NFP verringert, was die gesamte Produktionslinie vom Materialhersteller bis zum Ende stark beeinflussen wird.

Schlussfolgerung

Wenn es um Hochgeschwindigkeits-Leiterplatten geht, sind Multilayer-Leiterplatten unvermeidlich der Entwicklungstrend und die Durchkontaktierung ist das erste Problem. NFP bietet eine große Verbesserung gegenüber PTH-Kupfer im Prozess der Herstellung von PCB-Durchgangswänden und spielt eine wirksame Rolle bei der Verhinderung des Abfalls von Via-Kupfer und bei der Bewältigung von Qualitätsproblemen wie Rissen in der Durchkontaktierung. Unter Eliminierung anderer Einflussfaktoren wird in diesem Artikel die Variable NFP betrachtet und der Einfluss von NFP auf die Einfügungsdämpfung analysiert, um Materialherstellern, Leiterplattenherstellern und Anschlussherstellern in Bezug auf das Hochgeschwindigkeits-Leiterplattendesign einen Hinweis zu geben.

Hilfreiche Ressourcen

• Einführung in die Via-in-Pad-Technologie (VIP)

• High-Speed-Layout-Tipps

• High-Speed-PCB-Routing-Techniken zur Verringerung des Einflusses von EMI

• Forschung zu High -Schnelles PCB-Design in einem eingebetteten Anwendungssystem

• PCB-Fertigungsservice mit vollem Funktionsumfang von PCBCart – Mehrere Mehrwertoptionen

• Erweiterter PCB-Montageservice von PCBCart – ab 1 Stück

Industrietechnik

- Wie sollte eine Pandemieversicherung aussehen?

- Vias auf BGA-Pads

- Was ist PCB via Tenting?

- Warum sollte Papier aus Werkstätten entfernt werden?

- Kurze Antworten auf große Fragen zum PCB-Design

- Auswirkung von schlecht ausgeführten, mit Lötmasken verschlossenen Vias auf Via-Kupfer von PCB und Lösungen

- 3 Routing-Techniken beim PCB-Design von Hochgeschwindigkeits-Signalschaltungen

- Hochgeschwindigkeits-Layout-Tipps

- Methoden zur Stärkung der Entstörungsfähigkeit im PCB-Design

- Unterdrückungsmethode der Signalreflexion im Hochgeschwindigkeits-PCB-Layout