Neuere Veröffentlichungen beschreiben die Skalierbarkeit von Kohlenstoffnanoröhren und Durchbrüche bei der Integration

Carbon Nanotubes (CNT) sind für die Halbleiterindustrie attraktiv, da sie im Vergleich zu Silizium mit einer Körperdicke von nur 1 Nanometer überlegene elektrische Leiter sind. Warum haben wir also noch nicht überall CNT-Chips, von Mainframes bis hin zu Mobilgeräten? Die Skalierbarkeit des Transistors und die großflächige Integration sind immer noch große Herausforderungen. Aber zwei Artikel, die meine Kollegen und ich kürzlich in Wissenschaft veröffentlicht haben und Naturnanotechnologie zeigen vielversprechende Durchbrüche in diesen beiden Bereichen, die für die Realität von CNT-Chips entscheidend sind.

Fußabdruck-Errungenschaften weisen auf die Nanoskala hin

Erstens:Skalierung. Wir wissen, dass 3D-FinFET-Siliziumchips bei 7 Nanometern an ihre Leistungs- und Leistungsgrenze stoßen könnten. Und während die jüngste Ankündigung von 5-nm-Silizium-Nanoblatt-Transistoren Skalierbarkeit, Leistung und Leistung am nächsten Knoten steigert, kennen wir auch ihre Grenzen.

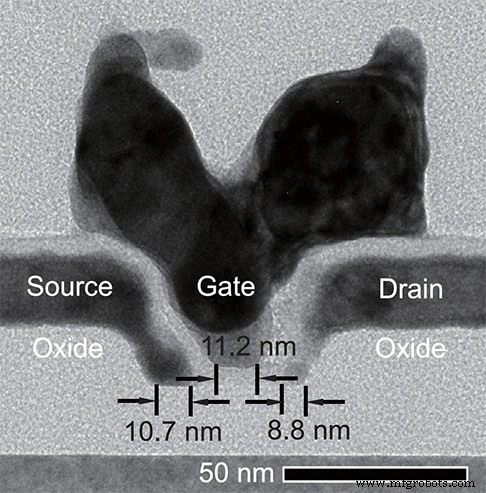

Ein Transistor ist mehr als sein Tor. Die Quelle, der Abfluss und die Abstandshalter ergeben zusammen eine Gesamtfläche. Im Bild:ein CNT-Transistor mit einem 40-nm-Footprint. (Abbildung 1B in „Carbon Nanotube Transistors scaled to a 40-nanometer Footprint“, veröffentlicht in Science.)

In unserer Wissenschaft Paper „Carbon Nanotube Transistors scaled to a 40-nm Footprint“, wir haben einen ganzen CNT-Transistor auf das Ziel der International Technology Roadmap for Semiconductors (ITRS) skaliert, dass Transistoren einen 40-nm-Footprint erreichen – ein Ziel, das sie sich gesetzt und seit 2015 nicht geändert haben Als Referenz nehmen die modernen 14-nm-Transistoren der Spitzenklasse tatsächlich etwa 90 nm Chipfläche ein.

Wir können einen CNT-Transistor potenziell weiter skalieren als Silizium aus dem Hauptgrund, dass er intrinsisch nur 1,2 nm dick ist. Diese Dünnheit hat den Dominoeffekt, die Gatelänge auf 10 nm zu reduzieren, da er eine bessere elektrostatische Kontrolle des Gates bietet und dazu beiträgt, Leckströme zu minimieren. Außerdem bewegen sich Elektronen in CNTs schneller als Silizium, was die Geräteleistung verbessert.

Aber wir brauchten einen neuen Weg, um CNTs mit ihrer Source und ihrem Drain zu verbinden (im Bild). Wir mussten den perfekten Materialmix finden, der diese 10-nm-Elemente bei einer herstellbaren Temperatur zusammen „backen“ konnte. Unsere früheren funktionierenden endgebondeten Kontakte zwischen Source-und-CNT und Drain-und-CNT erforderten so hohe Verarbeitungstemperaturen von etwa 850°C, dass der Kanal nicht kürzer als 60–100 nm sein konnte. Der Wechsel zu einer Kobalt-Molybdän-Legierung für die Verdrahtung zwischen den Elementen senkte die Temperatur effektiv auf akzeptable 650 °C – und verringerte die Abstände auf 10 nm.

Dr. Qing Cao, der Hauptautor des Papiers, und andere Kollegen im Team zeigten, dass der CNT-Transistor – bei dieser neu erreichten Grundfläche – eine Leistung erreichen kann, die mit den heutigen Transistorstandards vergleichbar ist.

CNT-Elemente kommen auf dem Ringoszillator zusammen

Die Demonstration eines derart extrem skalierten Einzeltransistors, selbst mit einem weniger herstellbaren Prozessablauf, gab uns die Motivation, die Integrationsherausforderungen für praktische CNT-Technologien zu lösen. Und seit fünf Jahren entwickelt mein Team einzelne Elemente der CNT-Technologie. Wir wissen, wie man halbleitende CNTs trennt, CNTs auf einem Wafer „selbstzusammenbaut“ und zuverlässige n-Kanal-CNT-Feldeffekttransistoren oder „FETs“ (die normalerweise aufgrund von Kontaktmetalloxidation schnell abgebaut werden) mit verschiedenen Techniken herstellt.

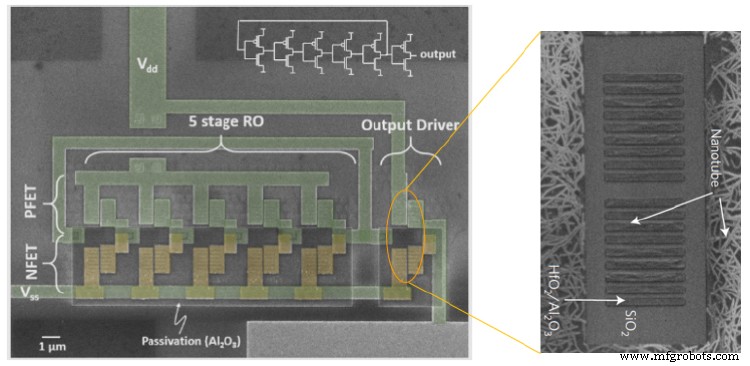

Alle Elemente müssen gleichzeitig in einem funktionsfähigen Ringoszillator arbeiten . Im Bild:Rasterelektronenmikroskopie-Draufsicht eines 5-stufigen CNT-Ringoszillators und in CNTs platzierten Gräben. (Abbildung 1B in „High-speed Logic Integrated Circuits with Solution Processing Self-Assembly Carbon Nanotubes“, veröffentlicht in Nature Nanotechnology.)

Die Herausforderung bei der Entwicklung einer disruptiven Technologie im Frühstadium besteht darin, dass einige Techniken, die zur Lösung eines Problems verwendet werden, dazu führen können, dass andere Elemente des Geräts und der Schaltung zerstört werden. Dies ist der wesentliche Grund dafür, dass alle nanotechnologisch basierten Demonstrationen, wie auch die mit CNTs, auf ein sehr niedriges Integrationsniveau beschränkt waren. Und es lässt Zweifel an ihrer praktischen Verwendung aufkommen.

Aber wir haben bei der Lösung dieser Integrationsherausforderung in unserer Nature Nanotechnology einen großen Schritt nach vorne gemacht Paper, „High-speed Logic Integrated Circuits with Solution Processing Self-assembled Carbon Nanotubes“, in dem wir zeigen, wie alle Teile zusammengefügt werden, um eine Standard-Benchmark-Schaltung in jeder Logiktechnologie zu erstellen – einen CMOS-Ringoszillator.

Dr. Jianshi Tang und meine anderen Teammitglieder kombinierten unsere zuvor entwickelten Methoden zur Reinigung und Platzierung von CNTs (einzeln sehen sie aus wie in Lösung schwimmende Penne-Nudeln), nahmen jedoch eine wichtige Anpassung vor, indem sie ein Seitenwandoxid zum Schutz des n-FET-Kanals hinzufügten vor Verschlechterung während des Herstellungsprozesses (die Seitenwand führte zu einer dreimal höheren Ausbeute, wodurch weiterhin sichergestellt wird, dass die Anforderungen aller Elemente an den Ringoszillator gleichzeitig arbeiten).

Die funktionalen 5-stufigen CMOS-Ringoszillatoren, die in dem Papier beschrieben (und oben abgebildet) sind, können bereits bei 1 V (einem Industriestandard) arbeiten. Trotz niedriger CNT-Dichte im Kanal (Sie können die sechs CNTs im gleichen Bild sehen) und entspannter Parameter erreicht die Schaltfrequenz der Bühne 2,8 GHz (355 Pikosekunden) – das erste Beispiel für das Durchbrechen der GHz-Barriere für alle nanotechbasierten Demonstrationen. Es wird prognostiziert, dass wir mit einer Dichte von mehr als 100 CNTs pro Mikrometer und richtig skalierten Geräteabmessungen eine Verzögerung im Sub-Pikosekundenbereich erreichen können, deutlich schneller als die heutigen Siliziumchips.

Wie wir in der Zeitung schreiben:

Da CMOS-Ringoszillatoren direkt die Reife der Technologie widerspiegeln, ist es der lang erwartete Beweis dafür, dass die wichtigen Probleme bei der Überführung dieses vielversprechenden Materials in eine echte Technologie energisch gelöst werden.

Speichern

Nanomaterialien

- Kohlenstoffpapier

- Carbon M2

- Kohlenstoff-Nanoröhren erweitern die Grenzen der flexiblen Elektronik

- Herstellung und Bildgebung von Cyclocarbon

- Ozeankohlenstoff auf atomarer Skala

- Carbon-Nanotube-Garn, Muskel- und transparente Folien

- Bor-Kohlenstoff-Oxynitrid als neuer metallfreier Photokatalysator

- Hocheffiziente, erregungsunabhängige blaue Lumineszenz-Karbonpunkte

- Heizungsunterstützte Dielektrophorese für ausgerichtete einwandige Kohlenstoff-Nanoröhren-Filme mit ultrahoher Dichte

- Erhöhte Biokompatibilität in anodischen TaO x Nanotube-Arrays