IBM bei SPIE:Sieben Fortschritte für mehr als 7-nm-Chips

Als wir 2015 mit unseren GLOBALFOUNDRIES- und Samsung-Partnern die ersten funktionsfähigen 7-Nanometer-Knoten-(7-nm-)Testchips der Branche ankündigten, wussten wir, dass der Prozess zur „Fertigungsreife“ der Chips – vielleicht schon im nächsten Jahr – schnell gehen würde. Während sich diese Bemühungen in der Halbleiterindustrie beschleunigen, erweitert IBM weiterhin die Grenzen, indem es sich auf die Herausforderungen der nächsten Knoten jenseits von 7 nm konzentriert.

Unser IBM-Team präsentiert diese Woche sieben Vorträge auf der Advanced Lithography Conference der International Society for Optics and Photonics (SPIE) 2017 konzentriert sich auf die Erforschung und Ermöglichung von Technologien jenseits des 7-nm-Knotens. Und es beginnt mit der Extreme Ultraviolet (EUV) Lithographie.

Unser IBM-Team präsentiert diese Woche sieben Vorträge auf der Advanced Lithography Conference der International Society for Optics and Photonics (SPIE) 2017 konzentriert sich auf die Erforschung und Ermöglichung von Technologien jenseits des 7-nm-Knotens. Und es beginnt mit der Extreme Ultraviolet (EUV) Lithographie.

Mit 7-nm-Chips erstellen wir jetzt Designs, die sich auf die Größe eines Transistors oder sogar die Verdrahtung zwischen Transistoren beziehen, die wirklich auf atomarer Ebene liegen. Um diese Art der Skalierung ohne allzu komplexe Musterschemata zu erreichen, ist EUV der Schlüssel. In einer einzigen Belichtung kann EUV ein hochauflösendes Muster erzeugen, das mit früheren Halbleitermusterungsprozessen nicht erreichbar ist. Um EUV-Muster zu ermöglichen, sind jedoch spezielle Geräte, Prozesse und Know-how erforderlich, die alle in den IBM Forschungslabors in Albany, NY und Yorktown Heights, NY, zu finden sind. Diese sieben bei SPIE vorgestellten Fortschritte in Bezug auf EUV-Masken (Vorlagen zum Drucken von Schaltungsdesigns auf einen Siliziumwafer) und Mustermaterialien (lichtaktivierte „Resists“ oder ätzbeständige Materialien) können alle als entscheidend für die Ermöglichung der 7-nm-Technologie angesehen werden und darüber hinaus:

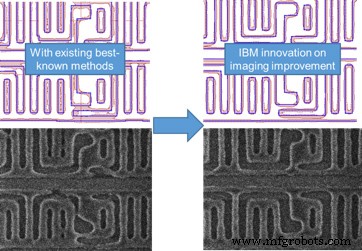

In Design-Intent-Optimierung am über 7-nm-Knoten:Die Schnittmenge der stochastischen Mitigationstechniken von DTCO und EUVL , zeigt Michael Crouse, dass, obwohl der Titel seines Vortrags groß ist, kleine Änderungen im Verdrahtungsdesign die Druckbedingungen drastisch verbessern können. In Abbildung 1 zeigt er, dass bei korrekter Optimierung der Maskenformen durchgehende Linien ohne Unterbrechung in den kleinsten Abmessungen gedruckt werden können, die für den 7-nm-Knoten und darüber hinaus erforderlich sind.

Abbildung 1 :Verbesserung der Kontrastoptimierung bei zweidimensionalen Metallverdrahtungen, demonstriert mit EUV-Lithographie. Mit der rechts dargestellten Art der Verbesserung können 20-30{ccf696850f4de51e8cea028aa388d2d2d2eef894571ad33a4aa3b26b43009887} kleinere Merkmale als die des 7-nm-Knotens robuster gedruckt und die physikalische/elektrische Variabilität drastisch reduziert werden.

In der Untersuchung alternativer Maskenstapel in der EUV-Lithographie Martin Burkhardt simuliert die Leistungsfähigkeit neuer Materialien, die derzeit nicht für EUV-Masken verwendet werden. Durch die Betrachtung des gesamten Periodensystems kann er veranschaulichen, dass EUV-Masken, die noch bessere Kontraste bieten, zum Greifen nah sind. Die tatsächliche Herstellung von Masken mit einigen dieser Materialien würde ohne weitere Änderung der EUV-Technologie Muster mit höherer Genauigkeit auf einem Siliziumwafer ermöglichen und es der Industrie somit ermöglichen, problemlos über 7 nm hinaus zu skalieren.

In Umfassende Analyse der Linienkanten- und Linienbreitenrauhigkeit für die EUV-Lithographie , zeigt Ravi Bonam, wie kleine Unvollkommenheiten und Wackeln in einer Verdrahtungsleitung klar charakterisiert werden können und zeigt dabei, welche Bedingungen die geradesten Merkmale erzeugen, die für die Verbesserung der Herstellbarkeit des EUV-Strukturierungsprozesses sowie der Leistung und Ausbeute des Chips entscheidend sind.

In Grundlagen der Wechselwirkungen zwischen EUV-Resisten und anorganischen Hartmasken , versucht Dario Goldfarb, den Filmstapel des Strukturierungsmaterials (den Punkt der Übertragung vom Muster auf den Wafer) zu verbessern, indem er die physikalischen und chemischen Wechselwirkungen an den Grenzflächen zwischen diesen Filmen verbessert, die oft nicht gerne aneinander haften. Er nutzt dieses Verständnis, um spezifische chemische Wechselwirkungen zu erzeugen, die diese Materialien zusammenhalten (siehe Abbildung 2), was entscheidend ist, um sicherzustellen, dass diese winzigen, EUV-gemusterten Formen lange genug an Ort und Stelle bleiben, um ihre Muster auf das darunter liegende Substrat zu übertragen.

Abbildung 2 :Ein EUV-Resist, der zuvor auf einer anorganischen Silizium-Hartmaske nicht strukturiert werden konnte, kann jetzt nach einer auf die Resist/Hartmasken-Kombination zugeschnittenen Oberflächenanpassung klar strukturiert werden.

In einem ähnlichen Thema wie Dario Goldfarbs Vortrag demonstriert Indira Seshadri in Ultrathin EUV Patterning Stack mit Polymerbürste als Haftvermittlerschicht , dass durch die Verwendung eines polymerähnlichen Materials, das eine Brücke zwischen winzigen EUV-gemusterten Strukturen und dem darunter liegenden Substrat bildet, diese sehr hochauflösenden Muster in das darunter liegende Substrat geätzt werden können und die beabsichtigte Designform beibehalten, was der Schlüssel zu nachgiebigen Chips bei dieser Länge ist Waage.

Bei so vielen neuen Dünnschichtlösungen im Spiel ist die Fähigkeit, fertigungswürdige Prozesse frühzeitig in der Forschungsphase zu erkennen und zu verbessern, von entscheidender Bedeutung. In einem Vortrag mit dem Titel Driving Down Defect density in Composite EUV Patterning Film Stacks , demonstriert Luciana Meli systematische Fallstudien unter Verwendung einer Mischung aus verfügbaren Fehlerinspektionstechniken, um die Prozess- und Materialverbesserungen aufzuzeigen, die erforderlich sind, um die für 7 nm und über die EUV-Herstellbarkeit hinaus erforderliche geringe Fehlerhaftigkeit zu erreichen.

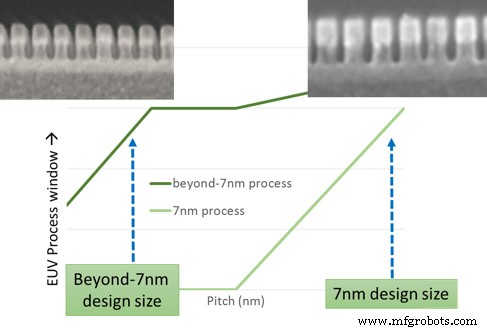

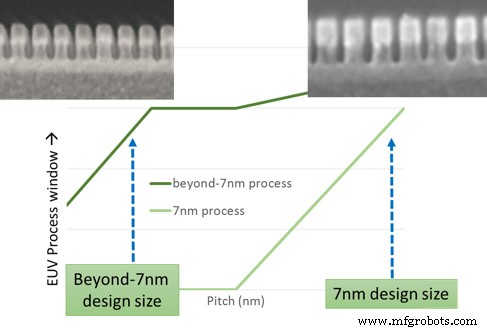

Anuja De Silva bringt viele dieser Konzepte der Bildgebung und Materialverbesserungen zusammen und hält einen Vortrag mit dem Titel Single-Expose Patterning Development for EUV Lithography , zeigt die erfolgreiche Strukturierung von Verdrahtungsschaltungen bei den Abmessungen von 30 nm und darunter, die über den 7-nm-Knoten hinaus erforderlich sind. Die Fähigkeit, dies zu erreichen, stellt einen großen Sprung gegenüber den Fähigkeiten dar, die erstmals für den 7-nm-Knoten verfügbar waren (siehe Abbildung 3) und kann den 7-nm-Knoten selbst verbessern, obwohl sie die noch verbleibenden Herausforderungen hervorhebt, um voll funktionsfähige, nachgiebige Chips bei . zu ermöglichen Abmessungen erforderlich für Technologie über 7nm.

Ein 7-nm-Chip hat 20 Milliarden Transistoren in einem etwa fingernagelgroßen Raum. Sie werden ihren Weg in Systeme und Geräte finden und die Fähigkeiten – und das Mooresche Gesetz – erweitern, um immer anspruchsvollere Aufgaben in den Bereichen Datenanalyse, Cognitive Computing und alles, was die nächste Generation mobiler Apps bereithält, zu erfüllen. Die in diesem Jahr auf der SPIE präsentierte Arbeit bringt die Branche näher an Musterlösungen heran, die nicht nur den 7-nm-Prozess mit Single-Expose-EUV robuster machen, sondern auch eine weitere Skalierung ermöglichen, um für die kommenden Jahre noch mehr Leistungs-/Leistungsvorteile zu erzielen.

Abbildung 3 :Innovationen in mehreren Aspekten des Musterungsprozesses ermöglichen es IBM, einen ganzheitlichen Musterungsprozess bereitzustellen, der die erforderlichen Funktionsgrößen über den 7-nm-Knoten hinaus bereitstellt.

Andere IBM-Präsentationen beim SPIE 2017

Design-Intent-Optimierung am über 7-nm-Knoten:Der Schnittpunkt der stochastischen Minderungstechniken von DTCO und EUVL , Michael Crouse, Nicole Saulnier, Derren Dunn

Untersuchung alternativer Maskenstapel in der EUV-Lithographie , Martin Burkhardt

Zerlegung des TCC mit nicht-kohärenten Kerneln zur schnelleren Berechnung lithographischer Bilder, Alan Rosenbluth

Entwicklung von Ti-haltigen Hartmasken durch PEALD-Abscheidung, Anuja De Silva

DSA-Musterungsoptionen für Logik- und Speicheranwendungen, Charlie Liu

Elektrische Studie des DSA-Schrumpfprozesses und des CD-Rektifikationseffekts bei unter 60 nm mit einem EUV-Testfahrzeug, Cheng-Chi

Nach dem wahren Overlay in erweiterten Knoten greifen Chiew-Seng Koay

Decklackfreie Strategien zur Orientierungskontrolle von vollorganischen High-χBlockcopolymeren, Dan Sanders

Identifizierung und Zuverlässigkeits-Sensitivitätsanalyse eines korrelierten Grundregelsystems (Entwurfsbogen), Eric Eastman

Erweiterte schnelle 3D-DSA-Modellentwicklung und -Kalibrierung für die Co-Optimierung der Designtechnologie Kafai Lai

Unerwartete Auswirkungen von RIE-Gasen auf lithografische Filme, Martin Glodde

Elektrische Testvorhersage mit hybrider Messtechnik und maschinellem Lernen, Mary Breton

Reduzierung von LER in Si und SiN durch RIE-Optimierung für photonische Wellenleiteranwendungen, Nathan Marchack

Directed Self-Assembly Patterning-Strategien für Phasenwechselspeicheranwendungen, R. Bruce

Materialcharakterisierung für die Prozessintegration von Mehrkanal-Gate-Rundum-(GAA)-Bauelementen, Raja Muthinti

Umfassende Analyse der Linienkanten- und Linienbreitenrauhigkeit für die EUV-Lithographie, Ravi Bonam

Nanomaterialien

- Wolfram-Titan-Legierung Target für Chips

- Hochreines Wolfram-Target für Halbleiterchips

- Gehen Sie über die minimalen Netzwerkanforderungen von Skype hinaus, um beste Ergebnisse zu erzielen

- Plädoyer für neuromorphe Chips für KI-Computing

- IBM-Wissenschaftler erfinden ein Thermometer für die Nanoskala

- IBM 5 in 5:Medizinische Labore „auf einem Chip“ werden als Gesundheitsdetektive dienen, um Krankheiten im Nanomaßstab aufzuspüren

- IBM-Forscher nehmen Innovationspreis für Halbleiterforschung mit nach Hause

- IBM präsentiert eine hybride Blockchain-Architektur für das Internet der Dinge

- Jenseits von AIOps:Beobachtbarkeit für einen effektiven IT-Betrieb

- Die sieben Voraussetzungen für eine optimierte Bearbeitung