Mehrschichtige SnSe-Nanoflake-Feldeffekttransistoren mit niederohmigen Au-Ohm-Kontakten

Zusammenfassung

Wir berichten über p-Typ-Zinnmonoselenid (SnSe)-Einkristalle, die in doppelt versiegelten Quarzampullen unter Verwendung einer modifizierten Bridgman-Technik bei 920 °C gezüchtet wurden. Röntgenpulverdiffraktometrie (XRD) und energiedispersive Röntgenspektroskopie (EDX)-Messungen bestätigen eindeutig, dass das gewachsene SnSe aus einkristallinem SnSe besteht. Der elektrische Transport von mehrschichtigen SnSe-Nanoflocken, die durch Exfoliation von massiven Einkristallen hergestellt wurden, wurde unter Verwendung von Back-Gate-Feldeffekttransistor(FET)-Strukturen mit Au- und Ti-Kontakten auf SiO2 . durchgeführt /Si-Substrate, was zeigt, dass mehrschichtige SnSe-Nanoflocken aufgrund der Sn-Leerstellen auf den Oberflächen der SnSe-Nanoflocken p-Typ-Halbleitereigenschaften aufweisen. Darüber hinaus wurde in 70–90 nm dicken SnSe-Nanoflocken-FETs ein starker Ladungsträger-Screening-Effekt beobachtet. Darüber hinaus wird die Wirkung der Metallkontakte auf mehrschichtige SnSe-Nanoflocken-basierte FETs auch mit zwei verschiedenen Metallen diskutiert, wie z. B. Ti/Au- und Au-Kontakten.

Hintergrund

Transiente Metallchalkogenide bieten eine Reihe von optischen Bandlücken, die diese Materialien für den Einsatz in verschiedenen optischen und optoelektronischen Anwendungen geeignet machen [1]. Dünne Filme dieser Materialien, einschließlich PbTe, PbSe und Bi2 Se3 [2], haben aufgrund ihrer voraussichtlichen Verwendung in optoelektronischen Infrarotgeräten, Strahlungsdetektoren, Solarzellen, Speichergeräten und holographischen Aufzeichnungsgeräten erhebliche Aufmerksamkeit auf sich gezogen [3,4,5,6,7,8]. Zinnmono und Diselenide (SnSe und SnSe2 ) stehen aufgrund ihrer hohen Absorptionskoeffizienten im Fokus der Forschung, was für optoelektronische Anwendungen von Vorteil ist. Darüber hinaus sind diese Materialien vielversprechend für den Einsatz in thermoelektrischen Anwendungen [9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]. Zinnmonoselenid (SnSe) ist ein Halbleiter vom p-Typ mit einer Bandlücke für indirekte zulässige Übergänge nahe ~0,9 eV und für direkte zulässige Übergänge nahe ~1,2 eV, während Zinndiselenid (SnSe2 ) ist ein n-Typ-Halbleiter [6]. Die Kristallstruktur von SnSe ist orthorhombisch und seine Elementarzellenparameter sind a = 11.496 Å, b = 4.151 Å und c = 4,444 Å; diese orthorhombische Struktur wandelt sich bei hoher Temperatur in eine tetragonale Struktur um, die dennoch niedriger ist als der Schmelzpunkt von SnSe2 [25].

Kürzlich wurden Sn-basierte binäre Chalkogenid- und Dichalcogenid-Elektrobauelemente, einschließlich Feldeffekttransistoren (FETs) mit einem großflächigen gemeinsamen Backgate, eingehend untersucht. Insbesondere bei der Charakterisierung von Sn-Dichalkogenid-FETs wurden große Fortschritte erzielt [26, 27]. Im Jahr 2016, Pei et al.. gemeldet ein paar Schichten SnSe2 FET mit einem hohen Ein-/Aus-Verhältnis von ~10 4 mit einer oberen Deckschicht aus einem Polymerelektrolyten [27]. Guo et al. berichtete auch über ein hochmobiles, mehrschichtiges SnSe2 FET mit einer Dicke von ~8,6 nm [28]. Aus früheren Arbeiten wurde bestätigt, dass dünne SnSe-Filme mit niedriger Trägerkonzentration eine hohe Mobilität und ein Strom-Ein/Aus-Verhältnis von SnSe2 . ergeben FETs. Trotz dieser Bemühungen bei der Verwendung von SnSe2 , jedoch wurde nicht über die elektrische Charakterisierung von SnSe-FETs, die durch Exfoliation von Einkristallen hergestellt wurden, berichtet. Eine detaillierte Charakterisierung des elektrischen Transports in mehrschichtigem SnSe2 Flocken müssen verwendet werden, um die elektrischen Transporteigenschaften von Zinnchalkogeniden wie SnSe-Nanoflocken zu beurteilen, da von einzelnen SnSe-Kristallen eine hohe Trägermobilität von ~7835 cm 2 . erwartet wird /V s [29].

In dieser Arbeit haben wir einkristallines SnSe charakterisiert, das mit einer modifizierten Bridgman-Methode gezüchtet wurde. Der elektrische Transport in mehrschichtigen SnSe-Nanoflocken-FETs, die durch Exfoliation aus massiven Einkristallen hergestellt wurden, wurde erstmals unter Verwendung von Back-Gate-FET-Strukturen auf SiO2 . charakterisiert /Si-Substrate. Darüber hinaus wurde der Einfluss von Metallkontakten auf mehrschichtige SnSe-Nanoflocken-basierte FETs auch für zwei verschiedene Kontakttypen (Ti/Au und Au) untersucht, da die Austrittsarbeit des Kontaktmetalls die Leitung von Lochträgern durch die Schottky-Barriere an der bestimmt Metall-SnSe-Nanoflake-Schnittstelle.

Methoden

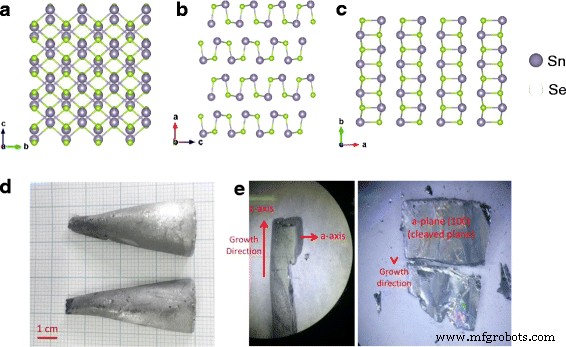

SnSe hat bei Raumtemperatur eine geschichtete orthorhombische Kristallstruktur [24]. Abbildung 1a–c zeigen die perspektivischen Ansichten der SnSe-Kristallstruktur entlang des a , b , und c axiale Richtungen. Wie in Abb. 1c gezeigt, sind SnSe-Platten mit einer Zweiatomschicht gerillt, während eine leichte Spaltung in den Kristallen entlang der (100)-Ebene auftritt (Abb. 1b). Einzelne SnSe-Kristalle wurden unter Verwendung der modifizierten Bridgman-Methode gezüchtet, wie zuvor beschrieben [24, 30]. Stöchiometrische Mengen an Sn (99,999 % Schrot, Alfa Aesar) und Se (99,999 % Pulver, Alfa Aesar) wurden zunächst in einer doppelt verschlossenen Quarzampulle zu einem Barren (~20 g) geschmolzen. Die Rohstoffe wurden langsam auf 500 °C erhitzt und 10 h dort verweilt, dann weitere 10 h bei 920 °C gehalten, bevor der Ofen abgeschaltet wurde. Der erhaltene Barren wurde zu Pulver gemahlen und in ein kegelförmiges Quarzrohr gefüllt, evakuiert und flammversiegelt. Dieses geladene kegelförmige Quarzrohr wurde in ein größeres Quarzrohr eingebracht. Das äußere Rohr wurde mit gasförmigem Ar gefüllt, um eine Explosion und Oxidation zu verhindern, und dann flammenversiegelt. Die beschickte Quarzampulle wurde an der Stelle platziert, an der der Temperaturgradient im Vertikalrohrofen am größten war. Der vertikale Rohrofen wurde 20 h lang langsam auf 970 °C erhitzt, 10 h lang gehalten und dann mit einer Geschwindigkeit von 0,5 °C/h auf 830 °C abgekühlt. Der Ofen wurde weitere 24 h auf 830 °C gehalten und dann mit einer Geschwindigkeit von 100°C/h auf 500°C abgekühlt, bevor der Ofen abgeschaltet wurde.

a –c Kristallstruktur von SnSe-Kristallen entlang a -, b -, und c -axiale Richtungen. d Fotografie eines gewachsenen einkristallinen SnSe. e Fotografien von gespaltenen SnSe-Kristallen entlang des a -Achse (100) Ebene. Draufsichten der gespaltenen Ebene (100) des SnSe-Einkristalls (rechtes Bild in d )

Ergebnisse und Diskussion

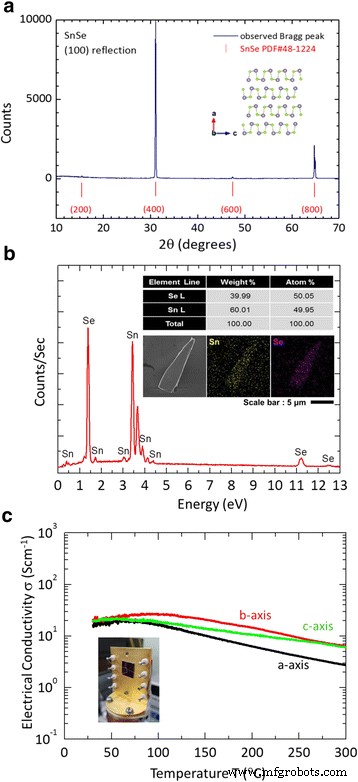

Ein kegelförmiger SnSe-Kristall (Durchmesser 30 mm; Länge 70 mm) wurde erhalten und ist in Abb. 1d–e gezeigt. Der erhaltene Kristall wurde aufgrund eines Risses, der bei der Extraktion des Kristalls aus der Quarzampulle auftrat, in zwei Teile geteilt (Abb. 1d). Die Qualität der gewachsenen SnSe-Kristalle wurde unter Verwendung eines Pulverröntgendiffraktometers (XRD, New D8-Advance, Bruker-AXS, Deutschland) mit Cu Kα . überprüft (λ = 1,5406 Å). Abbildung 2a zeigt das XRD-Muster der Leistungsbeugungsdatei (PDF) 48–1224 für orthorhombisches SnSe zusammen mit dem Muster für das kristallographische a Achse, die senkrecht zur gespaltenen Ebene (100) des SnSe-Kristalls ist. Wie in Abb. 2a gezeigt, deutet das XRD-Muster von einkristallinem SnSe stark auf einen orthorhombischen Einphasenkristall mit einer Raumgruppe Pnma . hin [31], was auf eine starke Vorzugsorientierung mit (h00)-Reflexen hinweist, was in guter Übereinstimmung mit einem früheren Bericht [32] ist. Darüber hinaus waren die vorherrschenden Peaks (400) und (800) bei 2θ = 31,081° bzw. 64,818°, wie in Abb. 2a [33] gezeigt. Wie in Abb. 2b gezeigt, ergab die energiedispersive Röntgenspektroskopie (EDX) ein Sn:Se-Atomverhältnis von 1:1, was das stöchiometrische Verhältnis von Sn und Se bestätigt (Einschub von Abb. 2b). Die Einschübe von Fig. 2b zeigen auch ein Rasterelektronenmikroskop (SEM)-Bild und eine EDX-Abbildung eines SnSe-Nanoflocken-FET mit einer Bauelementdicke von 90 nm. Dieses Ergebnis stimmt gut mit früheren Berichten überein [24, 33]. Darüber hinaus wurde die elektrische Leitfähigkeit von einkristallinem SnSe (Einschub in Abb. 2b) für Temperaturen im Bereich von 30‒300 K unter Verwendung der herkömmlichen Vierpunkt-Sondenmethode gemessen. Abbildung 2c zeigt die temperaturabhängige elektrische Leitfähigkeit von SnSe-Einkristallen entlang dreier unterschiedlicher kristallographischer Richtungen, was auf ein ähnliches temperaturabhängiges Verhalten und ein ähnliches Anisotropieverhalten aufgrund unterschiedlicher Lochbeweglichkeiten in SnSe entlang der verschiedenen axialen Richtungen hindeutet. Wie in Abb. 2c gezeigt, ist die elektrische Leitfähigkeit entlang des b - und c -Achse bei 300 K wurde mit ~6.00 S cm −1 . bestimmt , was ~2,2 mal größer ist als das für a -Achse (~2,7 S cm −1 ). Dieses Ergebnis stimmt gut mit früheren Ergebnissen für einkristallines SnSe überein [24]. In Abb. 2c ist die temperaturabhängige elektrische Leitfähigkeit von einkristallinem SnSe für den Halbleiterbereich (30–100 K) und für den metallischen Bereich (>100–300 K) dargestellt. Oberhalb von 100 K zeigten die gewachsenen SnSe-Kristalle ein metallisches Transportverhalten, das mit früheren Beobachtungen übereinstimmt [24].

a XRD-Muster von SnSe-Einkristallen, das eine klare (h00) Beugung zeigt. b EDX-Spektrum der SnSe-Einkristalle. Einfügen zeigt die detaillierten Informationen zum Atomverhältnis von Sn und Se. Einsätze zeigen ein SEM-Bild und ein EDX-Mapping eines SnSe-Nanoflake-FET mit einer Bauteildicke von 90 nm. c Temperaturabhängige elektrische Leitfähigkeit der SnSe-Einkristalle für Temperaturen von 30–300 K, gemessen mit der Vierpunkt-Sondenmethode

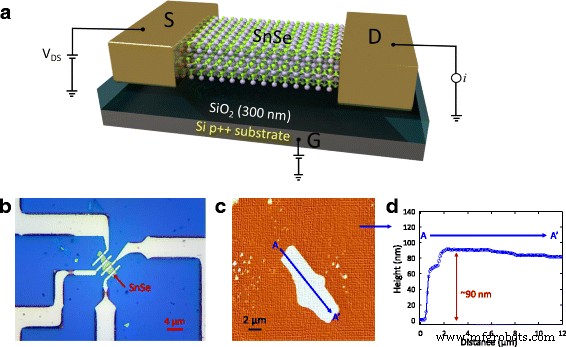

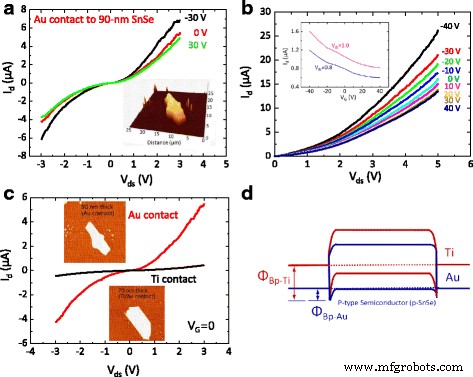

SnSe-FET-Vorrichtungen wurden wie folgt hergestellt. Zuerst wurden SnSe-Nanoflocken mechanisch auf ein 300 nm dickes SiO2 . abgeblättert /p ++ Si-Substrat aus einzelnen SnSe-Kristallen, leicht in der (100)-Ebene mit der bekannten Scotch-Tape-Methode spaltbar (Abb. 1e) [26, 27, 34]. Messungen des elektrischen Transports in präparierten einzelnen SnSe-Nanoflocken-FETs wurden bei Raumtemperatur in der Back-Gate-FETs-Konfiguration durchgeführt. Abbildung 3a zeigt schematisch FET-Bauelemente auf SnSe-Nanoflockenbasis mit einem großflächigen Backgate. In dieser Studie wurden zwei SnSe-Nanoflocken (70 und 90 nm dicke SnSe-Nanoflocken) auf dem SiO2 . hergestellt /Si-Substrat. Die SnSe-FETs wurden mit dem Standard-Elektronenstrahl-Lithografieverfahren hergestellt, gefolgt von zwei Metallisierungsarten, d. h. Au (Dicke 100 nm) und Ti/Au (Dicke 10/100 nm) wurden als ohmsche Kontakte auf SnSe-Nanoflocken betrachtet. Vor dem Metallisierungsprozess wurde eine gepufferte Oxidätzung (BOE) durchgeführt, um die Polymer- und Oxidrückstände auf den Oberflächen der Nanoflocken zu entfernen. Abbildung 3b zeigt ein optisches Bild eines SnSe-Nanoflocken-FET mit einer Bauteildicke von 90 nm. Die Dicken der SnSe-Nanoflocken wurden mit einem Rasterkraftmikroskop (AFM) bei Raumtemperatur gemessen (Abb. 3c–d). Wie in Fig. 3b und Einschub von Fig. 2b gezeigt, hatte der hergestellte 90 nm dicke SnSe-FET die Kanallänge (L ) von 5 μm und Breite (W ) von 4,71 μm, während für den 70 nm dicken SnSe-FET L war 5 μm und W war 6 μm. Die gesamte Stromspannung (I -V ) wurden unter Verwendung eines Halbleiterparameteranalysators (HP 4155C, Agilent Technologies, USA) an einer elektrisch abgeschirmten Sondenstation bei Raumtemperatur gemessen. Abbildung 4a zeigt den Drainstrom (I d ) als Funktion der Gatespannung (V g ), für die 90 nm dicke SnSe-Nanoflocke, für die Source-Drain-Spannungen (V ds ) von −30, 0 und 30 V bei Raumtemperatur, was auf ein klares p-Typ-Halbleiterverhalten hinweist, das hauptsächlich auf die Sn-Leerstellen zurückgeführt wird, wie zuvor beschrieben [15, 16, 22, 24, 35,36,37 ,38,39]. Das Ergebnis in Abb. 4a impliziert, dass metallisches AU mit seiner hohen Austrittsarbeit voraussichtlich schwache ohmsche Kontakte auf SnSe-Nanoflocken bildet, was auf eine niedrigere Schottky-Barriere für das Leitungsband von SnSe-Nanoflocken hinweist. Eine ausführlichere Diskussion für Austrittsarbeiten verschiedener Metalle wird später bereitgestellt. Abbildung 4b zeigt I d vs. V ds für verschiedene V g , im Bereich von –40–40 V, in Schritten von 10 V. Aus Abb. 4b ist die Lochbeweglichkeit (μ p ) wird mit ~2,7 cm 2 . bestimmt /V s, erhalten von μ p = t m [L ⁄ (WC Ochse V ds)], wobei t m ist die Transkonduktanz (=dI d /dV g = 2,89 × 10 − 8 A /V ), L ist die Länge (~5,1 μm), W ist die Breite (~4,75 μm), V ds die Drain-Source-Spannung (~1 V) des SnSe-FET ist und C Ochse (=ε r ε 0 /d = 11,5 nF/cm 2 ) mit ε r (Dielektrizitätskonstante) von 3,9 und d (die Dicke der Oxidschicht) von 300 nm ist die Kapazität pro Flächeneinheit des SnSe-Nanoflocken-FET mit Back-Gate. Die bewertete Lochbeweglichkeit der mechanisch abgeblätterten SnSe-Nanoflocken-FETs ist viel kleiner als die epitaktischer SnSe-Dünnschichten (~60 cm 2 /V s), hergestellt durch gepulste Laserabscheidung auf MgO-Substraten unter Verwendung von Se-reichen Targets [40]. Der hier erhaltene Wert ist jedoch ~1,8-mal größer als der für einkristalline SnSe-Nanoplatten erhaltene (~1,5 cm 2 /V s) [33]. Diese relativ geringe Lochmobilität kann einer starken Phononenstreuung aufgrund der Sn-Leerstellen auf der SnSe-Oberfläche [18, 36, 41, 42] und einer relativ hohen Schottky-Barriere an der Grenzfläche der Au-Metall-SnSe-Nanoflocken zugeschrieben werden.

a Schema eines mechanisch abgeblätterten SnSe-Nanoflake-FET auf einem SiO2 /p ++ Si-Substrat. b Optisches Bild eines hergestellten SnSe-Nanoflake-FET, der für elektrische Transportmessungen verwendet wurde. c AFM-Bild einer SnSe-Nanoflocke auf einem SiO2 /Si-Substrat. d AFM-Höhenprofil einer SnSe-Nanoflocke zur Schätzung der Dicke und Herstellung von FET-Bauelementen

a Drainstrom (I d ) als Funktion der angelegten Source-Drain-Spannung (V ds ), für die Gatespannungen (V g ) von -30, 0 und 30 V für einen 90 nm dicken SnSe-Nanoflocken-FET bei Raumtemperatur. b Ich d vs. V ds für V g im Bereich von -40–40 V in Schritten von 10 V für den 90 nm dicken SnSe-Nanoflake-FET. Der Einschub zeigt ich d vs. V g für V ds von 0,8 und 1,0 V, gemessen bei Raumtemperatur. c Ich d vs. V ds ohne Voreingenommenheit V g (=0) für Au- und Ti-Kontakte auf einem SnSe-Nanoflocken-FET. Der Einschub zeigt ein AFM-gescanntes Bild von SnSe-Nanoflocken. d Schemata der Energiebanddiagramme von zwei Metallen, Au und Ti, auf p-Typ-SnSe-Halbleitern

Darüber hinaus beobachteten wir eine schwache Gate-Abstimmung der Leitfähigkeit im Verarmungsbereich des I d vs. V ds (Abb. 4c) und ein niedriges Strom-Ein/Aus-Verhältnis (~2 bei V ds von 1 V, Einschübe von Fig. 4c) im p-SnSe-Nanoflocken-FET mit Au-Metallkontakten. Ein ähnliches Verhalten wurde für andere zweidimensionale (2D) halbleitende Materialien mit ähnlicher Dicke berichtet, einschließlich SnS-FETs (Dicke, ~50–80 nm) [43], ~15,8 nm dicke SnSe-Nanoplatten [33], ~80 -nm-dickes MoS2 [44] und ~84 nm dickes SnSe2 [26]. Dieses Verhalten kann durch den endlichen Ladungsträger-Abschirmungslängeneffekt aufgrund der Existenz einer oberflächlichen leitfähigen Oberflächenschicht in FET-Bauelementen mit Dicken größer als die Abschirmungslänge \( \left(\sqrt{\varepsilon {K}_B T}{e }^2 p\right) \), wobei ε , K B , und p sind die Dielektrizitätskonstante des Halbleiters, die Boltzmann-Konstante, bzw. die Lochträgerdichte [43].

Metallkontakte bestimmen maßgeblich die Eigenschaften von 2D-FET-Bauelementen [45]. Um die Wirkung der Austrittsarbeit von Metall auf SnSe zu bestimmen, haben wir Au (Austrittsarbeit, ~5,1 eV) und Ti (Austrittsarbeit, ~4,3 eV) als Metallkontakte auf SnSe-Nanoflocken betrachtet. Abbildung 4c zeigt typisches I d vs. V ds Kurven ohne Gate-Modulation (V g = 0) für SnSe-Nanoflocken-FETs mit Au- und Ti-Kontakten, was auf einen höheren Gesamtwiderstand für Ti (~15,4 MΩ) im Vergleich zu Au (~0,56 MΩ) hinweist. Somit ist die Schottky-Barriere an der Metall-SnSe-Grenzfläche für Ti höher (Abb. 4c). Dieses Verhalten wird immer bei allen SnSe-FETs mit Ti-Kontakten beobachtet. Wie in Fig. 4d gezeigt, nimmt die Höhe der Schottky-Barriere für Löcher zu, wenn die Austrittsarbeit des Metalls abnimmt. Somit können Metalle wie Pd, Au und Pt mit großen Austrittsarbeiten als ohmsche Kontakte auf p-SnSe-Nanoflocken-FETs geeignet sein, da für diese Metalle die Höhe der Schottky-Barriere für die Injektion von Löchern geringer ist. Bei weiteren Metallen sollte der Kontaktwiderstand gemessen werden, um deren Eignung als Metallkontakte auf SnSe-Nanoflakes zu bestimmen. Dieses Problem wird derzeit mit der Methode der Übertragungslänge behoben.

Schlussfolgerungen

Zusammenfassend wurden mehrschichtige SnSe-Nanoflocken gezüchtet, abgeblättert und für SnSe-FET-Kanäle mit einer Back-Gate-FET-Struktur auf SiO2 . charakterisiert /Si-Substrate. Elektrische Transportmessungen zeigten, dass mehrschichtige SnSe-Nanoflocken mit Au-Metallkontakten p-Typ-Halbleitereigenschaften mit einer relativ niedrigen Schottky-Barriere und einem niedrigen Kontaktwiderstand auf abgeblätterten SnSe-Nanoflocken-FETs aufweisen. Darüber hinaus betonen wir, dass diese Studie die erste ist, die über mechanisch abgeblätterte SnSe-Nanoflake-basierte FETs berichtet, und wir sind zuversichtlich, dass unsere SnSe-Nanoflake-FETs für 2D-Elektrogeräte sowie für Energy Harvesting-Anwendungen, einschließlich der zukünftigen Erzeugung von Thermoelektrizität, sehr vielversprechend sind .

Nanomaterialien

- Transistoren, Sperrschicht-Feldeffekt (JFET)

- Transistoren, Feldeffekt mit isoliertem Gate (IGFET oder MOSFET)

- Übergangs-Feldeffekttransistoren

- Feldeffekttransistoren mit isoliertem Gate (MOSFET)

- Einführung in Junction-Feldeffekttransistoren (JFET)

- Einführung in Feldeffekttransistoren mit isoliertem Gate

- Luftabstandshalter für 10-nm-Chips

- Ein Nanometersprung auf Billionen von Transistoren

- Unüberwachtes Lernen mit künstlichen Neuronen

- Auswirkung einer In-situ-Annealing-Behandlung auf die Mobilität und Morphologie von TIPS-Pentacen-basierten organischen Feldeffekttransistoren