Neuartiger SCR mit hoher Haltespannung und eingebetteter Trägerrekombinationsstruktur für Latch-up-immunen und robusten ESD-Schutz

Zusammenfassung

Ein neuartiger CMOS-prozesskompatibler siliziumgesteuerter Gleichrichter (HHV-SCR) mit hoher Haltespannung zum Schutz vor elektrostatischer Entladung (ESD) wird vorgeschlagen und durch Simulation und Tests mit Übertragungsleitungsimpulsen (TLP) demonstriert. Der neu eingeführte Loch- (oder Elektronen-) Rekombinationsbereich H-RR (oder E-RR) rekombiniert nicht nur die Minoritätsträger in der Basis des parasitären PNP- (oder NPN) Transistors durch die N+ (oder P+) Schicht, sondern bietet die zusätzliche Rekombination, um die Oberflächenlawinenträger durch neu hinzugefügte P+ (oder N+) Schicht in H-RR (oder E-RR), was eine weitere Verbesserung der Haltespannung (V h ). Verglichen mit dem gemessenen V h von 1,8 V eines niederspannungsgesteuerten siliziumgesteuerten Gleichrichters (LVTSCR), der V h des HHV-SCR auf 8,1 V erhöht werden, während ein ausreichend hoher Fehlerstrom (I t2> 2,6 A). Es wird eine mehr als vierfache Verbesserung der Gütezahl (FOM) erreicht.

Einführung

Mit der Entwicklung der integrierten Halbleitertechnologie und der konsequenten Miniaturisierung der Strukturgröße von Halbleiterbauelementen werden die durch ESD verursachten Bauelementschäden immer schwerwiegender. Auf Kosten einer großen Chipfläche wurden konventionelle Bauelemente wie Dioden- und Gate-geerdete N-Kanal-MOSFETs (ggNMOS) mit normaler ESD-Robustheit berichtet [1]. Um eine verbesserte ESD-Fähigkeit mit einer kleineren Bauteilabmessung zu realisieren, wurde der niederspannungsgesteuerte Silizium-gesteuerte Gleichrichter (LVTSCR) aufgrund seiner Hochstromfähigkeit pro Flächeneinheit als attraktives Bauteil angesehen [2]. Für Niederspannungsanwendungen aufgrund der eingebetteten niedrigen Triggerspannung (V t1 ) ggNMOS ist der LVTSCR mit ausgezeichneter ESD-Robustheit in der Lage, eine schnellere ESD-Reaktionsgeschwindigkeit bereitzustellen, als dies bei einem herkömmlichen SCR der Fall ist. Die starke inhärente positive Rückkopplung verursacht jedoch ein extrem niedriges V h (1~2 V), die für Latch-up und vorübergehende Fehlauslösung verantwortlich ist [3]. Solche negativen Effekte können durch einfaches Erhöhen von V . effektiv unterdrückt werden h [3,4,5,6,7,8,9,10,11]. Das Gerät ist frei von Latch-up und vorübergehenden Fehlauslösungen, während die V h höher ist als die Versorgungsspannung (VDD). Dementsprechend wurden die N+ESD-Region und die P+LDD-Region in SCR mit zusätzlichen Masken und Ionenimplantationsschritten hinzugefügt, um V . zu verbessern h [3]. Die ESD-Robustheit kann sich jedoch aufgrund der zusätzlichen Verlustleistung zusammen mit der erhöhten V . verschlechtern h . Darüber hinaus ist die Emitter-Spannungsklemmtechnik für V h Verbesserung mit akzeptablem Fehlerstrom (I t2 ) wurde ebenfalls vorgeschlagen [5]. Trotzdem ist das V h in den oben genannten Ansätzen ist nicht einstellbar, was bei vielseitigen Anwendungen immer noch Unannehmlichkeiten und Einschränkungen darstellt.

In diesem Brief wird ein neuartiger siliziumgesteuerter Gleichrichter mit hoher Haltespannung (HHV-SCR) vorgeschlagen und durch TCAD-Simulation und TLP-Tests demonstriert. Gleichzeitig erreicht das Gerät hohe V h , hoch ich t2 , und einstellbares V h ohne zusätzliche Masken und Schritte. Der TLP-Test wurde durchgeführt, um zu bestätigen, dass die V h kann effektiv verbessert werden, während ein ausreichend hohes I . aufrechterhalten wird t2 . Den Testergebnissen zufolge weist der HHV-SCR ein über viermal höheres V . auf h als im LVTSCR mit der vernachlässigbaren Verschlechterung in I t2 .

Methode

In dieser Arbeit wird ein neuartiger Hochhaltespannungs-SCR mit eingebetteter Trägerrekombinationsstruktur untersucht. In der numerischen Simulation werden die physikalischen Modelle IMPACT.I, BGN, CONMOB, FLDMOB, SRH und SRFMOB verwendet. Basierend auf dem Modell sind H-RR und E-RR optimiert, um hohe V . zu erreichen h und hohes P M . Die hergestellten HHV-SCRs und LVTSCR werden durch das TLP-System getestet.

Struktur und Mechanismus

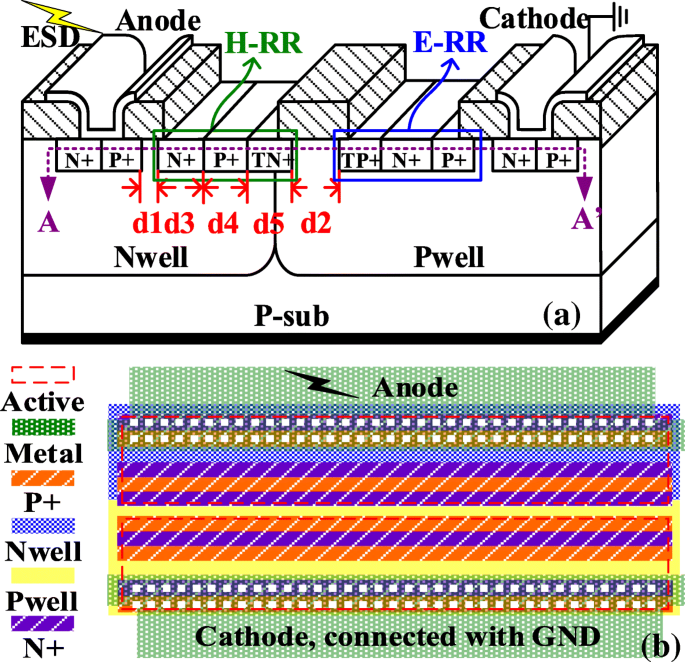

Die schematische Querschnittsansicht des vorgeschlagenen HHV-SCR und das Layoutdiagramm sind in Fig. 1a bzw. b gezeigt. Die neu eingeführten H-RR und E-RR, die durch schwebende N+ und P+ gebildet werden, sind identisch mit N+ und P+ im Anoden- bzw. Kathodenbereich. Das schwebende N+ in H-RR (oder schwebendes P+ in E-RR) wird neben dem P+-Gebiet in der Anode (oder dem N+-Gebiet in der Kathode) platziert. Darüber hinaus befindet sich das neue Floating P+ in H-RR (oder Floating N+ in E-RR) auch neben dem zuvor erwähnten Floating N+ in H-RR (oder Floating P+ in E-RR). Der Low-Trigger N+ in H-RR (TN+) und Low-Trigger P+ in E-RR (TP+) werden ebenfalls durch die gleichen Prozesse wie der N+ (oder P+) Bereich in der Anode (oder Kathode) hergestellt, um sicherzustellen, dass V t1 in einem akzeptablen Bereich. Als positive ESD-Spannung (V ESD ) bis zu einem bestimmten Pegel ansteigt, bricht der TN+/P-Wanne/TP+-Übergang mit einer niedrigen Durchbruchspannung zuerst durch, gefolgt vom Snapback der parasitären Transistoren, die durch den Lawinenstrom ausgelöst werden. Das starke positive Feedback der parasitären BJTs ist verantwortlich für das erheblich niedrige V h des LVTSCR. Im HHV-SCR rekombiniert das N+ in H-RR (oder das P+ in E-RR) die Minoritätsträger, die von der Kante der Anode P+ (oder Kathode N+) injiziert werden, was die Stromverstärkung reduziert (β ) des parasitären PNP (oder NPN) und eliminiert den bipolaren Oberflächeneffekt. Wichtig ist, dass das P+ in H-RR (oder das N+ in E-RR) den Oberflächenpfad mit niedrigem Widerstand blockiert, indem die Oberflächenelektronen (oder -löcher) rekombiniert werden. Verglichen mit dem H-RR ohne P+ (oder E-RR ohne N+) bietet das neue P+ in H-RR (oder das N+ in E-RR) die zusätzliche Rekombination, um die von der Kathode injizierten Oberflächenelektronen (oder Löcher) zu eliminieren ( oder Anode) und die durch Stoßionisation induzierten (in Abb. 3a gezeigt), was die weitere Erhöhung von V . bewirkt h . Durch die Kombination dieser Modifikationen wird eine signifikante Verbesserung des FOM . erreicht wird verifiziert. Die Gütezahl (FOM) wird aus [7] zitiert und ist definiert als die tolerierbare Leistungsdichte eines einzelnen Geräts, gegeben durch FOM=(V h ·ich t2 )/(N ·W ) um das V auszuwerten h und ich t2 Leistung eines einzelnen Gerätes. Im Allgemeinen begleitet von der Verbesserung von V h Leistung, es verursacht immer noch die Verschlechterung von I t2 wegen der höheren Verlustleistung. Daher bedeutet ein höheres FOM, dass das einzelne Gerät die höhere Strombelastbarkeit bei höheren V . erreichen kann h Niveau (N ist die Nummer der Stapelvorrichtung; W ist die Gerätebreite).

a Die schematische Querschnittsansicht des vorgeschlagenen HHV-SCR. b Das Layoutdiagramm des vorgeschlagenen HHV-SCR

Ergebnisse und Diskussion

Simulierte Ergebnisse

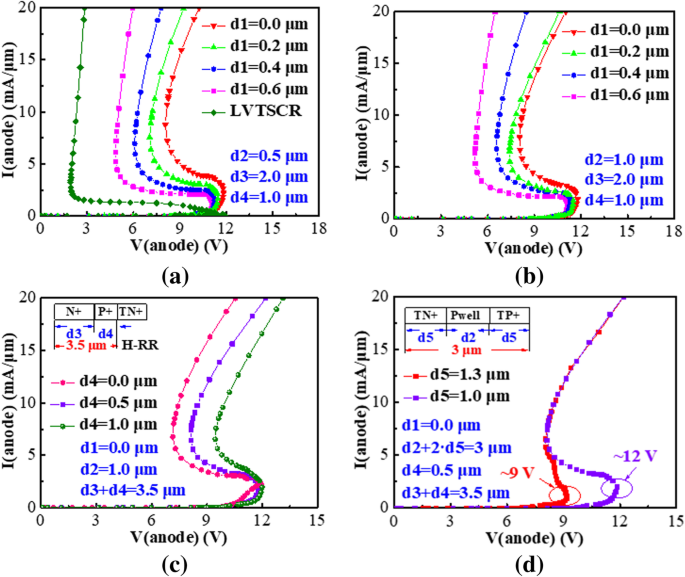

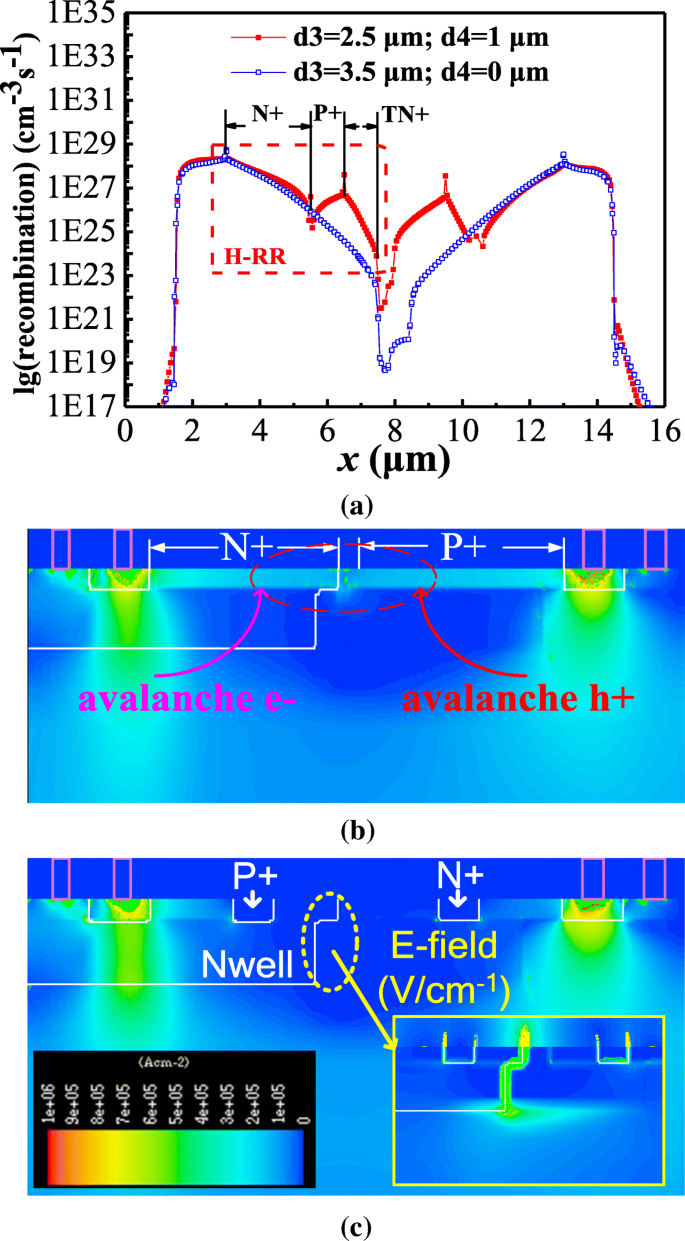

Die Geräteeigenschaften wurden von TCAD Medici untersucht und simuliert, wobei die entsprechenden Modelle wie Stoßionisation und konzentrationsabhängiges Mobilitätsmodell verwendet wurden. Die simulierten I-V-Kurven der LVTSCR und HHV-SCRs sind in Abb. 2 dargestellt. Die V h des LVTSCR beträgt nur 1,8 V, während die V h des HHV-SCR wird von 4,6 V auf 8,1 V verbessert, wobei d1 von 0,6 µm auf 0 µm für d2 =0,5 µm verringert wird. Tatsächlich wird das kleinere d1 für eine verbesserte Rekombinationsfähigkeit von N+ in H-RR (oder P+ in E-RR) bevorzugt, um ein niedrigeres β . zu erhalten , was erklärt, dass der HHV-SCR immer das höchste V . erreicht h für d1 =0 µm. Die simulierten Ergebnisse in Abb. 2b zeigen, dass die V h der HHV-SCR wird mit einer Erhöhung von d2 von 0,5 auf 1 µm aufgrund der zunehmenden Gerätelänge weiter verbessert. Zur Demonstration ist P+ in H-RR (oder N+ in E-RR) auch ein Schlüsselfaktor zur Erhöhung von V h . Die simulierten Ergebnisse sind in Abb. 2c dargestellt. Wenn das H-RR (oder E-RR) mit festem d3 + d4 vollständig durch starke Dotierung N+ (oder P+) gebildet wird (zB d3 =3,5 µm, d4 =0 µm), wird das simulierte V h beträgt 7,1 V. Durch Einfügen von P+ in H-RR und N+ in E-RR mit festem d3 + d4 (z. B. d3 =2,5 µm, d4 =1,0 µm), wird das simulierte V h kann auf etwa 9,5 V erhöht werden. Es kann gefolgert werden, dass das neue P+ in H-RR (oder N+ in H-RR) bei der Rekombination von Oberflächenlawinenelektronen (oder Löchern) wirksam ist, um den Oberflächenstrompfad zu blockieren. Daher ist ein höheres V h ist erforderlich, damit der HHV-SCR den gleichen Haltestrom (I h ). Die in Fig. 3a gezeigte AA&spplus;-Linie der Rekombinationskurve allein zeigt die Zunahme der Rekombinationsrate, die durch neues P+ in H-RR (oder N+ in E-RR) induziert wird. TN+ und TP+ werden übernommen, um die V . zu gewährleisten t1 in einem akzeptablen Bereich. Durch Einstellen von d2 und d5 auf die festen d5 + d2 + d5 wird das V t1 des HHV-SCR kann von 12 V auf 9,0 V erheblich reduziert werden, um das Designfenster von 5-V-Schaltungen mit vernachlässigbaren Auswirkungen auf V . zu erfüllen h , gezeigt in Abb. 2d. Die Stromverteilungsdiagramme der simulierten Geräte am Haltepunkt sind auch in Abb. 3b bzw. c dargestellt. Verglichen mit der Stromverteilung im HHV-SCR mit d3 =3,5 μm, d4 =0 μm ist der Oberflächenstrompfad im vorgeschlagenen HHV-SCR aufgrund der zusätzlichen Rekombinationsrate blockiert, die von P+ in H-RR und N+ in E . profitiert -RR.

Simulierte Snapback-I-V-Eigenschaften von konventionellem LVTSCR und vorgeschlagenem HHV-SCR, wobei der d1 von 0 µm auf 0,6 µm bei a . ansteigt d2 =0,5μm und b d2 =1μm. c Die I-V-Kurven von HHV-SCR mit unterschiedlichen d3 und d4 für das feste d3 + d4 (d3 + d4 =3,5 µm). d Die I-V-Kurven von HHV-SCR mit verschiedenen V t1

a Die Rekombinationsverteilungskurven und die aktuellen Verteilungen von HHV-SCR mit (b ) d3 =3,5 µm, d4 =0 µm und (c ) d3 =2,5 µm, d4 =1 µm

Experimentelle Ergebnisse

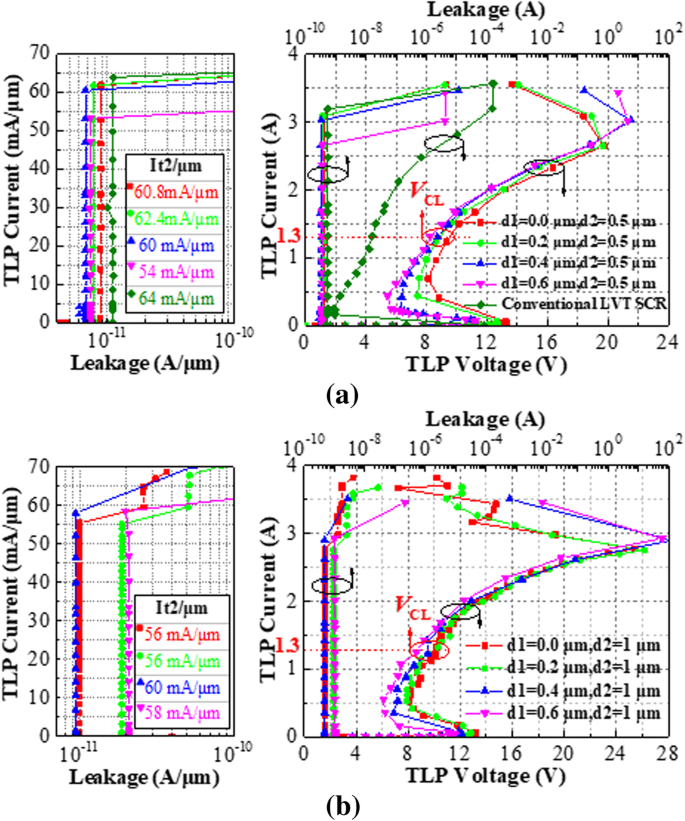

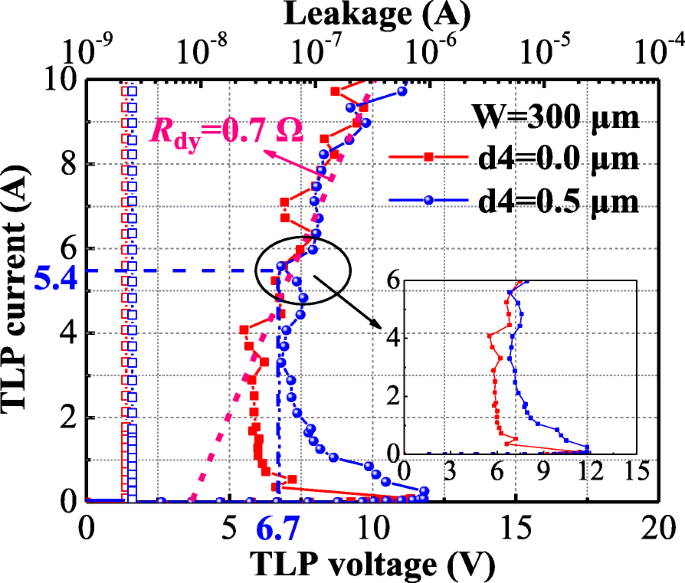

Die hergestellten Geräte werden durch das TLP-System getestet. Die Gesamtbreiten (W) aller getesteten SCRs betragen 50 µm und mit Einzelfinger für den Parametervergleich (Tabelle 1). Alle getesteten Geräte belegen die ähnliche Layoutfläche. Die Geräteparameter sind in Tabelle 2 dargestellt. Abbildung 4a zeigt die TLP-Messkurven der HHV-SCRs mit d2 =0,5 µm (genannt Geräte B1) und die LVTSCR. Nach den experimentellen Ergebnissen ist das V h des HHV-SCR wird von 5,5 auf 8,0 V erhöht, wobei der d1 von 0,6 µm auf 0,0 µm verringert wird, was viel höher ist als 1,8 V, die beim herkömmlichen LVTSCR erhalten werden. Wenn d2 von 0,5 auf 1 µm ansteigt, erhalten die entsprechenden HHV-SCRs (sogenannte Geräte B2) ein höheres V h in Abb. 4b gezeigt. Unter Berücksichtigung des Designfensters ist die Klemmspannung (V CL ) unter dem angegebenen Index ist auch ein Schlüsselparameter zur Bewertung der Klemmfähigkeit. Aus den getesteten Ergebnissen ergibt sich das V CL des Einzelfinger-HHV-SCR wird auch beim HBM =2 kV im akzeptablen Bereich gehalten (I TLP =1,3 A), obwohl die Fingerbreite nur 50 µm beträgt. Allerdings können nicht alle Geräte das berechtigte V . bereitstellen CL unter der stärkeren ESD-Belastung aufgrund des hohen V h und großer dynamischer Widerstand (R dy ) induziert durch zu geringe Gerätebreite. Um die höhere On-Chip-ESD-Anforderung zu erfüllen, wird die Fingerbreite auf die akzeptablen 300 µm für d1 =0,6 µm, d4 =0,5 µm und d1 =0,6 µm, d4 =0 µm erweitert. Der in Abb. 5 gezeigte TLP-Test zeigt, dass der HHV-SCR mit d4 =0,5 µm den extrem niedrigen R . aufweist dy (ca. 0,7 Ω), überlegene ESD-Robustheit (I t2> 10 A) und hohe V h von 6,7 V. Es kann beobachtet werden, dass die V CL beträgt nur 6,7 V am I TLP =5,4 A (HBM =8 KV). Darüber hinaus ist das höhere V h profitiert von P+ in H-RR (oder N+ in E-RR) ist auch bewiesen, verglichen mit der TLP-Kurve von SCR mit d4 =0 μm. Die getesteten Ergebnisse von 50-μm-Einfingergeräten sind in Tabelle 1 aufgeführt.

Experimenteller Fehlerstrom bei der Einheitsbreite und entsprechende TLP I-V-Eigenschaften von herkömmlichen LVTSCR und vorgeschlagenen HHV-SCRs mit a d2 =0,5 μm und b d2 =1 μm bei W =50 μm

Experimentelle TLP-Charakteristik von HHV-SCR mit d4 =0,0 µm und d4 =1,0 µm bei d1 =0,6 µm, W =300 μm

Schlussfolgerung

Ein neuartiger CMOS-prozesskompatibler HHV-SCR wird durch TCAD-Simulation und TLP-System untersucht und vermessen. Im Vergleich zum herkömmlichen LVTSCR bietet der HHV-SCR ein deutlich verbessertes V h (eine Verbesserung von über 450% im V h erreicht wird) und ohne die Chipfläche zu opfern. Außerdem ist das V h des HHV-SCR kann von 5,5 V bis 8,1 V eingestellt werden, um den unterschiedlichen V h Anforderungen mit vernachlässigbarer Verschlechterung in I t2 . In Bezug auf P M , verglichen mit dem herkömmlichen LVTSCR, wird auch eine Verbesserung von über 200 % erreicht.

Verfügbarkeit von Daten und Materialien

Alle während dieser Studie generierten oder analysierten Daten sind in diesem veröffentlichten Artikel enthalten.

Nanomaterialien

- Ein Überblick über die IC-Technologie für Mikrocontroller und eingebettete Systeme

- Maxime:dualer IO-Link-Transceiver mit DC-DC-Regler und Überspannungsschutz

- TRS-STAR:robuste und lüfterlose Embedded-Systeme von avalue

- Neuartige biokompatible Au-Nanostars@PEG-Nanopartikel für die In-vivo-CT-Bildgebung und renale Clearance-Eigenschaften

- Monodisperse Kohlenstoff-Nanosphären mit hierarchischer poröser Struktur als Elektrodenmaterial für Superkondensatoren

- Frequenzmodulation und Absorptionsverbesserung von THz-Mikrobolometern mit Mikrobrückenstruktur durch spiralförmige Antennen

- Neuer dualer mitochondrialer und CD44-Rezeptor, der auf Nanopartikel für die Redox-Stimuli-getriggerte Freisetzung abzielt

- Morphologie, Struktur und optische Eigenschaften von Halbleiterfilmen mit GeSiSn-Nanoinseln und gespannten Schichten

- Automatisierung und Cybersicherheit:Rundumschutz für Kunden

- PCB-Materialien und Design für Hochspannung