Über die Verbesserung des BFOM-Werts (BFOM) eines neuartigen GaN-Nanosäulen-Vertikalfeldeffekttransistors (FET) mit 2DEG-Kanal und Gemustertes Substrat

Zusammenfassung

Ein neuartiger vertikaler GaN-Feldeffekttransistor (FET) vom Anreicherungstyp mit 2DEG zur Reduzierung des Durchlasswiderstands (R EIN ) und ein Substratmuster (SP) zur Erhöhung der Durchbruchspannung (BV) wird in dieser Arbeit vorgeschlagen. Durch bewusste Gestaltung der Breite und Höhe des SP konnte das hochkonzentrierte elektrische Feld (E-Feld) unter der p-GaN-Kappe getrennt werden, ohne den R . dramatisch zu beeinflussen EIN , was zu einer verbesserten Figur-of-Verdienst von Baliga (BFOM, BV 2 ) führt /R EIN ). Verifiziert durch experimentell kalibrierte ATLAS-Simulation, weist das vorgeschlagene Bauelement mit einem 700 nm langen und 4,6 µm breiten SP eine sechsmal höhere BFOM im Vergleich zum FET ohne strukturiertes Substrat auf. Darüber hinaus nehmen das vorgeschlagene Säulengerät und der SP im Inneren nur einen Bereich im Nanobereich ein, was eine hochdichte Integration solcher Geräte ermöglicht, was sein hohes Potenzial in zukünftigen Leistungsanwendungen ausmacht.

Hintergrund

Heutzutage werden Halbleiter mit großer Bandlücke wie ZnO, In2 O3 , SiC und Galliumnitrid (GaN) haben Aufmerksamkeit erregt [1,2,3,4,5]. In Anbetracht der elektronischen Eigenschaften wird der laterale AlGaN/GaN-Transistor mit hoher Elektronenmobilität (HEMT) aufgrund der höheren Durchbruchspannung (BV) sowie aufgrund der höheren Durchbruchspannung (BV) weithin als potenzieller Kandidat für den Ersatz des Si-basierten Bauelements in Leistungs- oder Frequenzanwendungen angesehen die stärkere thermische Stabilität. Viele Anstrengungen, wie p-Typ-Kappe [6, 7], Fluorionenimplantation [8, 9], dünne Barriere [10, 11], Doppelkanal [5, 12] und feldgekoppeltes Gate [13] , wurden bei der Realisierung des HEMT vom Anreicherungstyp gemacht, der erwünscht ist, um die Treiberschaltung zu vereinfachen.

Diese Technologien stehen jedoch vielen gewaltigen Herausforderungen gegenüber, wie z. B. einer geringen Gleichmäßigkeit der Schwellenspannung, der Verschwendung von vertikaler Chipfläche, Stromeinbrüchen, begrenzten Baligas Figure-Of-Merits (BFOM) und so weiter. Insbesondere der Widerspruch zwischen Driftlänge und BV beeinflusst die Verkleinerung des Geräts negativ [14, 15]. Mit anderen Worten führt ein kleineres Gerät zu einer niedrigeren BV, bei der es schwieriger ist, die Anschlussklemmen zu verwenden, die die BFOM durch Optimierung der elektrischen Feldverteilung fördern. Zu diesem Zweck wurden eine rückwärtige Barriere [16], ein vergrabener Übergang [17], eine Quantentopf-Feldplatte [18] und andere Strukturen, die in den lateralen HEMT eingefügt werden und das Merkmal der elektrischen Feldplatte aufweisen, vorgeschlagen, um BV durch Verwendung von . zu verbessern der vertikale Bereich des Chips.

Auf der anderen Seite zieht der vertikale GaN-Feldeffekttransistor (VFET) aufgrund der überlegenen Eigenschaften von GaN aufgrund der einfacheren Realisierung der Funktionalität vom Anreicherungstyp und der vollen Ausnutzung des vertikalen Bereichs immer mehr Aufmerksamkeit auf sich [19 ,20,21,22]. Viele neuartige Strukturen werden durch Experimente oder Simulationen präsentiert, um die BV zu neigen und gleichzeitig den Durchlasswiderstand (R EIN ) [23,24,25]. Ganz zu schweigen von den Schwierigkeiten bei der Herstellung des Super-Junction (SJ) in GaN führt das Fehlen des hochbeweglichen zweidimensionalen Elektronengases (2DEG) zu einem höheren R EIN [26], was die Optimierung von BFOM in solchen Geräten behindert.

In dieser Arbeit wird ein neuartiger vertikaler GaN-FET im Anreicherungsmodus mit 2DEG zur Reduzierung des R EIN und ein Substratmuster (SP) zum Verbessern des BV wird vorgeschlagen, wobei die Kombination des 2DEG-Kanals und des SP den Widerspruch zwischen dem niedrigen Durchlasswiderstand und dem hohen BV effektiv ausgleicht. Darüber hinaus nehmen die vorgeschlagene Gerätesäule und der SP im Inneren nur einen Bereich im Nanobereich ein, was eine hochdichte Integration solcher Geräte ermöglicht. Verifiziert durch numerische Simulation, die in ATLAS konstruiert wurde, weist das vorgeschlagene Gerät einen höheren BFOM im Vergleich zu demselben Feldeffekttransistor (FET) ohne das strukturierte Substrat auf, was sein hohes Potenzial für zukünftige Leistungsanwendungen darstellt.

Methode

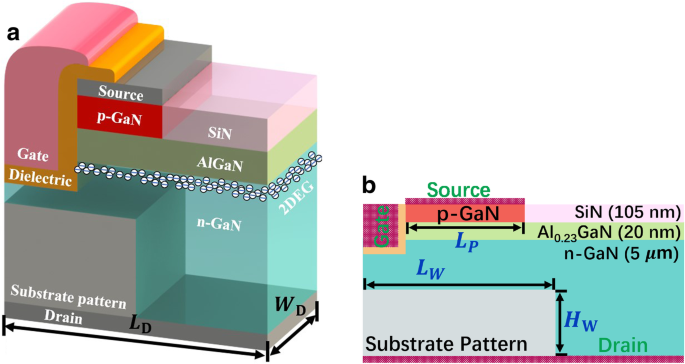

Das vorgeschlagene Gerät wird in einem normalen Al0,23 . erzeugt GaN/GaN-Wafer mit einem hochkonzentrierten n-Typ-Substrat, das als Drain-Elektrode fungiert, wie in Fig. 1a gezeigt, wobei die Dicke der Schicht Siliziumnitrid (SiN), AlGaN und GaN 105 nm, 20 nm und 5 μm beträgt , bzw. Ein n-Typ-GaN mit 2 × 10 16 cm −3 Doping n D und eine p-Typ-GaN-Kappe mit 2 × 10 17 cm −3 Doping n A wird als Puffer bzw. als zusammengesetzter Kanal eingestellt [27, 28]. Eine weitere Komponente des Kanals neben dem Gate ist eine dünne AlGaN-Schicht, die zum Induzieren von 2DEG eingeführt wird, wie in Fig. 1b gezeigt. A SP, hergestellt aus Aluminiumoxid (Al2 O3 ) zum Beispiel in diesem Papier, wird auf dem Substrat aufgewachsen.

Der Schaltplan a 3D-Säulenstruktur und b Querschnitt mit beschrifteten geometrischen Parametern des vorgeschlagenen SP-VFET

Die gesamte Vorrichtung könnte daher nacheinander durch einen Standardprozess hergestellt werden:(1) die epitaktische Abscheidung des leitfähigen Substrats und der integrierten SP-Schicht, (2) das teilweise Ätzen des SP-Musters, (3) die Abscheidung und das Polieren von n- GaN-Puffer, (4) die Abscheidung von AlGaN-Barriere und p-GaN-Kappe und (5) die Herstellung von Elektroden und Passivierung.

Der implantierte ATLAS-Simulator wird durch die experimentellen Daten eines HEMT vom Anreicherungstyp mit einer p-GaN-Kappe kalibriert [29, 30]. Die kalibrierten und anderen Spezifikationen des Geräts sind in Tabelle 1 aufgeführt. Andere Konfigurationen finden Sie in unserer früheren Arbeit [31]. Art und Dichte der Grenzflächenfalle an der SP/GaN-Grenzfläche werden auf kapazitätsbasierte experimentelle Messungen bezogen [32,33,34]. Die Polarisationsladung auf der AlGaN/GaN-Oberfläche wird gemäß der entsprechenden einfachen quadratischen Anpassungsgleichung [35] bestätigt.

Physischer Mechanismus

Im eingeschalteten Zustand weist der vorgeschlagene vertikale Feldeffekttransistor mit Substratstruktur (SP-VFET) gegenüber dem Gerät ohne 2-DEG-Kanal und SP einen hochleitfähigen Pfad aufgrund des 2-DEG und einen schmaleren vertikalen Stromkanal auf das schrumpft die Leitfähigkeit, wie in Abb. 2 gezeigt. Im Detail konnte dank des hochdichten 2DEG, das an der AlGaN/GaN-Grenzfläche konzentriert ist, der seitliche Weg des Stromflusses aufrechterhalten werden, was die gesamte Leitfähigkeit des Geräts teilweise kompensiert. Im Gegensatz dazu würde die Stromtransportfähigkeit des SP-VFET-Bauelements ohne 2DEG-Kanal dramatisch beeinflusst.

Die schematische Darstellung des Vorwärtsstromflusses in a das Gerät ohne SP, b der vorgeschlagene SP-VFET mit kurzem SP und c ein langer SP

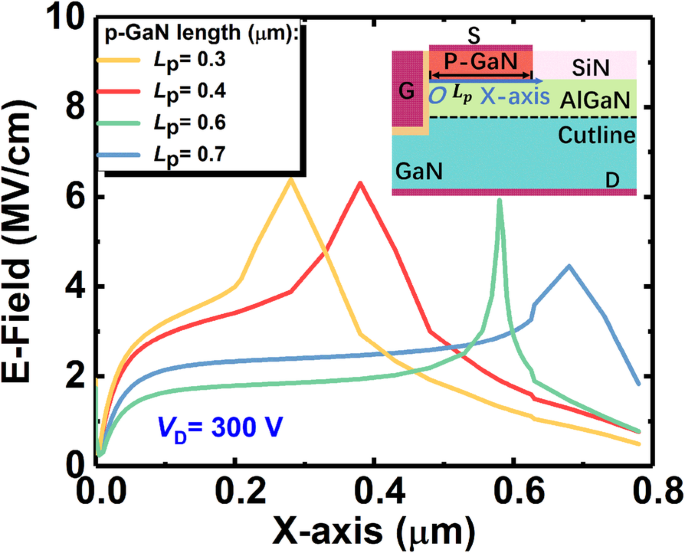

Die Länge der p-GaN-Kappe würde die Konzentration des elektrischen Felds (E-Feld) nicht dramatisch beeinflussen, bis die Länge mehr als 700 nm beträgt, wodurch das p-GaN fast die gesamte Geräteoberfläche bedeckt. Wie in Fig. 3 gezeigt, besitzt die E-Feldverteilung entlang der AlGaN/GaN-Grenzfläche einen Peak um die rechte Ecke des p-GaN. Die Position des Peaks verschiebt sich mit der variierenden p-GaN-Länge, behält jedoch die gleiche Größe bei. Ein winziger Unterschied des Spitzenwertes ist in Abb. 3 zu sehen, wenn die p-GaN-Kappe länger als 600 nm ist, da die lange p-GaN-Kappe das gesamte E-Feld im Gerät abflacht und hierdurch den Widerstand des Geräts bedingt erhöht zur Erschöpfung des 2DEG.

Die elektrische Feldverteilung des Bauelements ohne SP entlang des AlGaN/GaN-Heteroübergangs in verschiedenen p-GaN-Längen

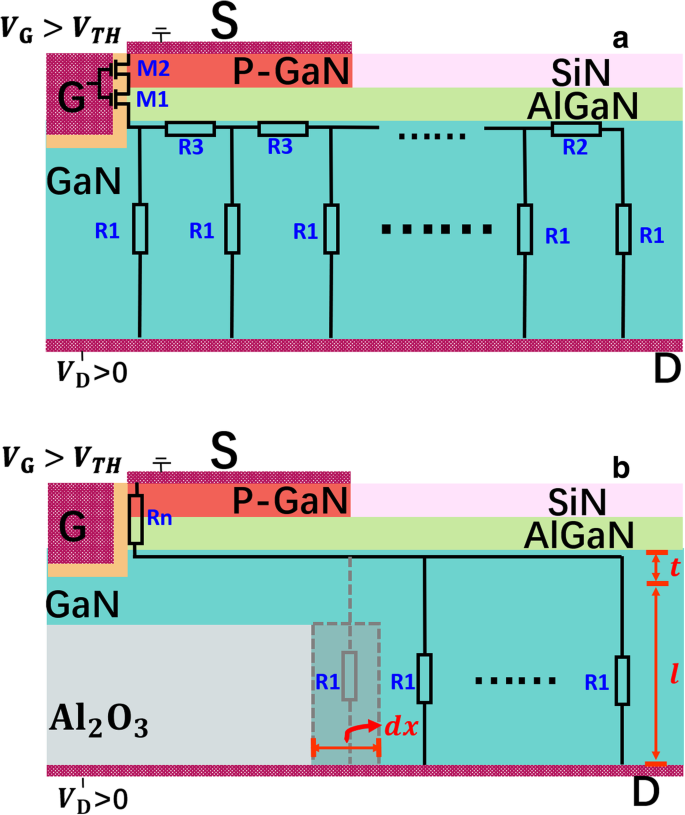

Um den Einfluss des gleichzeitig eingeführten p-GaN, 2-DEG und des SP zu veranschaulichen, kann ein Leitungsmodell im Durchlasszustand erstellt werden, wie in Fig. 4a schematisch gezeigt. M 1 und M 2 sind die MIS-ähnlichen Transistoren, deren Leitungskanal in p-GaN bzw. AlGaN gebildet ist. R 1 repräsentiert den infinitesimalen Teil des vertikalen Widerstands in Bulk-GaN. R 2 und R 3 repräsentieren die infinitesimalen Widerstandsanteile des 2-DEG-Kanals mit bzw. ohne teilweise erschöpft zu sein. Gemäß dem Widerstandsgesetz R 1 , R 2 , und R 3 erhältlich als

$$ {R}_1=\frac{1}{n_1 q\mu}\bullet \frac{l}{dx\bullet {W}_D} $$$$ {R}_2=\frac{1}{n_2 q\mu}\bullet \frac{dx}{t\bullet {W}_D} $$$$ {R}_3=\frac{1}{n_3 q\mu}\bullet \frac{dx}{t\ Aufzählungszeichen {W}_D} $$wo n 1 , n 2 , und n 3 repräsentieren die elektrische Konzentration in GaN, nicht-abgereichertem 2-DEG bzw. abgereichertem 2-DEG; q ist die Elektronenladung und μ ist die Mobilität des Elektrons in GaN; l ist die Länge der vertikalen Leiterbahn und dx ist die infinitesimale Länge im Horizont; W D ist die Breite des Geräts; und t ist die Dicke des 2-DEG. Der Einfachheit halber t ist auf 10 nm festgelegt [7]. Die Konzentration des abgereicherten 2-DEG unter p-GaN n 3 entspricht der nicht verarmten Konzentration n 1 minus der gesamten negativen Ladung im abgereicherten p-GaN [31], die lautet

$$ {n}_3={n}_2-{n}_A{x}_D $$

Das Schema von a vorgeschlagenes On-State-Modell ohne SP b On-State-Widerstandsnetzwerkmodell mit SP

Die p-GaN-Kappe kann als vollständig verarmt angesehen werden, also x D gleich 105 nm, der Dicke von p-GaN. Im Vergleich zu R 1 , R 2 und R 3 sind viel niedriger als R 1 , wegen ihrer höheren Elektronenkonzentration und kürzeren Leiterbahn. Daher kann der Widerstand im 2-DEG-Kanal ignoriert werden. Wenn die Drainspannung klein ist und die MIS-ähnlichen Transistoren M 1 und M 2 Arbeit im ungesättigten Modell, der Durchlasswiderstand von M 1 und M 2 kann als vernachlässigbarer konstanter Widerstand angesehen werden R n . Um die Berechnung zu vereinfachen, die analytische Form des vertikalen Strompfadleitwerts G v des vertikalen Strompfades erhalten Sie als

$$ {G}_v={\int}_0^{L_D}\frac{1}{R_1}={\int}_0^{L_D}{n}_1 q\mu\bullet \frac{dx\bullet { W}_D}{l} $$wo L D ist die Länge des Geräts.

Daher ist der Durchlasswiderstand R an erhalten werden, die lautet

$$ {R}_{on}=\frac{1}{G_v}+{R}_n=\frac{1}{n_1 q\mu}\bullet \frac{l}{L_D\bullet {W}_D }+{R}_n $$Wenn SP vorhanden ist, wie in Fig. 4b gezeigt, wurde der vertikale leitfähige Pfad teilweise blockiert. Somit kann der Leitwert des vertikalen Strompfads ausgedrückt werden als

$$ {G}_v={\int}_{L_W}^{L_{\mathrm{D}}}\frac{1}{R_1}={\int}_{L_W}^{L_D}{n} _1 q\mu\bullet \frac{dx\bullet {W}_D}{l} $$wo L W ist die Länge des SP.

Daher ist das entsprechende R an kann ausgedrückt werden als

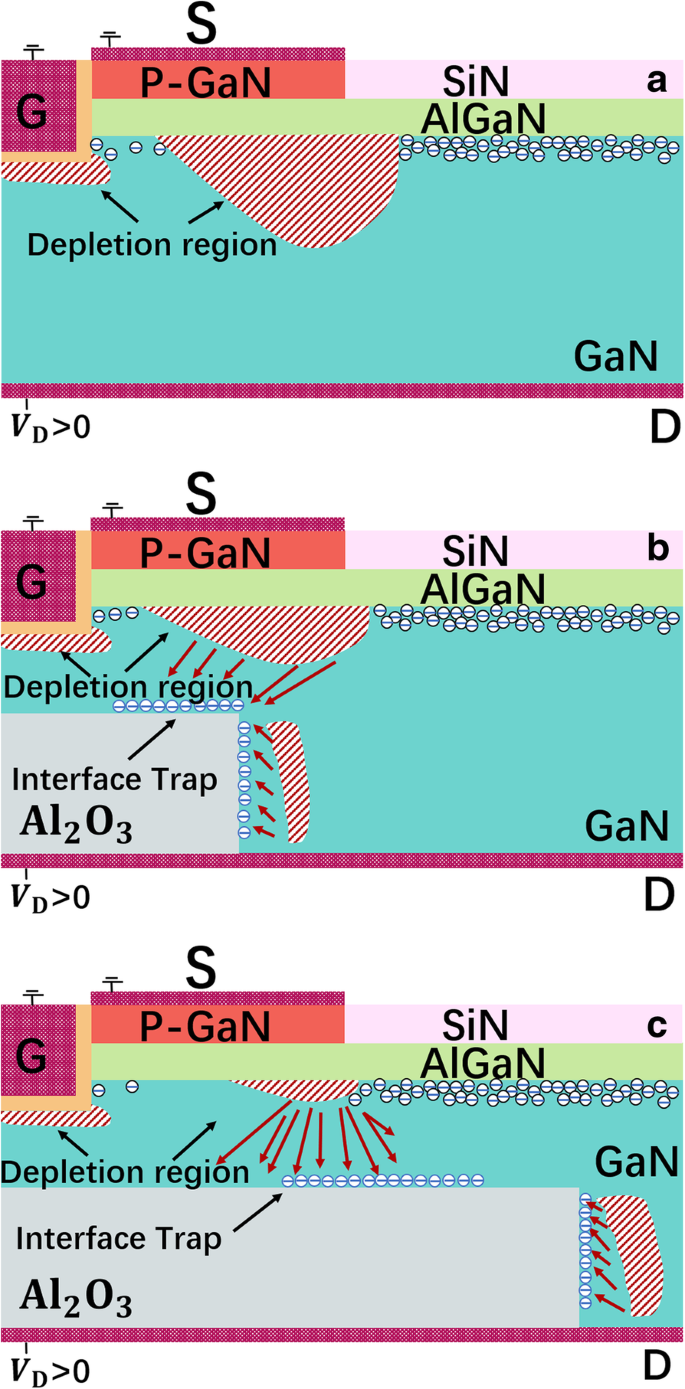

$$ {R}_{on}=\frac{1}{G_v}+{R}_n=\frac{1}{n_1 q\mu}\bullet \frac{l}{\left({L}_D -{L}_W\right)\bullet {W}_D}+{R}_n $$Im ausgeschalteten Zustand würde der SP aufgrund der kondensatorähnlichen Funktionalität und der negativ geladenen Grenzflächenfalle das elektrische Feld unter der p-GaN-Kappe effektiv neu verteilen, wodurch eine Feldkonzentration um den SP herum entsteht, die eine breitere Bandlücke besitzt, wie in gezeigt Abb. 5. Eine solche E-Feld-Umverteilung schrumpft den Verarmungsbereich, der um p-GaN und das Gate herum erscheint, und verringert dadurch die hohe Feldkonzentration um die p-GaN-Kappe und das Gate herum, was die BV des SP-VFET erhöhen würde bemerkenswert. Andererseits würde der SP, wie oben erwähnt, die Leitfähigkeit der Vorrichtung derart beeinflussen, dass die durch den SP eingebrachte negative Ladung zu einem Anstieg der potentiellen Energie in der Nähe des Gates führt, was die Abnahme von 2-DEG in der Nähe des Gates erklärt. Als Ergebnis würde ein schwankender BFOM durch Variieren der Länge und Höhe des SP erreicht.

Die schematische Verteilung des elektrischen Felds und der Verarmungsregion in a das Gerät ohne SP, b der vorgeschlagene SP-VFET mit kurzem SP und c der vorgeschlagene SP-VFET mit einem langen SP

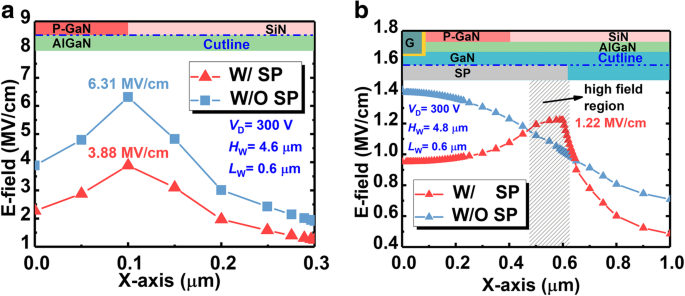

Mit anderen Worten, der SP könnte die Spitze des E-Felds um die p-GaN-Ecke reduzieren und gleichzeitig das E-Feld anziehen, das sich über den SP konzentriert, wie in Fig. 6a, b gezeigt. Dank des höheren kritischen E-Felds des SP würde eine solche E-Feld-Konzentration jedoch das Bauelement nicht zerstören, wodurch der SP-VFET eine viel höhere BV aufweisen würde.

Die elektrische Feldverteilung des vorgeschlagenen SP-VFET entlang der Grenzfläche von a p-GaN/AlGaN und b GaN/SP

Ergebnis und Diskussion

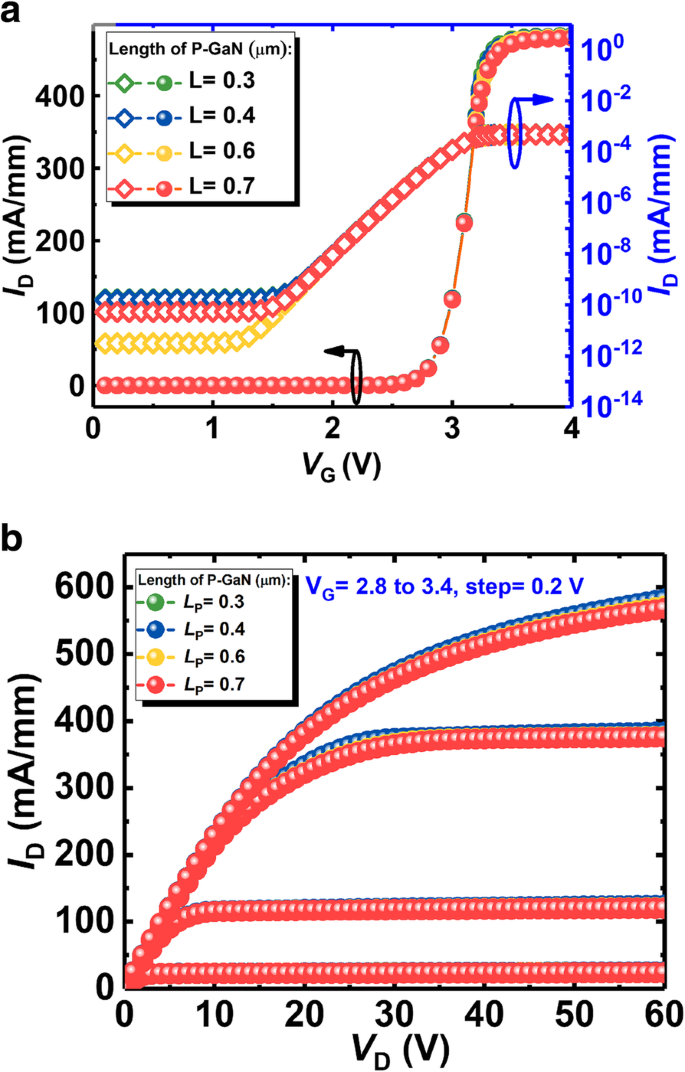

Abbildung 7a, b zeigen jeweils die Übertragungs- und Ausgangskurven des vorgeschlagenen Geräts ohne SP. Bei unterschiedlicher Länge der p-GaN-Kappe überlagern sich diese Kurven sowohl im Unterschwellen- als auch im Einschaltbereich, was darauf hindeutet, dass die Länge der p-GaN-Kappe die Leitfähigkeit des Geräts ohne SP nicht beeinflusst. Mit anderen Worten, obwohl die p-GaN-Kappe das 2-DEG teilweise abbauen und hierdurch den Widerstand des 2-DEG-Kanals beeinträchtigen würde, besitzt das verbleibende 2-DEG immer noch eine hohe Konzentration n 3 das entspricht ungefähr der nicht abgereicherten Konzentration n 2 , die durch Optimierung der p-Typ-Konzentration in der p-GaN-Kappe realisiert wird. Darüber hinaus ist, wie zuvor analysiert, der Widerstand des 2-DEG-Kanals im Vergleich zum Widerstand des n-GaN im vertikalen Pfad ziemlich klein. Daher überlagern sich die Übertragungskurven in Fig. 7a, b. Um das Gate jedoch vor dem hochkonzentrierten E-Feld zu schützen, sollte eine solche Verdrängung nicht neben dem Gate liegen, was bedeutet, dass die Länge des p-GaN nicht zu kurz sein darf. Daher beträgt die Mindestlänge des p-GaN in unserer Arbeit 400 nm, sofern nicht anders angegeben.

a Die Übertragungskurven und b Ausgangskurven des Gerätes ohne SP in unterschiedlicher Länge der p-GaN-Kappe

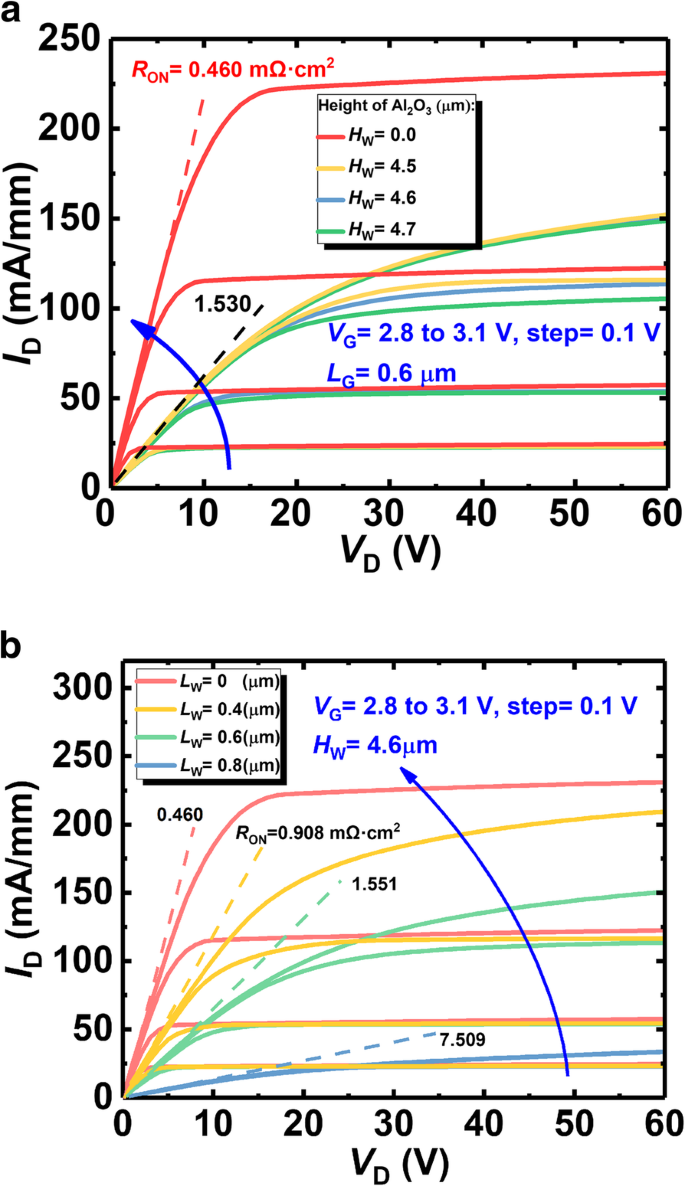

Abbildung 8 zeigt die Ausgangseigenschaften des vorgeschlagenen SP-VFET und des VFET ohne SP. Es ist ersichtlich, dass der SP den Gerätewiderstand durch Verengung des vertikalen Leitungskanals auferlegt. Im Detail ist der Durchlasswiderstand unabhängig von der Höhe des SP, wenn die Höhe unter 4,7 μm liegt, während er erheblich von der Länge des SP abhängt, die dem Mechanismus entspricht, mit dem ein schmaler vertikaler Strompfad den Leitwert schrumpft. Die erstere Unabhängigkeit liegt daran, dass das 2DEG der wichtigste seitliche Leitungskanal ist, der innerhalb seiner moderaten Höhe nicht durch den SP geschwächt würde. Wenn der SP jedoch an den 2-DEG-Kanal angrenzt, wird die eingeführte negative Ladung um den SP herum das Energieband nivellieren, was zu einer dramatischen Abnahme der 2-DEG-Konzentration führt. Folglich steigt der Widerstand des 2-DEG und der gesamte Durchlasswiderstand R an erhöht sich entsprechend. Außerdem kommt die spätere Abhängigkeit von dem bemerkenswert erhöhten Widerstand im vertikalen Kanal, wie bereits erwähnt. Darüber hinaus sollte beachtet werden, dass die durch hohe SP induzierten Gitterdefekte in 2-DEG die Höhe von SP begrenzen.

Die Ausgangskurven des vorgeschlagenen SP-VFET mit variierenden a SP-Breite und b SP-Länge im Vergleich zum Gerät ohne SP

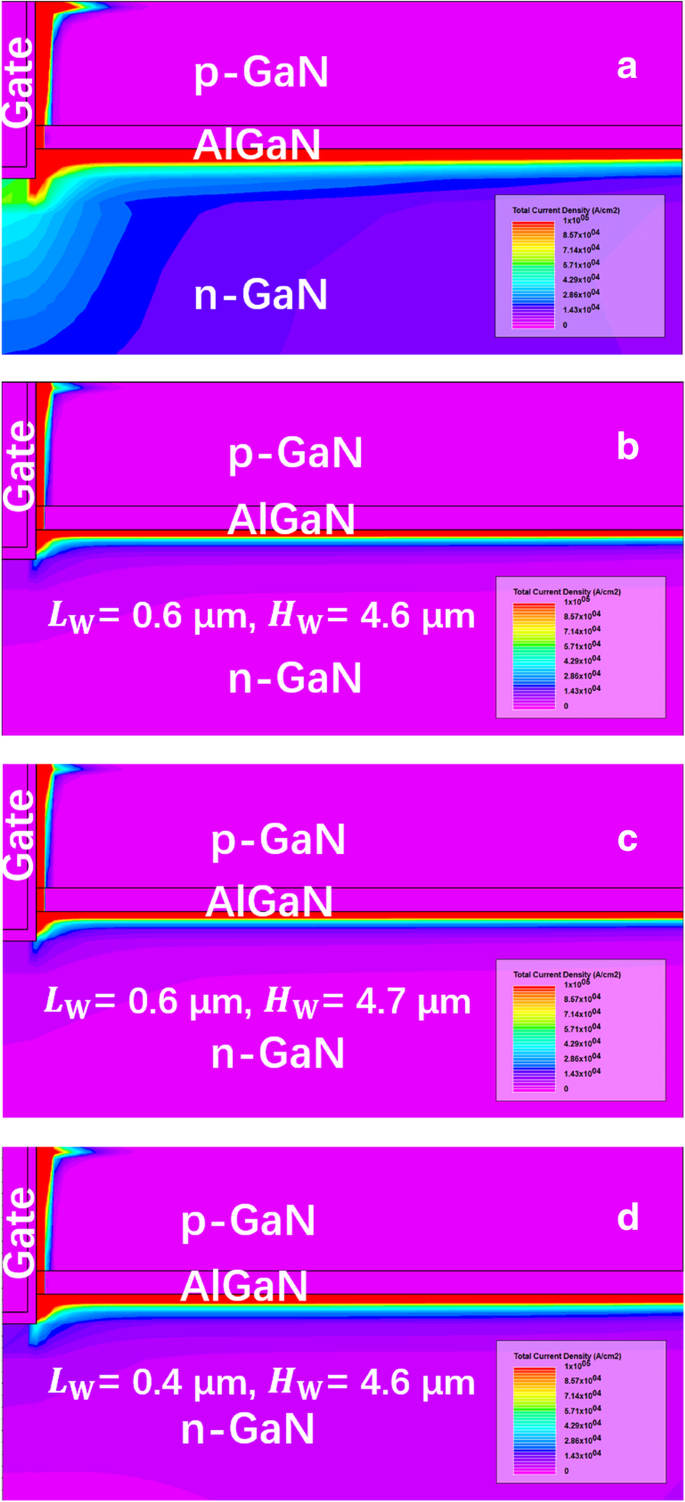

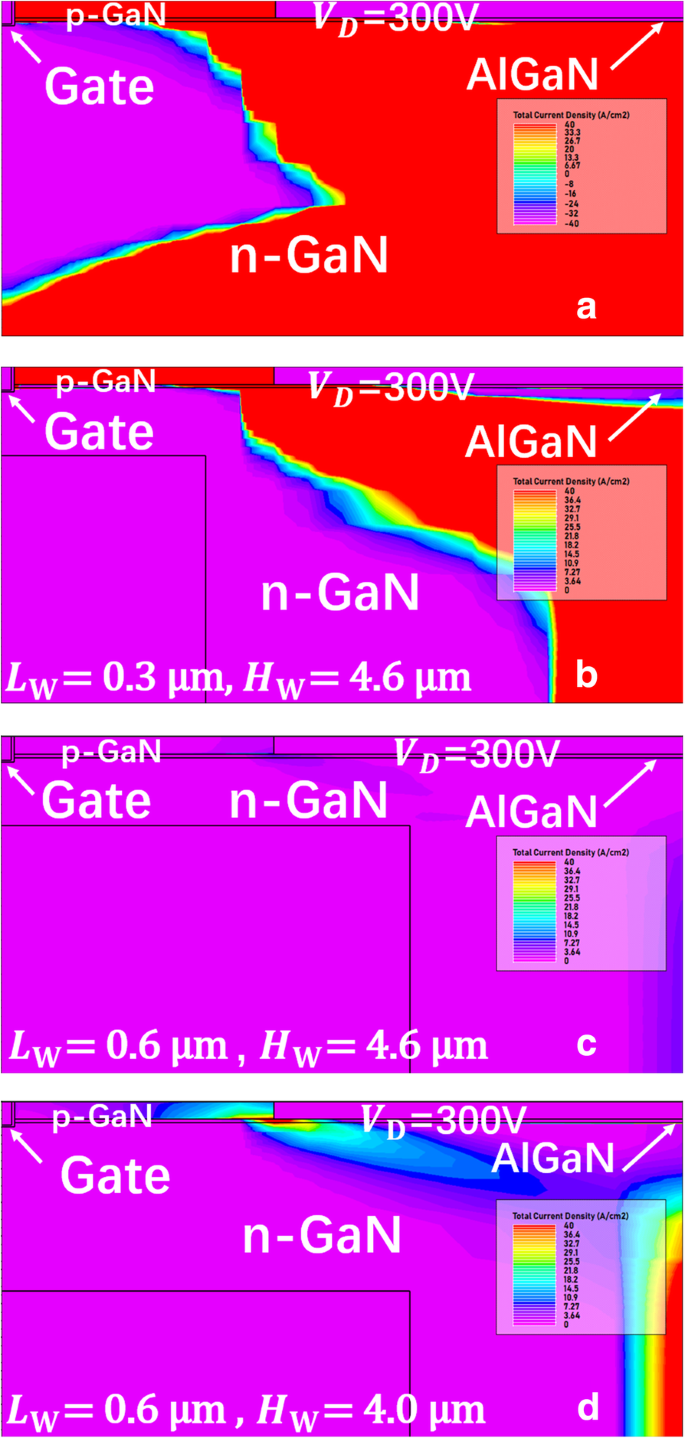

Figur 9 zeigt die Details der Stromdichteverteilung um das Gate der VFET-Bauelemente mit oder ohne SP, wobei der VFET ohne SP eine höhere Stromtransportfähigkeit aufweist, die mit Figur 8a übereinstimmt. Im Gegensatz dazu verringert der SP-VFET die Stromleitung, indem er den vertikalen Kanal verengt. Inzwischen verdeutlichen die detaillierten Abbildungen deutlich, dass der Strom im seitlichen Kanal vom 2DEG transportiert wird und sich die Gesamtstromdichte mit wachsender SP-Höhe leicht ändert, was auch im Mechanismusabschnitt demonstriert wird. Die Ergebnisse zeigen, dass der seitliche Kanalwiderstand nicht merklich durch den SP innerhalb einer moderaten Höhe auferlegt wird.

Die Stromdichte von a das Gerät ohne SP und b –d der vorgeschlagene SP-VFET mit unterschiedlichen geometrischen SP-Parametern

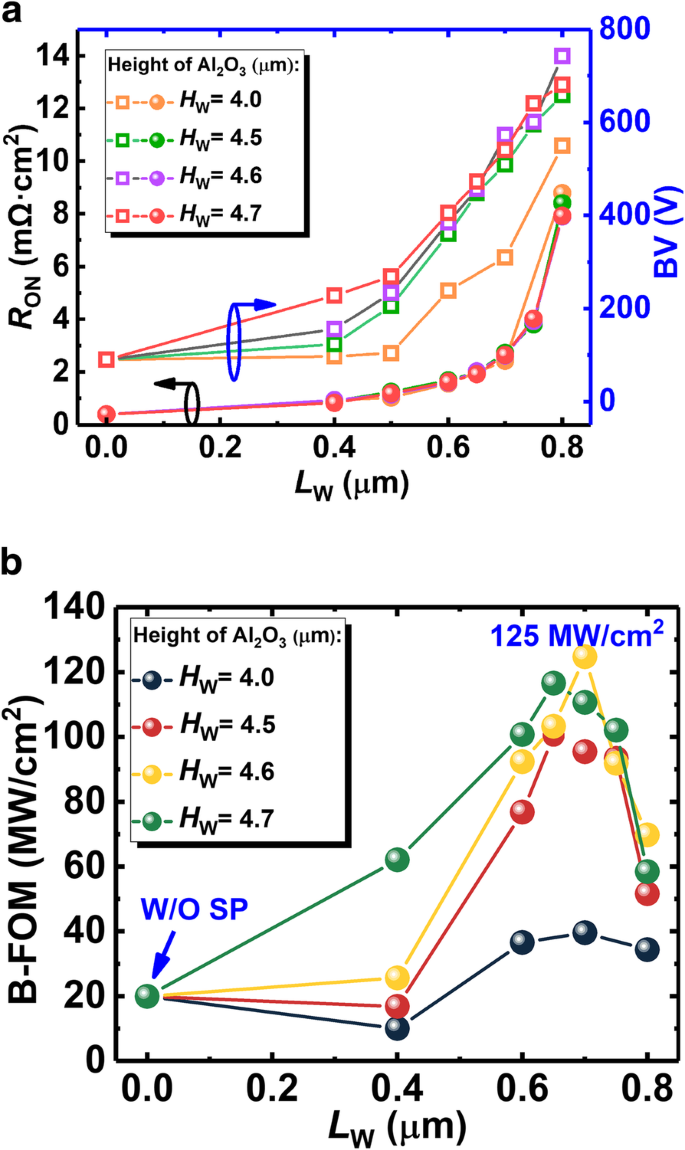

Abbildung 10a zeigt den extrahierten Durchlasswiderstand und den entsprechenden BV. Der Widerstand des SP-VFET steigt mit längerem SP. Und insbesondere zeigt die Kurve des Widerstands gegenüber der SP-Länge einen hyperbolischen Trend, und die Steigung der Kurve nimmt mit der längeren SP-Länge zu. Wie zuvor analysiert, R an variiert mit unterschiedlicher SP-Länge L W in Form einer hyperbolischen Funktion, die dem Simulationsergebnis entspricht. Darüber hinaus überlagert sich die Widerstandskurve mit unterschiedlichen SP-Höhen, da die Höhe weniger als 4,7 μm beträgt, was darauf hindeutet, dass der 2-DEG-Kanal der seitliche Hauptleitpfad ist und der 2-DEG-Kanal, wie oben erwähnt, nicht beeinflusst wird.

a Der extrahierte Durchlasswiderstand sowie BV und b die entsprechende BFOM des vorgeschlagenen SP-VFET in unterschiedlicher SP-Länge und -Breite

Abbildung 10b zeigt den berechneten BFOM des SP-VFET. Aufgrund der unterschiedlichen Anstiegsrate von BV und Durchlasswiderstand wächst der BFOM aller Geräte zuerst und fällt dann nach einer Länge des SP von mehr als 400 nm ab. Ein Spitzen-BFOM von 125 MW/cm 2 wird erreicht, wenn die Länge 700 nm und die Höhe 4,6 μm erreicht. Verglichen mit dem Gerät ohne SP schneidet der vorgeschlagene SP-VFET in Bezug auf das BFOM mehr als sechsmal besser ab.

Diese Verbesserung wird durch die Unterdrückung des hohen E-Felds unter dem p-GaN dank der negativ geladenen Grenzflächenfalle um den SP erreicht. Die Wechselwirkung, die zwischen der eingefangenen negativen Ladung an der Grenzfläche des SP und der Verarmungsregion um das p-GaN auftritt, bildet eine neue Verteilung des E-Felds hauptsächlich in Richtung der eingefangenen Ladung. Nach dem Gaußschen Gesetz wird der elektrische Fluss durch die eingeschlossene Ladung begrenzt. Somit beeinflusst das eingeführte E-Feld den elektrischen Fluss an anderer Stelle. Da die negative Ladung der Verarmungsregion die Hauptquelle für das gedrängte E-Feld um p-GaN ist, spielt das durch die eingefangene Ladung eingeführte E-Feld eine Rolle bei der Unterdrückung des um p-GaN gedrängten E-Felds, und folglich BV wird verbessert. Insbesondere wenn die SP-Länge weniger als 400 nm beträgt, ist die durch SP eingeführte negative Ladung weit von der Verarmungsregion entfernt. Somit ist das zwischen dem Verarmungsbereich und der eingefangenen negativen Ladung gebildete E-Feld zu klein, um eine Rolle bei der Beeinflussung des gedrängten E-Felds unter p-GaN zu spielen. Dadurch wächst der BV des Geräts leicht. Da die SP-Länge jedoch höher als 400 nm ist, ist das E-Feld zwischen der Verarmungszone und der eingefangenen negativen Ladung aufgrund der stärker eingefangenen negativen Ladung an der Grenzfläche des SP und des kürzeren Abstands zwischen der Verarmungsregion und der eingefangenen negativen Ladung verbessert, was zum Wachstum der BV führt.

Darüber hinaus ist die Region um das SP aufgrund der durch das SP eingeführten negativen Ladung enorm verarmt. Und wie in Fig. 11 gezeigt, verengt sich der vertikale Leckstrompfad mit dem längeren SP in der Breite aufgrund des Zusammendrückens des verarmten Bereichs zum Bauteilrand, was auch den Leckstrom blockiert und folglich die BV erhöht. Daher steigt die BV mit zunehmender SP-Länge merklich an.

Die Leckstromdichte von a das Gerät ohne SP und b –d der vorgeschlagene SP-VFET mit unterschiedlichen geometrischen SP-Parametern

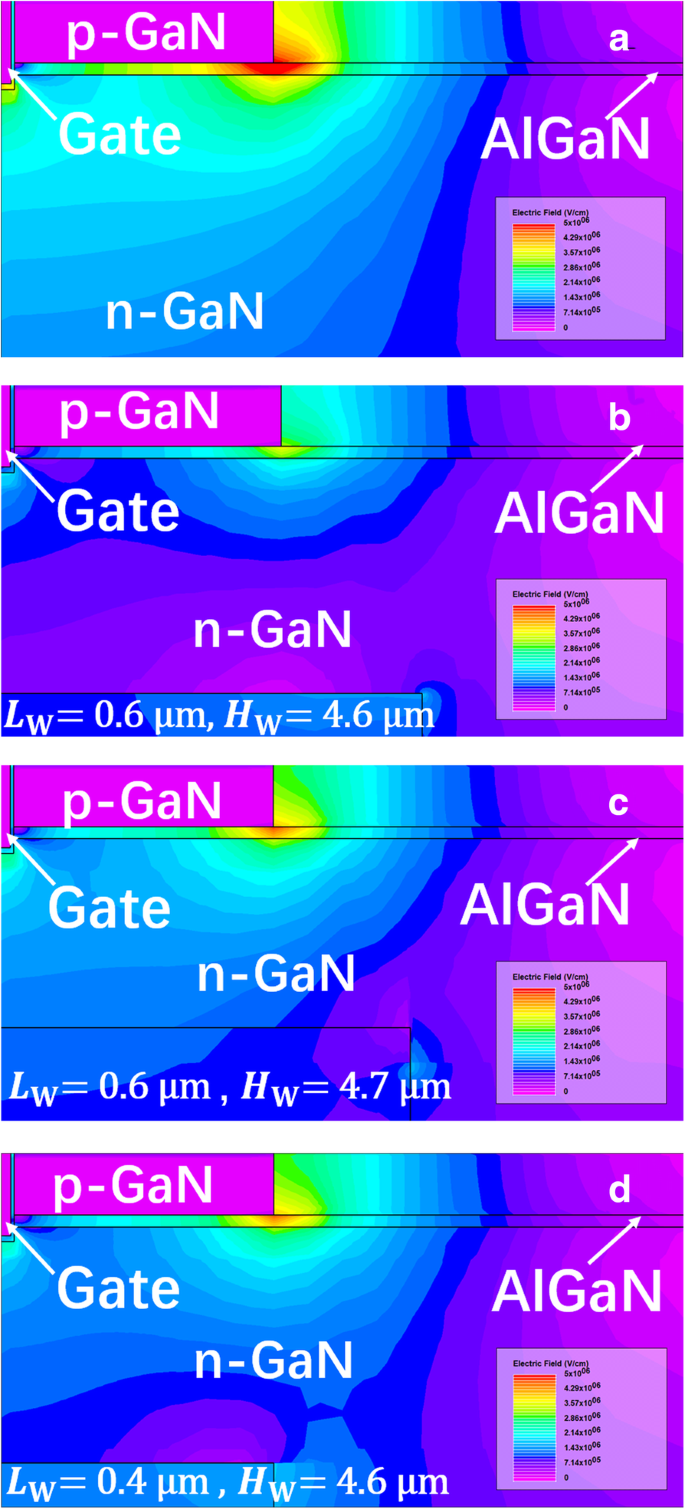

Abbildung 12 zeigt die simulierte E-Feld-Verteilung im SP-VFET bei einer Drain-Spannung von 300 V, wobei der SP anscheinend andere neue E-Feld-Konzentrationspunkte induziert, was bedeutet, dass der Spitzen-E-Feld-Bereich unter dem p-GaN unterdrückt wird . Verglichen mit der E-Feld-Verteilung in den Geräten mit unterschiedlicher SP-Höhe unterdrückt die Erhöhung der SP-Länge die Ansammlung des E-Felds und verbessert folglich die BV effizienter.

Die E-Feldverteilung um das Gate des VFET a mit oder b –d ohne SP, wenn die Drainspannung 300 V beträgt

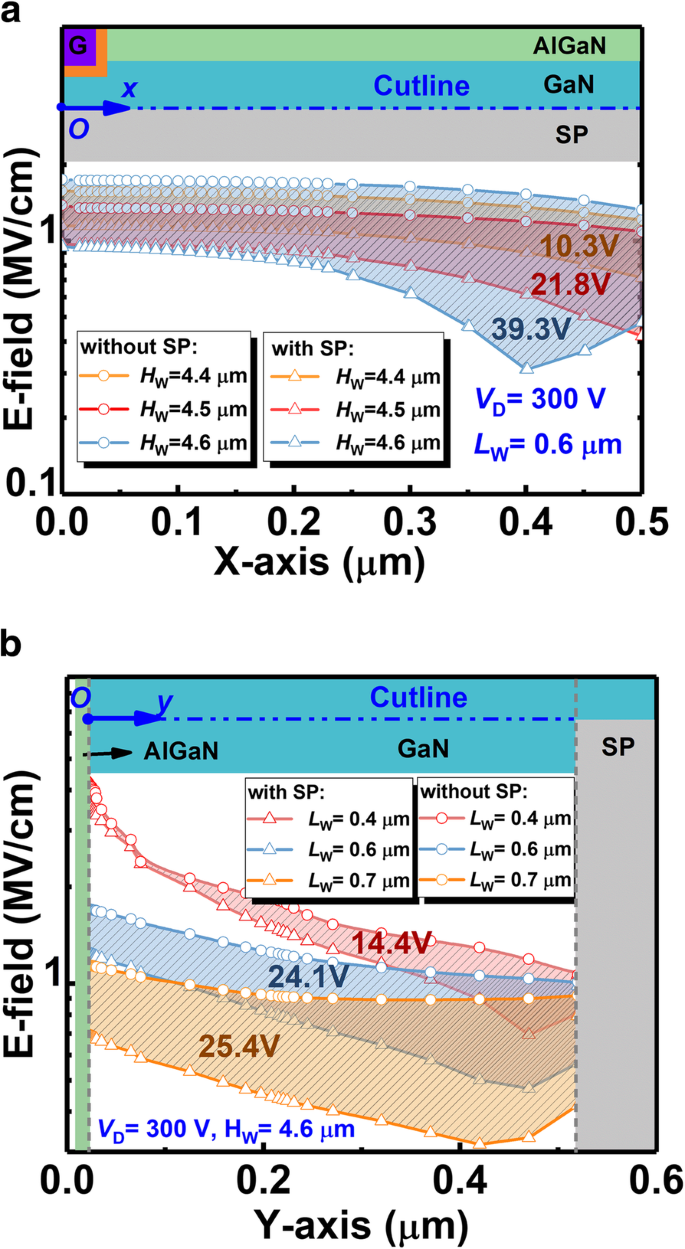

Ein solches abgeflachtes E-Feld konnte auch explizit in Abb. 13 beobachtet werden, in der die E-Feld-Verteilungen entlang der horizontalen und senkrechten Kante des SP (siehe Schnittlinie) aufgetragen sind. Wie in polychromer Abb. 12 gezeigt, ist in Abb. 13 zu sehen, dass ein höherer und längerer SP eine immer effektivere Rolle bei der Rekonstruktion des E-Felds unter p-GaN spielt und das E-Feld anzieht, um sich über den SP . zu konzentrieren Kante. Diese Umverteilung wirkt dem E-Feld um verwundbares p-GaN entgegen. Somit wird die BV des Bauelements verbessert, wodurch der B-FOM des vorgeschlagenen SP-VFET gesteigert wird.

Die E-Feld-Verteilung a horizontal und b senkrecht entlang der Schnittlinie der SP-Kante im SP-VFET extrahiert

Schlussfolgerung

In dieser Arbeit wird ein neuartiger vertikaler GaN-FET (SP-VFET) vom Anreicherungstyp mit 2DEG-Kanal- und Substratmuster zur Verbesserung seines BFOM vorgeschlagen und untersucht. Verifiziert durch experimentell kalibrierte Simulation, die mit ATLAS implementiert wurde, ist es der SP, der den E-Feld-Peak unter dem p-GaN lindert und gleichzeitig eine neue E-Feld-Konzentration über den SP anzieht, der ein höheres kritisches E-Feld besitzt. Folglich wird die BV des vorgeschlagenen SP-VFET aufgrund der 2DEG-Kompensation mit einem moderat ansteigenden Durchlasswiderstand verstärkt. Der BFOM des SP-VFET wird daher sechsmal besser als der des Geräts ohne SP, wenn die SP-Länge und -Höhe 700 nm bzw Integration.

Abkürzungen

- n A :

-

Dotierungskonzentration von p-Typ GaN

- n D :

-

Dotierungskonzentration von n-Typ GaN

- 2DEG:

-

Zweidimensionales Elektronengas

- Al0,23 GaN:

-

Aluminiumgalliumnitrid mit einem Molenbruch von 0,23 für Aluminium

- Al2 O3 :

-

Aluminiumoxid

- BFOM:

-

Baligas Persönlichkeit

- D SP :

-

Grenzflächenfallendichte des Substratmusters

- E-Feld:

-

Elektrisches Feld

- E T :

-

Der Unterschied zwischen dem Leitungsband und dem Grenzflächenfallen-Energieniveau

- FET:

-

Feldeffekttransistor

- GaN:

-

Galliumnitrid

- HEMT:

-

Transistor mit hoher Elektronenmobilität

- H G :

-

Höhe des Tors

- H W :

-

Höhe des Substratmusters

- L D :

-

Länge des Gerätes

- L G :

-

Länge des Tors

- L P :

-

Länge der p-GaN-Kappe

- L W :

-

Länge des Substratmusters

- SiN:

-

Siliziumnitrid

- SP:

-

Substratmuster

- SP-VFET:

-

Vertikaler Feldeffekttransistor mit Substratmuster

- W D :

-

Tiefe des Gerätes

- σ p :

-

Polarisationsladung

Nanomaterialien

- Unterwegs mit IoT

- Einfluss von Oberflächenzuständen und Aluminium-Molekülfraktion auf das Oberflächenpotential und 2DEG in AlGaN/GaN-HEMTs

- Modulation der elektronischen und optischen Anisotropieeigenschaften von ML-GaS durch vertikales elektrisches Feld

- Die Wirkung von Kontakt-Nichtgleichgewichtsplasma auf die strukturellen und magnetischen Eigenschaften von Mn Х Fe3 − X О4 Spinellen

- Auswirkung einer In-situ-Annealing-Behandlung auf die Mobilität und Morphologie von TIPS-Pentacen-basierten organischen Feldeffekttransistoren

- Kontrollierte Synthese von BaYF5:Er3+, Yb3+ mit unterschiedlicher Morphologie zur Verbesserung der Aufkonversionslumineszenz

- Lichtleitfähigkeit, pH-Empfindlichkeit, Rauschen und Kanallängeneffekte bei Si-Nanodraht-FET-Sensoren

- Grüne Synthese von Metall- und Metalloxid-Nanopartikeln und ihre Wirkung auf die einzellige Alge Chlamydomonas reinhardtii

- Einfluss von Morphologie und Kristallstruktur auf die Wärmeleitfähigkeit von Titanoxid-Nanoröhren

- Herstellung eines periodischen Polystyrol-Nanosphären-Arrays unter Verwendung der Dip-Drop-Methode mit Ätzen nach der Abscheidung und deren Anwendung zur Verbesserung der Lichtextraktionseffizienz v…