Ge-pMOSFETs mit hoher Mobilität und ZrO2-Dielektrikum:Auswirkungen des Nachglühens

Zusammenfassung

Dieses Papier untersucht die Auswirkungen von Post Metal Annealing (PMA) und Post Deposition Annealing (PDA) auf die elektrische Leistung von Ge p-Typ Metalloxid-Halbleiter-Feldeffekttransistoren (pMOSFETs) mit ZrO2 Dielektrikum. Für die Transistoren ohne PDA, Durchlassstrom (I EIN ), Subthreshold-Swing (SS) und die Eigenschaften der kapazitiven Äquivalentdicke (CET) werden verbessert, wenn die PMA-Temperatur von 350 auf 500°C ansteigt. Kristallisation von ZrO2 Dielektrikum bei der höheren PMA-Temperatur trägt zur Erhöhung der Permittivität von ZrO2 . bei und die Abnahme der Dichte der Grenzflächenzustände (D es ), was zu einer reduzierten CET und einer hohen effektiven Lochmobilität (μ eff ). Es wird gezeigt, dass Ge-pMOSFETs mit einer PDA-Behandlung bei 400°C einen niedrigeren CET und einen steileren SS, aber einen niedrigeren μ . aufweisen eff im Vergleich zu Geräten ohne PDA.

Hintergrund

Germanium (Ge) gilt als eines der attraktivsten p-Kanal-Materialien für fortschrittliche CMOS, da es eine viel höhere Lochbeweglichkeit bietet als Si [1,2,3]. Ein hochwertiges Gate-Dielektrikum und eine effektive Passivierung der Ge-Oberfläche sind der Schlüssel zur Realisierung der überlegenen effektiven Ladungsträgermobilität (μ eff ) und hoher Ansteuerstrom im Ge-Transistor [4,5,6,7]. Mehrere High--Materialien wie HfO2 [8], ZrO2 [7, 9], La2 O3 [10] und Y2 O3 [11] wurden als alternative Gate-Dielektrika für Ge-p-Typ-Metall-Oxid-Halbleiter-Feldeffekttransistoren (pMOSFETs) untersucht, um eine Skalierbarkeit der kapazitätsäquivalenten Dicke (CET) auf unter 1 nm zu erreichen. Darunter ZrO2 Dielektrikum hat aufgrund des viel höheren κ-Wertes [12, 13] und der besseren Grenzflächenqualität [14] im Vergleich zu den Hf-basierten die größte Aufmerksamkeit auf sich gezogen. Es wurde allgemein berichtet, dass die Kristallisation von ZrO2 kann die elektrische Leistung von Ge-pMOSFET weiter verbessern, z. B. durch Reduzierung der CET und Erhöhung von μ eff [15, 16]. Es fehlen jedoch Studien zu den Auswirkungen von Prozessschritten für ZrO2 Kristallisation auf die Geräteleistung von Ge-Transistoren.

In diesem Beitrag untersuchen wir die Auswirkungen des Post Metal Annealing (PMA) und des Post Deposition Annealing (PDA) auf die elektrische Leistung von Ge-pMOSFETs mit ZrO2 Dielektrikum. Deutlich verbesserte μ eff und eine reduzierte CET kann in Geräten mit einer höheren PMA-Temperatur erreicht werden.

Methoden

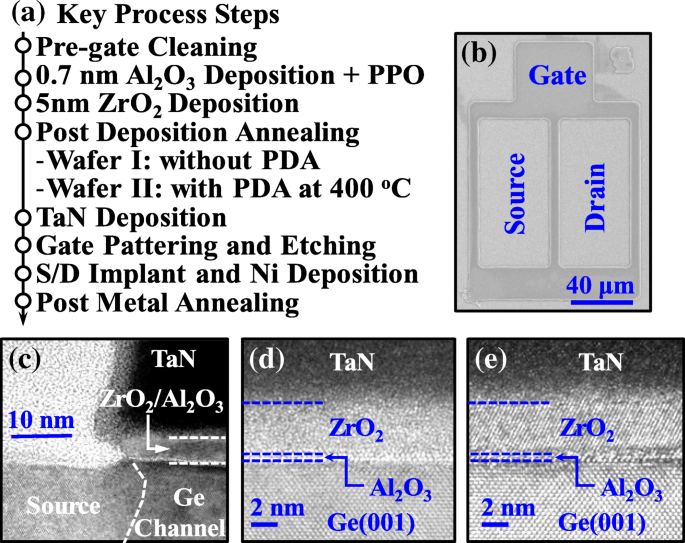

Wichtige Prozessschritte zur Herstellung von Ge-pMOSFETs mit ZrO2 Dielektrikum sind in Abb. 1a dargestellt. Die Ge-pMOSFETs wurden auf einem n-Typ Ge(001)-Wafer mit einem spezifischen Widerstand von 0,088–0,14 Ω∙cm hergestellt. Nach mehreren Zyklen chemischer Reinigung in verdünnter HF-Lösung (1:50) und Spülen in DI-Wasser. Ge-Wafer wurde in eine Atomlagenabscheidungs-(ALD)-Kammer geladen. Die Ge-Oberfläche wurde durch eine Ozon-Nachoxidation (OPO) passiviert, d. h. ein ultradünnes Al2 O3 Schicht wurde bei 300 °C abgeschieden, und dann wurde die in situ OPO bei 300 °C für 15 min durchgeführt. Danach ein 5 nm dickes ZrO2 wurde bei 250°C in derselben ALD-Kammer unter Verwendung von TDMAZr und H2 . abgeschieden O als Vorläufer von Zr bzw. O. Während der Abscheidung wird Zr[N(CH3 )2 ]4 Die Quelle wurde auf 85 °C erhitzt. Der PDA-Prozess wurde an einigen Proben bei 400 °C für 60 Sekunden unter Verwendung des schnellen thermischen Glühens durchgeführt. Proben mit und ohne PDA wurden als Wafer II bzw. I bezeichnet. Dann wurde eine 100 nm dicke TaN-Gate-Elektrode durch reaktives Sputtern abgeschieden. Nach dem Strukturieren und Ätzen des Gates wurden die Source/Drain-(S/D)-Bereiche durch BF2 . gebildet + Implantation bei einer Energie von 30 keV und einer Dosis von 1 × 10 15 cm −2 . Fünfzehn-Nanometer-Nickel-S/D-Kontakte wurden durch einen Abhebeprozess gebildet. Schließlich wurde die PMA bei 350, 400, 450 und 500°C für 30 s zur Dotierstoffaktivierung und S/D-Metallisierung durchgeführt.

a Wichtige Prozessschritte zur Herstellung von Ge-pMOSFETs mit ZrO2 Dielektrikum. b SEM-Aufnahme des hergestellten Transistors. c XTEM-Bild eines Ge-pMOSFET, das die Gate- und S/D-Regionen zeigt. d , e HRTEM-Bilder von Gate-Stapeln von Ge-pMOSFETs auf Wafer I, die bei 400°C bzw. 500°C getempert wurden

Abbildung 1b zeigt das Rasterelektronenmikroskop (REM)-Bild eines hergestellten Ge-pMOSFET. Abbildung 1c zeigt das Querschnittsbild eines Transmissionselektronenmikroskops (XTEM) eines Ge-pMOSFET, das die Source-/Drain-Region, das Metallgate und ZrO2 . zeigt Dielektrikum. Abbildung 1d und e zeigen die hochauflösenden TEM (HRTEM)-Bilder der Gate-Stapel von Ge-pMOSFETs mit einem PMA bei 400 bzw. 500°C auf Wafer I. Es wird beobachtet, dass das ZrO2 Dielektrikum war vollständig kristallisiert und wurde einer PMA bei 500°C unterzogen. Die Dicke von Al2 O3 Grenzschicht ist ungefähr 0.7 nm.

Ergebnisse und Diskussion

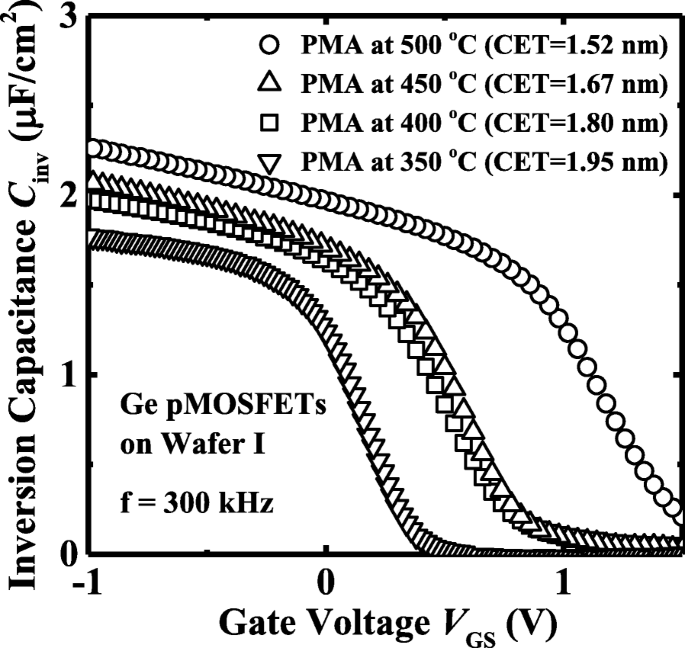

Inversionskapazität C inv vs. V GS Kurven, die bei einer Frequenz von 300 kHz für die Bauelemente auf Wafer I gemessen wurden, sind in Abb. 2 gezeigt. Die CET-Werte wurden mit ∼ 1.95, 1.80, 1.67 und 1.52 nm für die Bauelemente mit PMA bei 350, 400, 450 extrahiert. bzw. 500°C. Die kleinere CET wird aufgrund der Kristallisation von ZrO2 . bei einer höheren PMA-Temperatur erreicht . Im Allgemeinen sind die κ-Werte für amorphes und kristallines ZrO2 sind etwa 20–23 bzw. 28–30. Ein 5 nm dickes kristallines ZrO2 trägt einen EOT von ~ 0,7 nm bei. Die Verschiebung von C-V Kurven mit verschiedenen PMA-Temperaturen ist darauf zurückzuführen, dass die Kristallisation die Dichte der Bulk-Fallen in ZrO2 . verringert Dielektrikum.

Umkehrung C inv -V GS Kurven für die Ge-pMOSFETs auf Wafer I mit einem PMA bei 350°C, 400°C, 450°C und 500°C

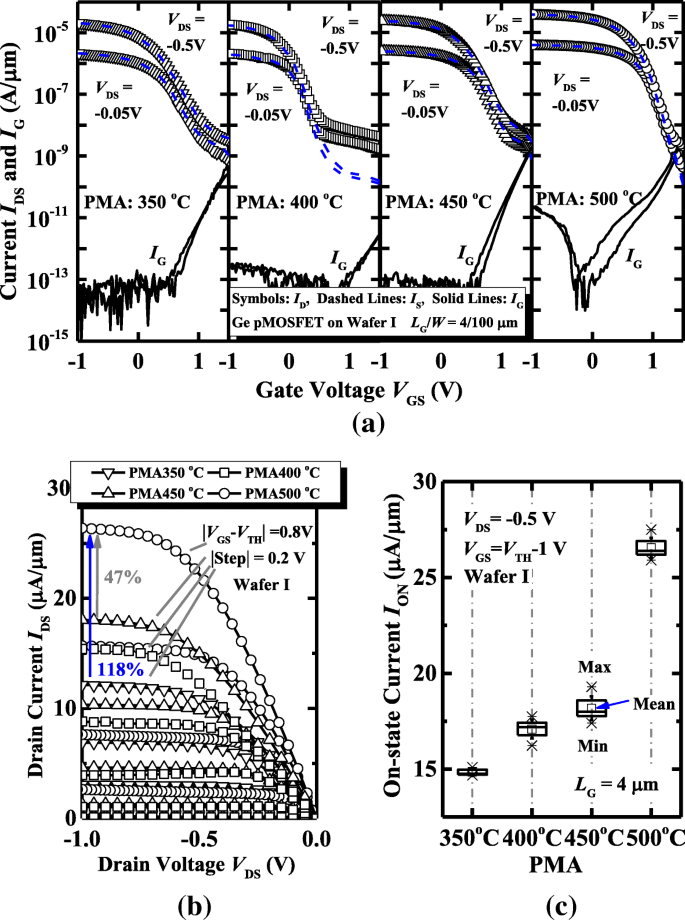

Abbildung 3a zeigt die gemessenen Übertragungseigenschaften und Gate-Leckströme I G von Ge-pMOSFETs auf Wafer I mit den unterschiedlichen PMA-Temperaturen. Alle Geräte haben eine Gate-Länge L G von 4 μm und einer Gate-Breite W von 100 µm. Ge pMOSFETs weisen das viel niedrigere I . auf G im Vergleich zu ich DS für alle PMA-Temperaturen. Ein Ich EIN /Ich AUS Verhältnis über 10 4 wird für das Gerät mit einem PMA bei 500°C erreicht. Das Ich DS -V DS Kurven der Geräte gemessen bei den verschiedenen Gate-Overdrive |V GS -V TH | sind in Abb. 3b dargestellt. Es wird darauf hingewiesen, dass die Schwellenspannung V TH ist definiert als das V GS bei ich DS von 10 −7 A/μm. Der Ge-Transistor mit einem PMA bei 500°C erzielt eine Verbesserung des Ansteuerstroms von ~ 47 % bzw. 118% im Vergleich zu den bei 450°C bzw DS von − 1.0 V und einem |V GS -V TH | von 0.8 V. Abbildung 3c zeigt den statistischen Plot des I EIN bei einem V DS von − 0.5 V und einem V GS -V TH von − 1 V für Ge-pMOSFETs mit den verschiedenen PMA-Temperaturen. Alle Transistoren in diesem Diagramm haben ein L G von 4 μm und einem W von 100 µm. Geräte mit einem PMA bei 500°C weisen ein verbessertes I . auf EIN im Vergleich zu denen mit den niedrigeren PMA-Temperaturen, was auf den verringerten S/D-Widerstand, die verringerte CET und das höhere μ . zurückgeführt wird eff , auf die später eingegangen wird.

a Gemessen I D , ich S , und ich G vs. V GS Kurven von Ge-pMOSFETs auf Wafer I mit dem PMA bei 350, 400, 450 und 500°C. b Ich DS -V DS Kurven gemessen bei den verschiedenen V GS -V TH für die Geräte. c Bei 500°C geglühtes Gerät hat einen höheren Durchlassstrom I EIN im Vergleich zu den Transistoren mit dem PMA bei den niedrigeren Temperaturen

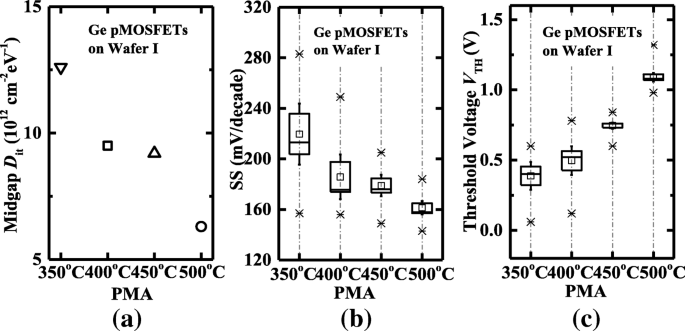

Abbildung 4 zeigt die statistischen Diagramme von Midgap D es , SS und V TH Eigenschaften für die Geräte mit den unterschiedlichen PMA-Temperaturen. Wie in Abb. 4a gezeigt, beträgt der mittlere Abstand D . basierend auf der Methode der maximalen Leitfähigkeit [17] es Werte werden zu 1,3 × 10 13 . extrahiert , 9,5 × 10 12 , 9,2 × 10 12 , und 6,3 × 10 12 cm −2 eV −1 für die Geräte mit PMA bei 350, 400, 450 bzw. 500°C. Abbildung 4b zeigt, dass bei 500°C getemperte Ge-pMOSFETs aufgrund des kleineren Midgap D . bessere SS-Eigenschaften aufweisen als die bei niedrigeren Temperaturen getemperten Transistoren es und MEZ. Die Werte von D es und SS von Ge-pMOSFETs mit PMA sind immer noch höher als die der am besten berichteten Ge-Transistoren. Es könnte möglicherweise durch Optimierung des OPO-Passivierungsmoduls reduziert werden, z. B. Al2 O3 Dicke und Ozonoxidationstemperatur und -dauer. V TH verschiebt sich zum positiven V GS mit steigender PMA-Temperatur, die auf die reduzierte CET und D . zurückzuführen ist es . Daraus wird geschlossen, dass die beste elektrische Leistung für Ge-pMOSFETs mit einem PMA bei 500°C erreicht wird.

Vergleich von a Midgap D es , b SS und c V TH für Ge-pMOSFETs auf Wafer I mit PMA bei 350, 400, 450 und 500°C

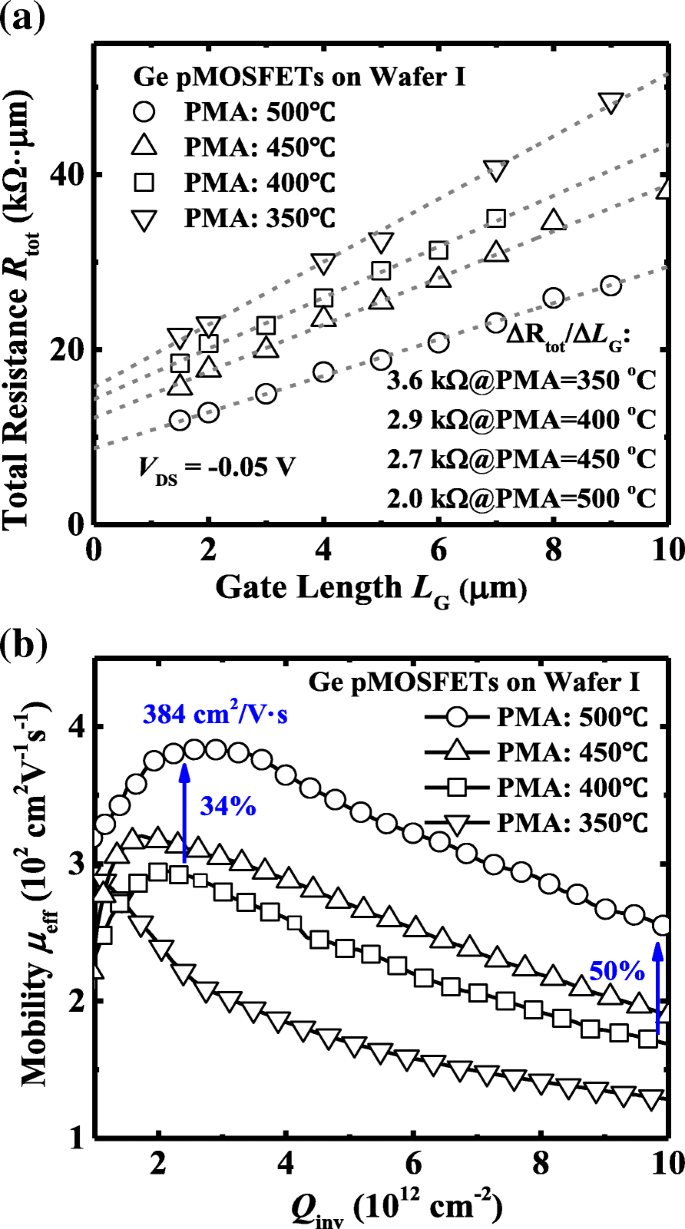

μ eff , als ein entscheidender Faktor, der den Treiberstrom und die Transkonduktanz von Ge-pMOSFETs beeinflusst, wurde mit dem ΔR . gemessen tot /ΔL G Methode [18]. Eine große Anzahl von Geräten wurde mit L . gemessen G im Bereich von 1,5 bis 9 µm. Abbildung 5a zeigt den Gesamtwiderstand R tot extrahiert bei einem |V GS -V TH | von − 1 V und einem V DS von − 0.05 V als Funktion von L G . Die R SD ist der Wert, bei dem sich die angepasste Linie am y . schneidet -Achse. Die R SD die Werte wurden auf 7,85, 7,15, 6,10 und 4,35 kΩ ·μm für Geräte mit PMA bei 350, 400, 450 bzw. 500 °C geschätzt. Dies ist ein Hinweis auf die bessere Dotierstoffaktivierung von S/D bei höherer PMA-Temperatur. μ eff kann durch μ . extrahiert werden eff = 1/[WQ inv (ΔR tot /ΔL G )], wobei Q inv ist die Inversionsladungsdichte im Ge-Kanal und ΔR tot /ΔL G ist die Steigung des R tot vs. L G wie in Abb. 5a gezeigt. Das kleinere ΔR tot /ΔL G für Geräte mit PMA bei 500°C zeigt eine Verbesserung von μ . an eff im Vergleich zu Transistoren mit PMA bei 450°C. Abbildung 5b zeigt μ eff als Funktion von Q inv Kurven, extrahiert mit dem geteilten C -V Methode. Die maximale Lochbeweglichkeit beträgt 384 cm 2 . /V ·s für Geräte mit einem PMA bei 500°C, was 31% höher ist als bei Geräten mit einem PMA bei 400°C. Bei hohem Q inv von 1 × 10 13 cm −2 , Ge-pMOSFETs, die einer PMA bei 500 °C unterzogen wurden, erzielen eine Mobilitätsverbesserung im Vergleich zu den bei 400 °C getemperten Bauelementen. Ge-Transistoren mit kristallinem ZrO2 haben die geringere Dichte der Massenfallenladung, was zu einer geringeren entfernten Coulomb-Streuung von Löchern im Vergleich zu den Geräten mit amorphem ZrO2 . führt . Aufgrund der glatten Grenzfläche zwischen kristallinem ZrO2 und Ge, Ge-Vorrichtungen, die bei 500°C getempert wurden, haben eine geringere Streuung der Oberflächenrauheit und zeigen eine Verschiebung der Spitzenmobilität zu einem höheren Q inv .

a R tot als Funktion von L G bei einem V GS -V TH von − 1 V und einem V DS von − 0.05 V für Bauelemente auf Wafer I mit verschiedenen PMA-Temperaturen. b μ eff vs. Q inv extrahiert durch den Split C -V Methode. Die höchste Mobilität wird bei Geräten mit einem PMA bei 500°C erreicht

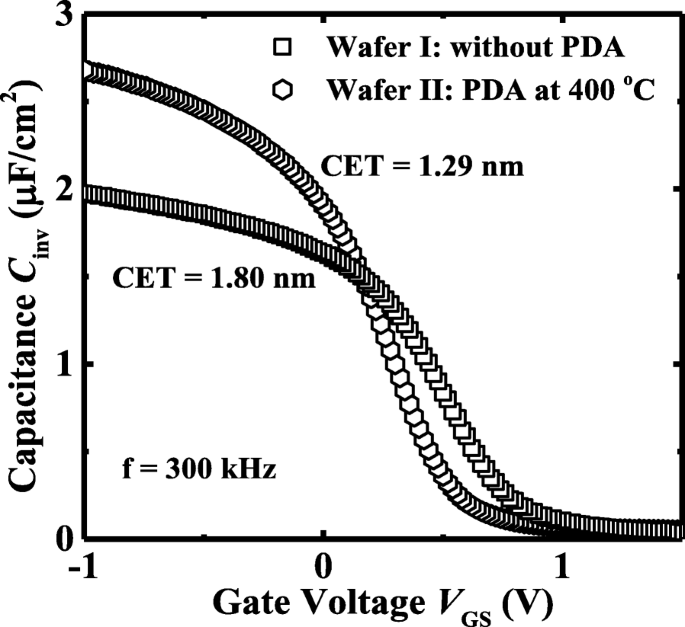

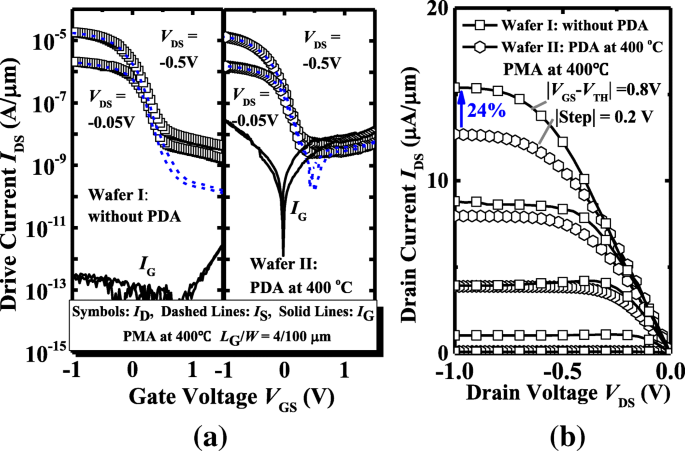

Als nächstes diskutieren wir die Auswirkungen von PDA auf die elektrischen Eigenschaften von Ge-pMOSFETs. Abbildung 6 zeigt das gemessene C inv vs. V GS der Ge-pMOSFETs auf Wafer I und Wafer II mit einem PMA bei 400 °C. Das Gerät, das einem PDA bei 400 °C unterzogen wurde, hat einen viel niedrigeren CET-Wert von 1,29 nm im Vergleich zum Gerät ohne PDA von 1,80 nm. Abbildung 7a zeigt das I D , ich S , und ich G -V GS charakteristische Kurven von Ge-pMOSFETs auf Wafer I und Wafer II und die Vorrichtungen, die einer PMA bei 400 °C unterzogen wurden. Für das Bauelement mit PDA wird im Vergleich zu dem Transistor ohne PDA ein größerer Gate-Leckstrom erhalten, was auf die niedrigere CET zurückzuführen ist. Das entsprechende Ich DS -V DS Kurven der Geräte gemessen bei verschiedenen Gate-Overdrive V GS -V TH sind in Fig. 7b gezeigt. Der Ge-Transistor ohne PDA zeigt eine Verbesserung des Ansteuerstroms von ~~24% gegenüber dem mit PDA bei 400 °C bei der gleichen Übersteuerung von - 0,8 V im Sättigungsbereich.

C inv -V GS Plots für die Bauelemente auf Wafer I und II mit einer PMA bei 400°C

a Ich D , ich S , und ich G vs. V GS Kurven von Ge-pMOSFETs auf Wafer I und II mit PMA bei 400 °C. b Ich DS -V DS Kurven gemessen bei verschiedenen V GS -V TH für die Geräte

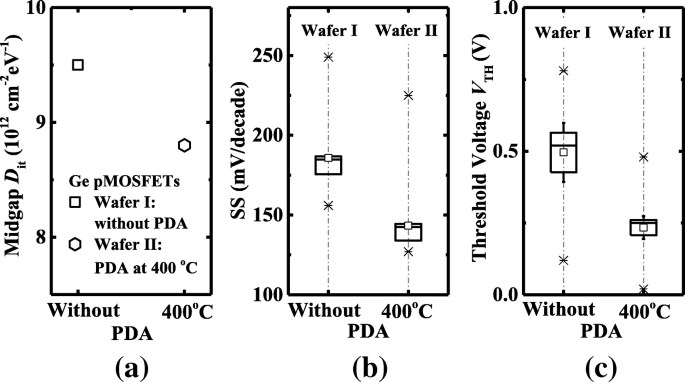

Abbildung 8 zeigt die statistischen Ergebnisse von Midgap D es , SS und V TH der Ge-pMOSFETs mit und ohne PDA. Abbildung 8a zeigt, dass das kleinere D es wird in Ge-pMOSFETs mit PDA bei 400 °C im Vergleich zu Geräten ohne PDA erreicht. In Abb. 8b wird für Geräte mit PDA bei 400°C der niedrigere Wert des mittleren unterschwelligen Swings von 142 mV/Dekade erreicht, entsprechend der niedrigeren CET und dem niedrigeren D es . Es zeigt an, dass Geräte mit PDA bei 400°C ein überlegenes ZrO2 . aufweisen /Ge-Schnittstelle. Abbildung 8c zeigt, dass Geräte mit und ohne PDA ein unterschiedliches V . haben TH; es kann der Fallendichte in der unteren Bandlückenhälfte zugeschrieben werden, die im V . dominant ist TH .

Vergleich von a Midgap D es , b SS und c V TH für Ge-pMOSFETs auf Wafer I und II mit PMA bei 400°C

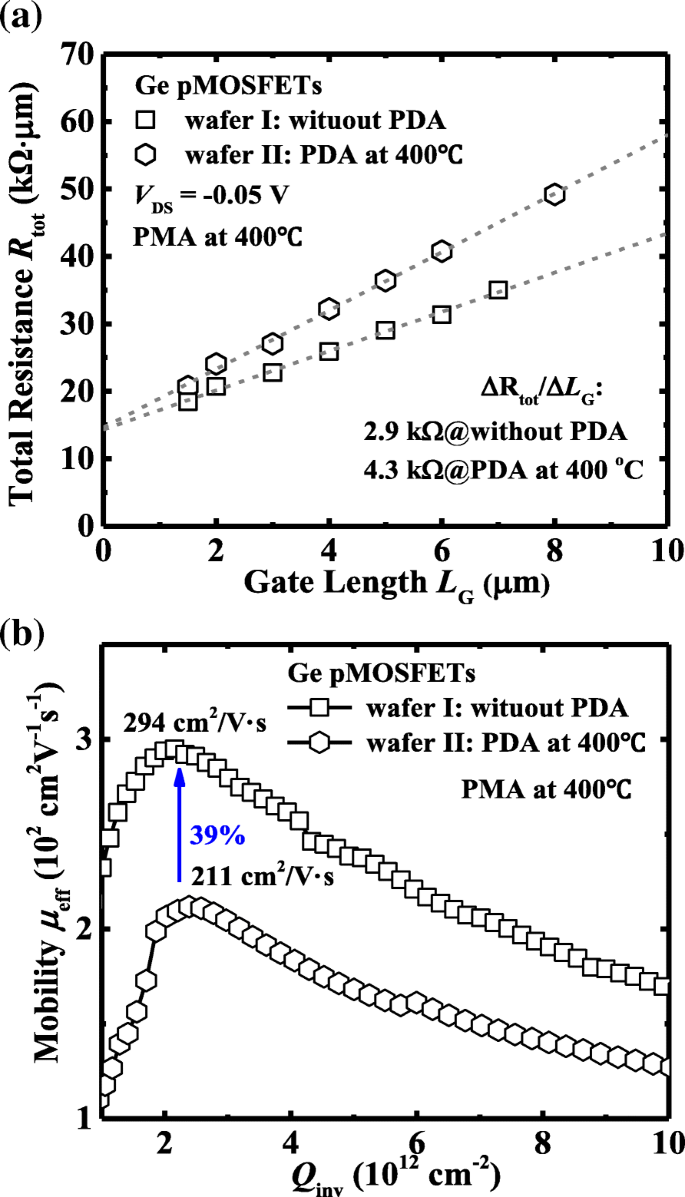

Abbildung 9a zeigt die R tot vs. L G Kurven bei einem Gate Overdrive von − 1 V und V DS von − 0,05 V für Geräte mit einem PMA bei 400 °C. Die R SD die Werte werden für Geräte ohne und mit PDA bei 400°C auf etwa 7,15 bzw. 7,30 kΩ·μm geschätzt. Wie in Abb. 9b gezeigt, ist ein bemerkenswert höherer Peak μ eff wird für Ge pMOSFETs ohne PDA erreicht, entsprechend dem kleineren ΔR tot /ΔL G in Abb. 9a im Vergleich zu Geräten mit PDA. Die Geräte mit einem PDA bei 400°C zeigen einen Peak von μ eff von 211 cm 2 /V·s; die geringere Lochbeweglichkeit könnte hauptsächlich auf die starke Coulomb-Streuung aus der Ferne zurückgeführt werden, die durch die feste Ladung in ZrO2 . beigesteuert wird Dielektrikum.

a R tot vs. L G Kurven für Vorrichtungen auf Wafer I und Wafer II mit PMA bei 400 °C. b Lochbeweglichkeit μ eff vs. Q inv für Geräte mit und ohne PDA

Schlussfolgerungen

Zusammenfassend sind die Auswirkungen von PMA und PDA auf Ge-pMOSFET mit ZrO2 Dielektrikum wurde ausführlich untersucht. Kristallisation von ZrO2 Gate-Dielektrikum sorgt im Vergleich zu Bauelementen bei der niedrigeren PMA-Temperatur für eine deutlich verbesserte Lochmobilität und eine reduzierte CET. Eine maximale Lochbeweglichkeit von 384 cm 2 /V·s und verbesserter Treiberstrom wurden in Geräten mit PMA bei 500°C erreicht. Geräte mit PDA bei 400°C zeigten die niedrigere CET und die kleinere D es aber die schlechte Lochbeweglichkeit und der größere Leckstrom im Vergleich zu Transistoren ohne PDA.

Verfügbarkeit von Daten und Materialien

Die Datensätze, die die Schlussfolgerungen dieses Artikels unterstützen, sind im Artikel enthalten.

Abkürzungen

- ALD:

-

Atomlagenabscheidung

- BF2 + :

-

Borfluoridion

- MEZ:

-

Kapazitive effektive Dicke

- Ge:

-

Germanium

- HF:

-

Flusssäure

- HRTEM:

-

Hochauflösendes Transmissionselektronenmikroskop

- IL:

-

Grenzschicht

- MOSFETs:

-

Metall-Oxid-Halbleiter-Feldeffekttransistoren

- Ni:

-

Nickel

- PDA:

-

Glühen nach der Abscheidung

- PMA:

-

Nachglühen des Metalls

- SS:

-

Schwung unter der Schwelle

- TaN:

-

Tantalnitrid

- TDMAZr:

-

Tetrakis (dimethylamido) hafnium

- ZrO2 :

-

Zirkoniumdioxid

- μ eff :

-

Effektive Trägermobilität

Nanomaterialien

- KUHMUTE gestaltet Mobilität mit SLS-3D-Druck neu

- Hochgeschwindigkeits-3D-Druck mit AFPM

- Hochgeschwindigkeits-3D-Druck mit AION500MK3

- Vollständige Terahertz-Polarisationskontrolle mit erweiterter Bandbreite über dielektrische Metaoberflächen

- Compliance-freier ZrO2/ZrO2 − x /ZrO2 Resistiver Speicher mit steuerbarem Grenzflächen-Mehrzustands-Schaltverhalten

- Polarisationskonverter mit steuerbarer Doppelbrechung basierend auf einer hybriden volldielektrischen Graphen-Metaoberfläche

- Hochleistungsfähige organisch-nanostrukturierte Silizium-Hybridsolarzelle mit modifizierter Oberflächenstruktur

- Dielektrische Verstärkung von atomschichtbeschichteten Al2O3/ZrO2/Al2O3-MIM-Kondensatoren durch Mikrowellenglühen

- Eine widerstandslose Spannungsreferenz im Nanomaßstab mit hohem PSRR

- Ge-pMOSFETs hoher Mobilität mit amorpher Si-Passivierung:Einfluss der Oberflächenorientierung