Simulationsstudie des Double-Gate-Tunnel-Feldeffekttransistors mit Stufenkanaldicke

Zusammenfassung

Es wird erwartet, dass ein Doppelgate-Tunnel-Feldeffekttransistor (DG-TFET) die Beschränkungen des Leckstroms und der Steilheit unterhalb der Schwelle erweitert. Es leidet jedoch auch unter dem ambipolaren Verhalten mit der symmetrischen Source/Drain-Architektur. Um den ambipolaren Strom zu überwinden, muss eine Asymmetrie zwischen Source und Drain eingeführt werden. In diesem Papier untersuchen wir die Leistung von DG TFET mit Stufenkanaldicke (SC TFET) unter Verwendung der 2D-Simulation. Die Asymmetrie zwischen Source und Drain wird durch die Stufenkanaldicke eingeführt; daher wird erwartet, dass das ambipolare Verhalten erleichtert wird. Die Ergebnisse zeigen, dass der SC-TFET im Vergleich zum herkömmlichen DG-TFET eine signifikante Reduzierung des ambipolaren Stroms aufweist. Die Mechanismen von SC-TFET werden gründlich diskutiert, um die physikalischen Erkenntnisse zu untersuchen. Die durch die Strukturparameter eingeführten Auswirkungen auf die Onset-Spannung, die Subthreshold-Steigung, den Drain-Strom im eingeschalteten und ambipolaren Zustand werden auch bei der Bestimmung der optimalen Struktur gezeigt.

Hintergrund

Während der extreme Skalierungsprozess fortschreitet, stößt die CMOS-Technologie mit herkömmlichen MOSFETs auf verschiedene Herausforderungen wie den zunehmenden Leckstrom und die unterschwellige Steigung (SS ). Tunnel-Feldeffekttransistoren (TFET), die die Band-zu-Band-Tunneling-(BTBT)-Mechanismen nutzen, werden voraussichtlich die Begrenzungen von Leckstrom und SS . erweitern [1,2,3,4,5,6,7,8]. TFET auf Siliziumbasis weist Vorteile wie hohe Zuverlässigkeit und niedrige Kosten auf. Allerdings weist ein herkömmlicher siliziumbasierter TFET im Vergleich zum MOSFET aufgrund der eingeschränkten BTBT-Rate einen relativ geringen Einschaltstrom auf [9,10,11]. Um das Potenzial von TFETs auf Siliziumbasis zu entwickeln, wurden kürzlich verschiedene neue TFET-Strukturen vorgeschlagen, um den Durchlassstrom zu verbessern. Der Double-Gate-TFET (DG-TFET) zeigt eine verbesserte BTBT-Rate, was zu einem erhöhten Einschaltstrom führt [12,13,14]. Allerdings wird auch der ambipolare Strom von DG TFET erhöht, da die BTBT-Ratenverbesserung auch im ambipolaren Zustand aktiviert wird [15]. Um den ambipolaren Strom weiter zu überwinden, muss eine Asymmetrie zwischen Source und Drain eingeführt werden [16]. DG-TFETs mit Gate-Drain-Unterlappung und geringerer Drain-Dotierungskonzentration sind gängige Methoden, um das ambipolare Problem zu lösen [17,18,19]. Die Gate-Drain-Unterlappung erfordert jedoch einen größeren S/D-Abstand und eine geringere Drain-Dotierungskonzentration erhöht die Serienwiderstände [15]. Eine frühere Arbeit hat gezeigt, dass die ambipolaren Effekte in TFETs mit Drain-Unterlappung durch die Verwendung von Low-k-Abstandshaltern und durch die Anordnung der Kontakte in der oberen und unteren Konfiguration weiter gemildert werden könnten [15], was darauf hindeutet, dass kombinierte Asymmetriestrategien sinnvoll sein könnten in Verbesserung der Leistung des TFET. In unserer vorherigen Arbeit wurde gezeigt, dass der FinFET mit asymmetrischer Finnenbreite die Leistung von FinFET verbessert [20]. Es wird auch angenommen, dass die Kanaldicke t si hat einen signifikanten Einfluss auf die BTBT-Rate von DG TFET [21]; Daher kann die Asymmetrie zwischen der Source-Dicke und der Drain-Dicke den ambipolaren Strom weiter entlasten und muss gründlich untersucht werden.

In diesem Papier untersuchen wir die verschiedenen Leistungen von DG TFET mit Stufenkanaldicke (SC TFET), die Asymmetrie zwischen Source und Drain wird durch die Stufenkanaldicke eingeführt, so dass erwartet wird, dass der ambipolare Strom reduziert wird. Der Rest dieses Dokuments ist wie folgt aufgebaut:Abschnitt 2 stellt die Gerätestruktur und den Simulationsaufbau vor. In Abschnitt 3 werden die Mechanismen des SC-TFET ausführlich diskutiert. Die ausführliche Diskussion über die Auswirkungen von Strukturparametern auf die Übertragungskurven, Onset-Spannung (V Beginn ), durchschnittlicher SS und Drainstrom im eingeschalteten/ambipolaren Zustand ist ebenfalls dargestellt. Schließlich werden die Ergebnisse dieses Papiers in Abschnitt IV beleuchtet.

Struktur und Simulation

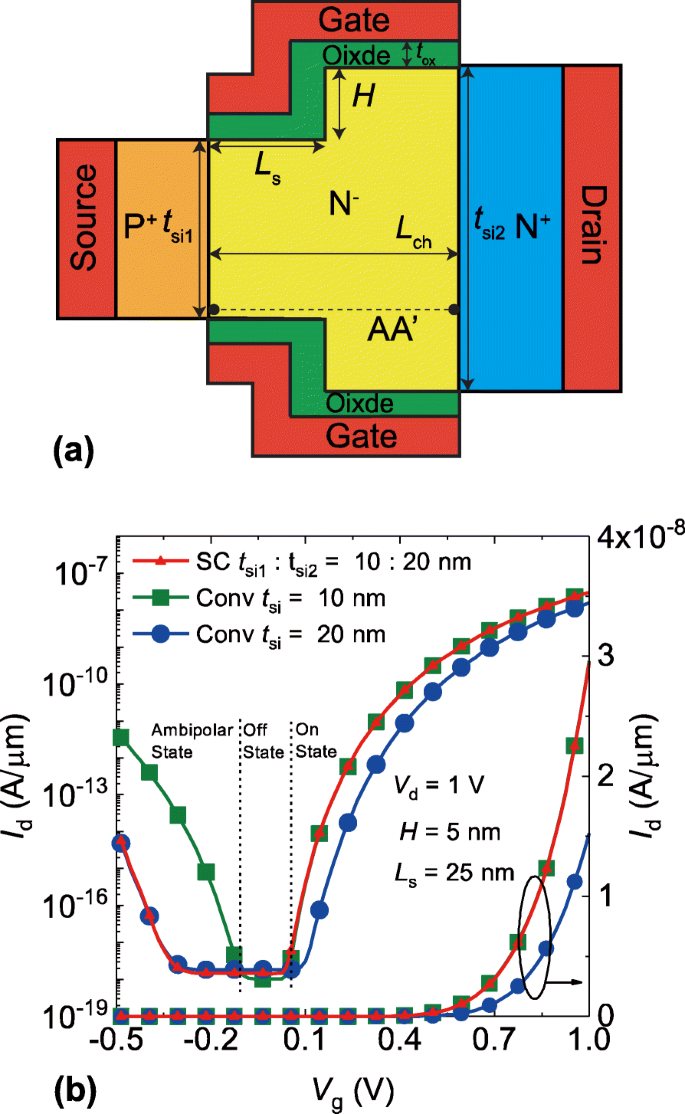

Das schematische Diagramm des in dieser Arbeit betrachteten SC-TFET ist in Abb. 1a dargestellt. Die Kanaldicke in der Nähe des Source-Bereichs ist nicht gleich der Kanaldicke in der Nähe des Drain-Bereichs. An einer bestimmten Stelle im Kanalbereich ändert sich die Kanaldicke stufenweise. Die Stufenhöhe und die Stufenposition werden als H . bezeichnet und L s bzw. t si1 und t si2 die Kanaldicke in der Nähe des Source-Bereichs bzw. des Drain-Bereichs sind. Die effektive Oxiddicke (EOT) beträgt in unserer Simulation 1 nm. Die Source-Region ist hoch p-dotiert (10 20 Atome/cm 3 ) und der Drain-Bereich ist hoch n-dotiert (10 20 Atome/cm 3 ) um den Serienwiderstand zu reduzieren [15], wird der Kanalbereich leicht n-dotiert (10 17 Atome/cm 3 ). Um die Onset-Spannung mit verschiedenen Kanaldicken-Setups zu analysieren, wird die Austrittsarbeit des Metallgates auf 4,5 eV festgelegt, die Gatelänge ist gleich der Kanallänge L ch und auf 50 nm eingestellt [22,23,24,25]. Die Simulationen werden mit dem Sentaurus TCAD Release I-2013.12 [26, 27] durchgeführt. Das Dopingabhängigkeitsmodell und das feldabhängige Mobilitätsmodell sind das vereinheitlichte Mobilitätsmodell von Philips bzw. das Lombardi-Mobilitätsmodell. Die Fermi-Dirac-Statistik, das Shockley-Read-Hall- und das Auger-Rekombinationsmodell werden ebenfalls verwendet. Um die hochdotierten Source/Drain-Gebiete zu berücksichtigen, wird das Bandlücken-Verengungsmodell aktiviert. Das nichtlokale BTBT-Modell basierend auf der Wentzel-Kramer-Brillouin (WKB)-Approximation, abgestimmt mit den experimentellen Ergebnissen von [28], und das Dichtegradienten-Quantisierungsmodell ermöglichen eine genaue Simulation [29, 30]. Die Onset-Spannung ist als die Gate-Spannung definiert, bei der die Subthreshold-Steigung maximal ist. Die durchschnittliche SS wird aus dem Sperrstrom zu I . extrahiert d =10 −11 A/μm.

a 2D-Schaltbild des SC-TFET, t si1 und t si2 sind die Kanaldicken in der Nähe des Source- und des Drain-Gebiets, die Asymmetrie zwischen Source und Drain wird offensichtlich eingeführt. Schnittlinie AA’ ist die Schnittlinie in horizontaler Richtung. Der vertikale Abstand zwischen der Schnittlinie und der Oberfläche des Source-Bereichs beträgt 0,5 nm. b Übertragungskurven des SC-TFETs und der konventionellen DG-TFETs in logarithmischer und linearer Skala

Ergebnisse und Diskussion

Transferkurven und -mechanismus

Abbildung 1b zeigt die Übertragungskurven von SC-TFET und konventionellem DG-TFET im logarithmischen bzw. linearen Maßstab. Wir markieren den Ein-Zustand, den Aus-Zustand und den ambipolaren Zustand in Abb. 1b. Für TFETs sind immer ein höherer Strom im eingeschalteten Zustand und ein niedrigerer Strom im ambipolaren Zustand erwünscht, was erfordert, dass die V Beginn und SS sollte niedrig sein, während der ausgeschaltete Zustand einen weiten Spannungsbereich haben sollte. Wie in Abb. 1b gezeigt, ist das V Beginn des herkömmlichen DG-TFET mit einer Kanaldicke von 10 nm sind geringer als die des DG-TFET mit einer Kanaldicke von 20 nm. Das extrahierte V Beginn von DG TFET mit t si =10 nm ist 0,04 V und sein extrahierter Durchschnitt SS beträgt 44,8 mV/dec, die V Beginn und der durchschnittliche SS konventioneller DG TFET mit t si =20 nm ist 0,1 V bzw. 50,6 mV/dec. Der Drainstrom eines herkömmlichen DG-TFET mit t si =10 nm verbessert sich um 94,7% gegenüber dem herkömmlichen DG TFET mit t si =20 nm. Der Hauptgrund für diese Verbesserung des Drainstroms ist das reduzierte SS und V Beginn . Der Sperrbereich des herkömmlichen DG-TFET mit t si =10 nm sind nur 0,17 V. Der konventionelle DG TFET mit t si =20 nm weist im Vergleich einen Sperrbereich von 0,45 V auf. Als Ergebnis ist der ambipolare Strom des herkömmlichen DG-TFET mit t si =20 nm reduziert sich um 3 Größenordnungen gegenüber dem herkömmlichen DG TFET mit t si =10 nm.

Für den fairen Vergleich die t si1 und t si2 der SC-TFETs sind jeweils gleich den Kanaldicken der obigen herkömmlichen DG-TFETs. Die schmalere Kanaldicke t si1 von SC TFET beträgt 10 nm und die breitere Kanaldicke t si2 des SC-TFET beträgt 20 nm. Die Position der Stufe wird in der Mitte des Kanals angenommen und das L s beträgt 25 nm. Man kann beobachten, dass der SC-TFET vielversprechende Eigenschaften aufweist, einschließlich des hohen Drainstroms im eingeschalteten Zustand sowie des weiten Sperrbereichs. Der Drainstrom von SC-TFET im eingeschalteten Zustand ist ähnlich wie beim herkömmlichen DG-TFET mit t si =10 nm, der Durchschnitt SS beträgt 45,8 mV/dec und die V Beginn beträgt 0,03 V. Allerdings wird der Sperrbereich des SC-TFET um bis zu 123,5% verbessert und der ambipolare Strom wird im Vergleich zum herkömmlichen DG-TFET mit t . ebenfalls um 3 Größenordnungen reduziert si =10 nm. Als Ergebnis ist die Durchlasscharakteristik des SC-TFET ähnlich dem des herkömmlichen DG-TFET mit schmaler Kanaldicke, der SC-TFET zeigt auch nahezu parallele Aus-/Ambipolar-Kurven zu dem herkömmlichen DG-TFET mit großer Kanaldicke. Daher kann der SC-TFET niedrige SS . erreichen , reduziertes V Beginn , und großer Ausschaltbereich gleichzeitig.

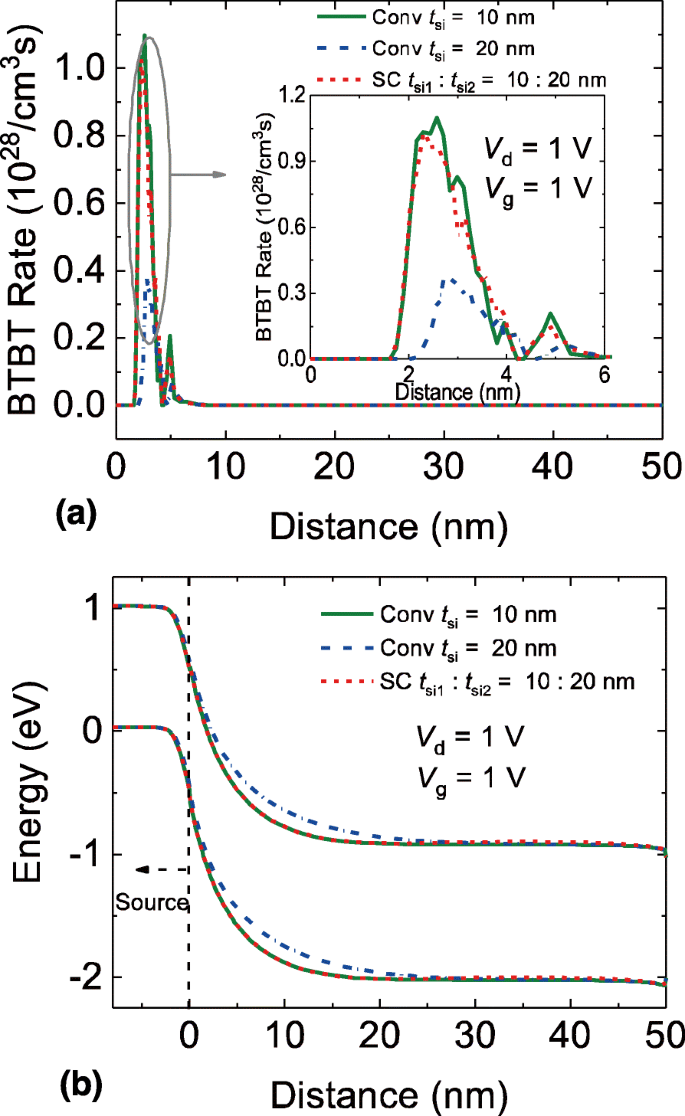

Um den physikalischen Mechanismus des SC-TFET zu untersuchen, vergleichen wir die BTBT-Raten und Energiebanddiagramme im eingeschalteten Zustand, in der Nähe des Onset-Punkts bzw. im ambipolaren Zustand. Abbildung 2a zeigt die BTBT-Raten des SC-TFETs und der herkömmlichen DG-TFETs. Es ist zu erkennen, dass die BTBT-Rate stark von der Kanaldicke abhängt. Tatsächlich ist die Beziehung zwischen der Kanaldicke und dem BTBT-Strom I BTBT kann ausgedrückt werden als [31].

$$ {I}_{BTBT}\propto \exp \left(-\frac{4\lambda \sqrt{2{m}^{\ast }{E_g}^{2/3}}}{3\mathrm {\hslash}\left(\Delta \Phi +{E}_g\right)}\right) $$ (1)

a BTBT-Raten und b Energiebanddiagramm des SC-TFET und der herkömmlichen DG-TFETs im eingeschalteten Zustand, Abstand ist die seitliche Position der Schnittlinie AA’ in Abb. 1

Wo λ =(ε si t si t Ochse /2ε Ochse ) 1/2 ist die natürliche Länge, ε si und ε Ochse sind die Permittivität von Silizium bzw. Oxid und t Ochse ist die Oxiddicke. Φ ist der Energiebereich, über den Tunneln stattfinden kann, E g ist die Bandlücke am Tunnelübergang und m * ist die Tunnelmasse. Gleichung (1) zeigt an, dass das I BTBT sollte als t . zunehmen si reduziert. Daher ist die BTBT-Rate eines herkömmlichen DG-TFET mit t si =10 nm sollte größer sein als der des herkömmlichen DG-TFET mit t si =20 nm. Der SC-TFET zeigt eine ähnliche Verteilung der BTBT-Rate wie der herkömmliche DG-TFET mit t si =10 nm. Dies liegt daran, dass der BTBT im eingeschalteten Zustand hauptsächlich in der Nähe des Source-Übergangs auftritt, daher bestimmt die Kanaldicke in der Nähe des Source-Übergangs die BTBT-Rate im eingeschalteten Zustand. Abbildung 2b zeigt das Energiebanddiagramm des SC-TFET und der herkömmlichen DG-TFETs. Da die BTBT-Rate grundlegend mit der Tunnelentfernung zusammenhängt, erklärt das Energiebanddiagramm, das die Tunnelentfernung klar darstellen kann, den Ursprung der BTBT-Ratenvariation. In Fig. 2b befindet sich der minimale Tunnelabstand des SC-TFET in der Nähe des Source-Übergangs und ist mit t . mehr oder weniger gleich dem des herkömmlichen DG-TFET si =10 nm. Der minimale Tunnelabstand eines herkömmlichen DG-TFET mit t si =20 nm ist deutlich breiter; daher ist seine BTBT-Rate im Vergleich zum SC-TFET und dem herkömmlichen DG-TFET mit geringerer Kanaldicke reduziert.

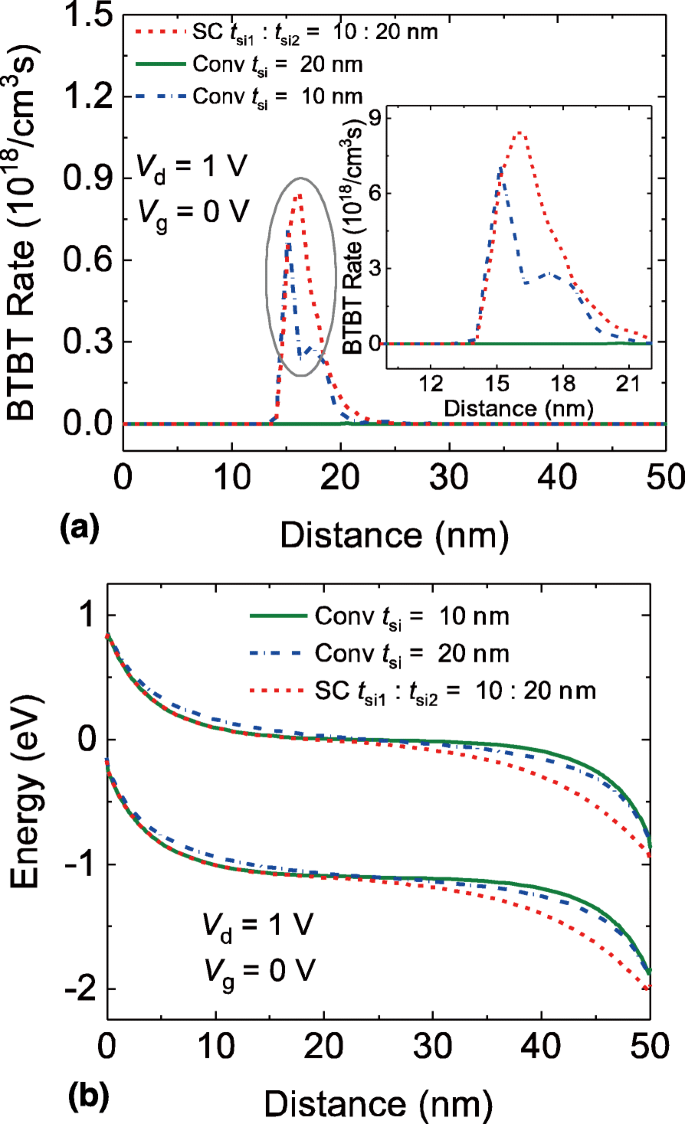

Abbildung 3a zeigt die BTBT-Raten, wenn die Gate-Spannung null ist und nahe der Onset-Spannung liegt. Es ist ersichtlich, dass der SC-TFET die höchste BTBT-Rate besitzt, gefolgt vom konventionellen DG-TFET mit t si =10 nm. Der konventionelle DG TFET mit t si =20 nm zeigt die niedrigste BTBT-Rate. Abbildung 3b zeigt das entsprechende Energiebanddiagramm. Man kann beobachten, dass der Ort des minimalen Abstands vom Valenzband zum Leitungsband in der Mitte des Kanalbereichs liegt. Außerdem ist der Mindestabstand des herkömmlichen DG-TFET mit breiterer Kanaldicke länger als der des SC-TFET und des herkömmlichen DG-TFET mit dünnerer Kanaldicke. Dies deutet darauf hin, dass die Kanaldicke auch einen signifikanten Einfluss auf die BTBT-Rate am Anfangspunkt hat. Daher ist das V Beginn ist auch von der Kanaldicke abhängig. Eine weitere Tatsache ist, dass der SC-TFET mit t . eine höhere BTBT-Rate aufweist als der herkömmliche DG-TFET si =10 nm, obwohl ihre minimalen Kanaldicken gleich sind. Dieses Phänomen wird auf die Variation der Potentialverteilung zurückgeführt, die durch die Ecke der Gate-Elektrode eingeführt wird, wie auch in anderen Arbeiten beobachtet werden kann [32, 33]. Als Ergebnis zeigt der SC-TFET die niedrigste V Beginn , gefolgt vom konventionellen DG TFET mit dünner Kanaldicke, und der konventionelle DG TFET mit breiter Kanaldicke weist die höchsten V . auf Beginn .

a BTBT-Raten und b Energiebanddiagramm des SC-TFETs und der herkömmlichen DG-TFETs im Nah-Einsatzpunkt, Abstand ist die seitliche Position der Schnittlinie AA’ in Abb. 1

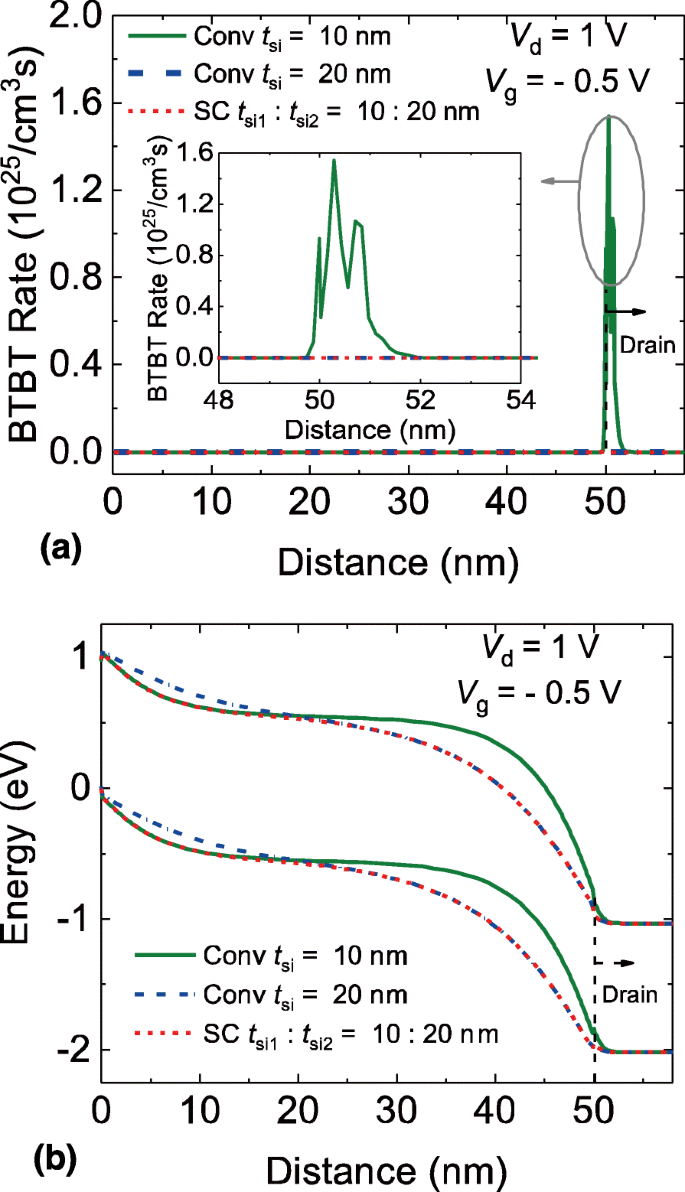

Abbildung 4a zeigt den Vergleich der BTBT-Raten im ambipolaren Zustand. Da die BTBT-Rate stark von der Kanaldicke abhängt, ist der konventionelle TFET mit t si =10 nm zeigt die signifikanteste BTBT-Rate im Vergleich zu den anderen beiden TFET-Strukturen. Der SC-TFET zeigt jedoch eine ähnliche BTBT-Rate wie der herkömmliche DG-TFET mit t si =20 nm. Dies liegt daran, dass das Tunneln hauptsächlich in der Nähe des Drain-Gebiets erzeugt wird und der SC-TFET eine größere Kanaldicke in der Nähe des Drain-Gebiets hat. In Abb. 4b ist auch das Energiebanddiagramm im ambipolaren Zustand dargestellt. Es ist deutlich zu erkennen, dass sich der minimale Tunnelabstand in der Nähe des Drainbereichs befindet. Außerdem sind die Tunnelabstände von SC-TFET und konventionellem DG-TFET mit breiterer Kanaldicke größer als die von konventionellen DG-TFET mit dünnerer Kanaldicke, was zu einem geringen ambipolaren Strom von SC-TFET und konventionellen DG-TFET mit breiterer Kanaldicke führt.

a BTBT-Raten und b Energiebanddiagramm des SC-TFET und der herkömmlichen DG-TFETs im ambipolaren Zustand, Abstand ist die seitliche Position der Schnittlinie AA’ in Abb. 1

Auswirkungen von H und LS auf DC-Eigenschaften

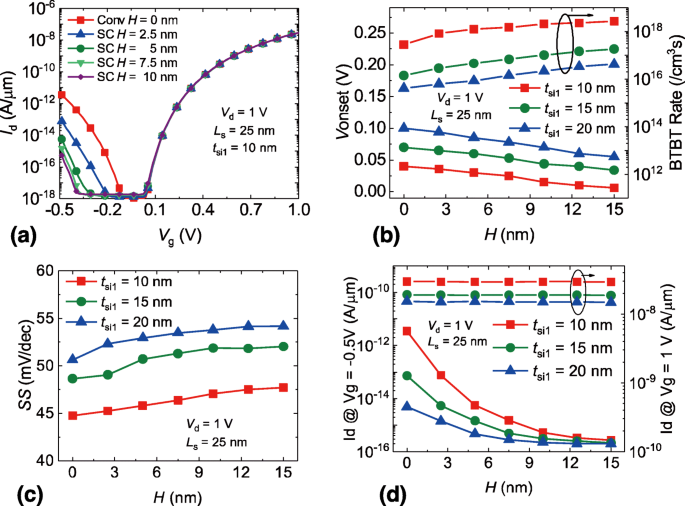

Abbildung 5a zeigt die Transferkurven des SC-TFET mit verschiedenen H und t si1 =10 nm. Es ist zu erkennen, dass die H hat weniger Einfluss auf den Durchlassstrom. Der ambipolare Strom nimmt jedoch deutlich ab, wenn der H steigt, der Ausschaltbereich verbessert sich mit dem Anstieg von H sowie. Es ist auch zu sehen, dass die Reduzierung des ambipolaren Stroms mit dem H . abnimmt steigt. Der Grund dafür ist, dass der Kopplungseffekt der Double-Gate-Struktur bei größerer Kanaldicke tendenziell weniger stark ausfällt [31]. Daher als H erhöht, werden die BTBT-Raten unabhängiger von der Kanaldicke, was zur Sättigung des ambipolaren Stroms führt. Um den optimalen Strukturparameter weiter zu untersuchen, werden die Auswirkungen von H variiert von 0 bis 15 nm auf den Geräteleistungen werden extrahiert und in Abb. 5b–d gezeigt. Abbildung 5b zeigt das V Beginn und die BTBT-Ratenvariation mit verschiedenen H und t si1 . Es ist zu erkennen, dass das V Beginn nimmt monoton mit Zunahme von H . ab . Dies liegt daran, dass die Ecke der Gate-Elektrode die Variation der Potentialverteilung im Kanalbereich einführen würde [32, 33], was zu einer Änderung der BTBT-Rate und der V . führt Beginn . Abbildung 5b zeigt, dass die BTBT-Rate mit dem H . steigt verbessert. Infolgedessen verringert sich das V Beginn findet man mit dem erhöhten H . Man kann auch beobachten, dass V Beginn steigt mit dem t si1 steigt. Der Hauptgrund ist, dass die erhöhte t si1 schwächt die BTBT-Rate, was zu einem höheren V . führt Beginn . In Abb. 5c ist der extrahierte Durchschnitt SS von SC TFET mit verschiedenen H und t si1 wird gezeigt. Der Trend der SS mit verschiedenen H ist entgegengesetzt zu dem des V Beginn . Mit anderen Worten, die SS steigt als das H steigt. Wir haben erwähnt, dass der Drain-Strom im eingeschalteten Zustand von t . abhängt si1 , so dass die SC-TFETs mit unterschiedlichem H aber mit dem gleichen t si1 sollte im eingeschalteten Zustand einen ähnlichen Drainstrom haben. Außerdem ist auch bekannt, dass die V Beginn nimmt mit der Zunahme von H . ab . Dies impliziert, dass der Bereich der Gatespannung zum Treiben des gleichen Drainstroms verbessert wird als der H steigt. Als Ergebnis ist der durchschnittliche SS steigt monoton mit dem Anstieg von H . Es ist auch zu sehen, dass der Anstieg von t si1 wird die SS untergraben , was auf die reduzierte Gate-Steuerungsfähigkeit zurückzuführen ist. Abbildung 5d zeigt den Drainstrom im eingeschalteten und ambipolaren Zustand mit unterschiedlichem H und t si1 , bzw. Der Durchlassstrom ist nahezu unabhängig von H , aber es wird stark von der t beeinflusst si1 , was unserem vorherigen Ergebnis entspricht, dass das Tunneln im eingeschalteten Zustand hauptsächlich in der Nähe des Source-Gebiets auftritt und stark von der Kanaldicke in der Nähe des Source-Gebiets abhängt. Der ambipolare Strom nimmt jedoch mit dem H steigt. Da das Tunneln im ambipolaren Zustand in der Nähe der Drain-Region dominiert wird, ist der Anstieg von H verbessert die Kanaldicke an der Drainseite und schwächt somit den ambipolaren Strom. Es ist auch zu sehen, dass der ambipolare Strom stärker abfällt, wenn der H kleiner als 10 nm ist, was auf den größeren Kopplungseffekt bei geringerer Kanaldicke zurückzuführen ist.

Die Auswirkungen von H auf der a Übertragungskurven, b V Beginn und BTBT-Rate, c durchschnittlicher SS , und d Drainstrom im eingeschalteten/ambipolaren Zustand, H ist die Höhe der Stufe und H =0 nm repräsentiert den herkömmlichen DG TFET

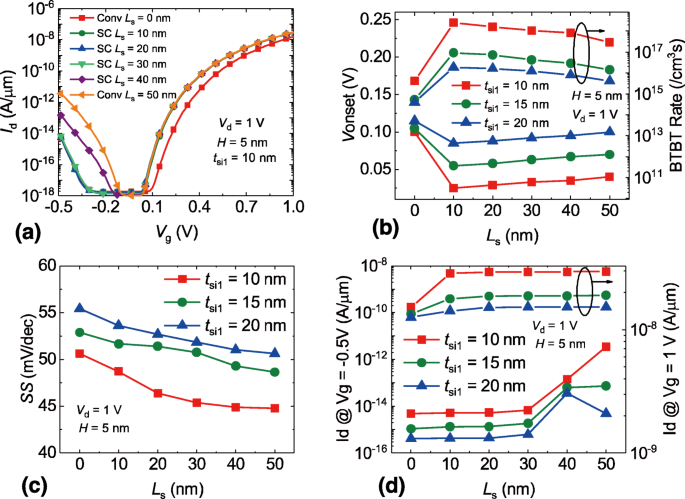

In Abb. 6a sind die Transferkurven von SC-TFET mit unterschiedlichen L s werden jeweils vorgestellt. L s =0 nm repräsentiert den konventionellen DG TFET mit entsprechendem t si2 und L s =50 nm repräsentiert den konventionellen DG TFET mit entsprechendem t si1 . Es ist ersichtlich, dass die Lage der Stufe einen signifikanten Einfluss auf den ambipolaren Strom und den Sperrbereich hat. Die SC-TFETs mit L s weniger als 30 nm zeigen einen ähnlichen ambipolaren Strom- und Sperrbereich. Als L s 30 nm überschreitet, wird der ambipolare Strom stark verstärkt. Abb. 6b zeigt das V Beginn und die BTBT-Ratenvariation mit verschiedenen L s und t si1 , der Trend, dass die V Beginn steigt mit dem t si1 Auch eine Verbesserung ist deutlich zu beobachten. Der Wendepunkt auf dem L s =10 nm ergibt sich aus der Vielfalt der t si1 . Seit L s =0 nm ist der konventionelle DG-TFET mit einer größeren Kanaldicke, die BTBT-Rate würde sich verringern, was zu einem erhöhten V . führt Beginn und ein verringerter Durchlassstrom. Abgesehen vom Fall des herkömmlichen DG-TFET ist der V Beginn von SC TFET wird monoton erhöht, da der L s steigt, was auf die durch die Stufenkanalstruktur induzierte reduzierte BTBT-Rate zurückzuführen ist. Abbildung 6c zeigt die Auswirkungen des L s und t si1 auf der SS von SC-TFETs. Das erhöhte t si1 führt zu einem verschlechterten SS . Nach Gl. (1) würde eine erhöhte Kanaldicke die Kopplungseffekte zwischen den Gate-Elektroden verringern, was zu einer verringerten Gate-Steuerungsfähigkeit und einem erhöhten SS . führt [12]. Als L s abfällt, wird sich der Bereich mit größerer Kanaldicke ausdehnen und würde die gesamte Gate-Steuerungsfähigkeit schwächen. Als Ergebnis wird ein reduziertes L s wird die SS untergraben von SC-TFETs, was in Abb. 6c deutlich zu erkennen ist. Abbildung 6d zeigt den Drainstrom im eingeschalteten und ambipolaren Zustand mit unterschiedlichem L s und t si1 , bzw. Man kann beobachten, dass der Durchlassstrom des SC-TFET mehr oder weniger gleich dem des herkömmlichen DG-TFET mit entsprechendem t . ist si1 . Was den ambipolaren Strom betrifft, so sind die SC-TFETs mit L s weniger als 30 nm zeigen einen ähnlichen Strom wie bei herkömmlichen DG-TFETs mit entsprechendem t si2 . Wenn das L s auf 40 nm ansteigt, steigt der ambipolare Strom dramatisch an. Im Fall von SC-TFET mit L s =40 nm und t si1 =20 nm, sein ambipolarer Strom ist mit t . sogar größer als der des herkömmlichen DG-TFET si1 =20 nm. Dies liegt daran, dass der vertikale Teil der Gate-Elektrode die Tunnelfläche verbessern kann, insbesondere wenn der vertikale Teil der Gate-Elektrode nahe am PN-Übergang liegt [34]. Es zeigt an, dass das L s sollte weniger als 40 nm betragen, um den ambipolaren Strom zu reduzieren.

Die Auswirkungen von L s auf der a Übertragungskurven, b V Beginn und BTBT-Rate, c durchschnittlicher SS , und d Drainstrom im eingeschalteten/ambipolaren Zustand, L s ist der seitliche Abstand von der Quellregion zur Stufe, L s =0 nm repräsentiert den konventionellen DG TFET mit entsprechendem t si2 und L s =50 nm repräsentiert den konventionellen DG TFET mit entsprechendem t si1.

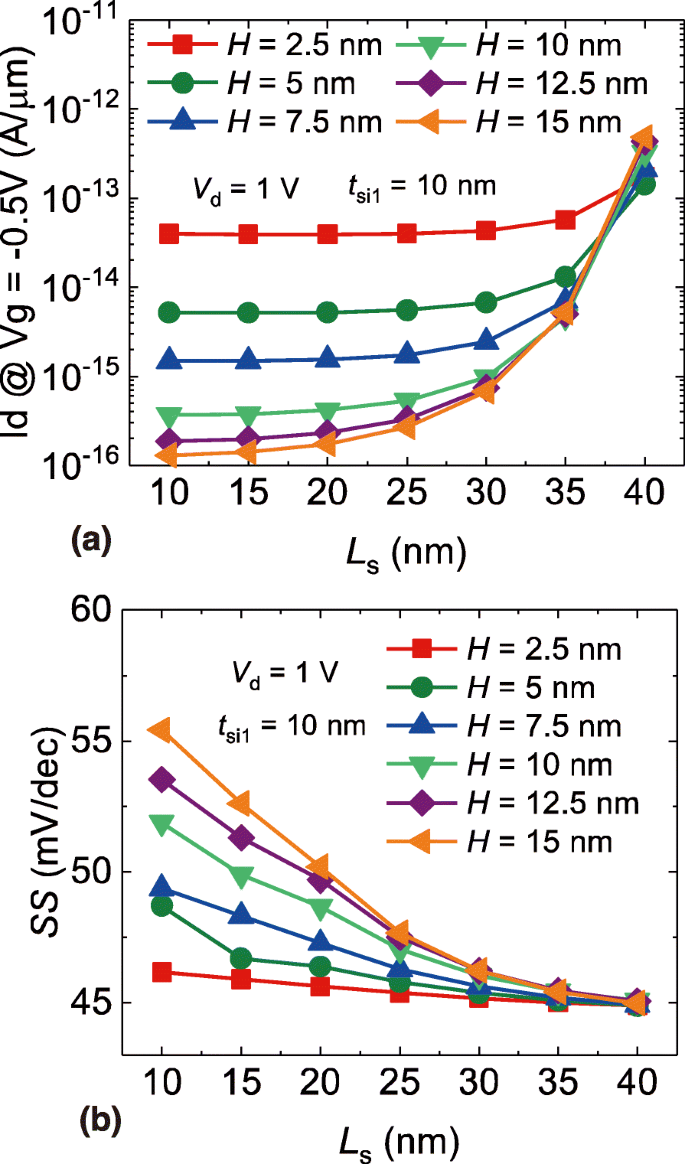

Um die optimalen Strukturparameter des SC-TFET zu bestimmen, wird eine orthogonale Simulation durchgeführt, indem der kombinierte Effekt des H . untersucht wird und das L s auf die Geräteleistung. Die t si1 ist auf 10 nm festgelegt, um einen größeren Durchlassstrom zu erreichen. In Abb. 7a wird der ambipolare Strom als Funktion von L . extrahiert s mit verschiedenen H . Es ist deutlich zu erkennen, dass der ambipolare Strom deutlich abnimmt, wenn der H abnimmt, was darauf hindeutet, dass ein höheres H ist vielversprechend im Hinblick auf die Erzielung eines geringeren ambipolaren Stroms. Allerdings kann man beobachten, dass der Nutzen einer größeren H ist weniger bedeutsam. Daher ein H =15 nm wäre der optimale Wert, wenn man bedenkt, dass ein größeres H konnte nur die Gerätefläche vergrößern. In der Zwischenzeit ein verringertes L s senkt auch den ambipolaren Strom, insbesondere bei einem größeren H . Daher ist ein niedrigeres L s ist zum Zwecke eines minimalen ambipolaren Stroms erwünscht. Trotzdem ein niedrigeres L s könnte auch zu einer Erhöhung der unterschwelligen Steigung führen, wie in Abb. 7b zu sehen ist. Die unterschwellige Steigung steigt langsam mit einem höheren L s steigt aber schnell mit einem niedrigeren L s , was darauf hinweist, dass ein L s etwa 25 nm wäre der Kompromisswert. Als Ergebnis wären die optimalen Geräteparameter H =15 nm und L s =25 nm, wobei sowohl der ambipolare Strom als auch die Steigung unterhalb der Schwelle relativ gering sind.

a Der ambipolare Strom und b die unterschwellige Steigung des SC-TFET als Funktion von L S mit verschiedenen H

Herstellungsmethode

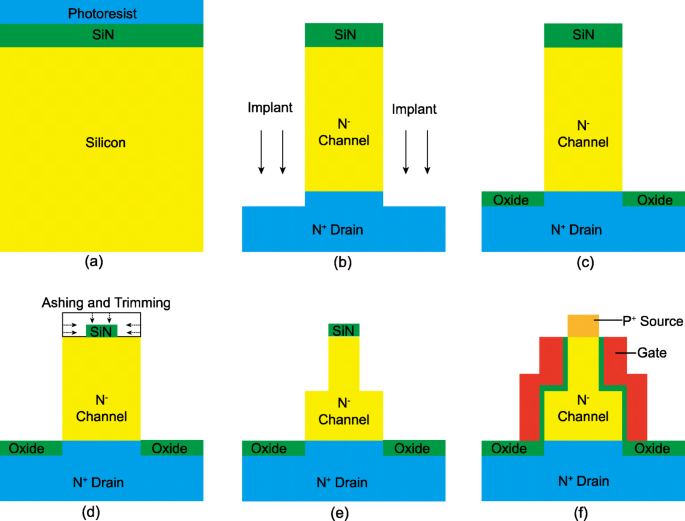

Ein durchführbarer Herstellungsprozess des SC-TFET ist in 8 gezeigt. Aufgrund der einzigartigen Kanalform kann die Stufenkanaldicke leichter durch Anwenden der vertikalen Struktur erreicht werden. Der Prozess beginnt mit der Vorbereitung des Siliziumsubstrats mit SiN und Photoresistabscheidung, wie in Fig. 8a gezeigt. In 8b wird die SiN-Strukturierung durch Lithographie erreicht, gefolgt vom Ätzen, um den Kanalbereich zu bilden, dann wird die N + Die Region wird durch eine vertikale As-Implantation und Ausheilung eingeführt [35]. Danach wird das Isolationsoxid abgeschieden, um zu verhindern, dass der Drain-Bereich im folgenden Prozess geätzt wird, wie in Fig. 8c gezeigt. In Fig. 8d werden das Veraschen und Trimmen durch Verwenden des Reaktionsionenätzens [36] übernommen, um die Dicke und Breite von SiN zu verringern. Die Stufenkanaldicke wird dann durch Ätzen eingebracht, wie in Fig. 8e gezeigt. Die verbleibenden Prozesse sind denen des herkömmlichen vertikalen TFET ähnlich und beinhalten die Bildung von Gateoxid, Gateabscheidung, Siliziumfreilegung und Implantation des Sourcebereichs [35, 37], wie in Fig. 8f gezeigt.

Herstellungsprozess des SC TFET. a Vorbereitung des Siliziumsubstrats mit SiN und Photoresistabscheidung. b Ätzen, Implantieren und Tempern. c Abscheidung von Isolationsoxiden. d Reduzierung der Dicke und Breite von SiN durch Veraschen und Besäumen. e Die Stufenkanaldicke wird eingeführt. f Gateoxidbildung, Gateabscheidung, Gateplanarisierung und Sourcebereichimplantation

Schlussfolgerung

Wir untersuchen die elektrische Leistung von DG TFET mit Stufenkanaldicke (SC TFET) unter Verwendung der 2D-Simulation. Die Asymmetrie zwischen Source und Drain wird durch die Stufenkanaldicke eingeführt; daher wird das ambipolare Verhalten deutlich gemildert. Der SC-TFET weist ähnliche Durchlasseigenschaften wie der herkömmliche DG-TFET mit entsprechenden t . auf si1 und parallele Aus-/Ambipolar-Kurven des herkömmlichen DG-TFET mit entsprechendem t si2 . Als Ergebnis kann der SC-TFET einen großen Sperrbereich, einen niedrigen ambipolaren Strom erreichen und den niedrigen SS . aufrechterhalten gleichzeitig. Die Mechanismen von SC-TFET werden gründlich diskutiert, um die physikalischen Erkenntnisse zu untersuchen. Die durch die Strukturparameter eingeführten Auswirkungen auf die Onset-Spannung, die Subthreshold-Steigung, den Drain-Strom im eingeschalteten Zustand und den ambipolaren Zustand werden ebenfalls untersucht, um die optimale Struktur zu bestimmen. Der SC-TFET mit H von 15 nm und L s von 25 nm zeigt die optimalen Leistungen. Darüber hinaus bietet die Architektur der Stufenkanaldicke ein alternatives Asymmetrieverfahren. Da sich die kombinierten Asymmetriestrategien als effektiv erwiesen haben, könnte unsere Arbeit die Leistungsfähigkeit des TFET weiter verbessern.

Verfügbarkeit von Daten und Materialien

Alle Daten sind uneingeschränkt verfügbar.

Abkürzungen

- DG TFET:

-

Doppel-Gate-Tunnel-Feldeffekttransistor

- SC-TFET:

-

DG TFET mit Stufenkanaldicke

- SS :

-

Unterschwellige Steigung

- BTBT:

-

Band-zu-Band-Tunneling

- EOT:

-

Effektive Oxiddicke

- V Beginn :

-

Onset-Spannung

- H :

-

Stufenhöhe

- L s :

-

Schrittposition

- L ch :

-

Kanallänge

- t si :

-

Kanaldicke

- t si1 :

-

Kanaldicke nahe der Quellregion

- t si2 :

-

Kanaldicke in der Nähe des Drainbereichs

Nanomaterialien

- Die Teile verbinden:FACE-konforme tragbare Komponente in eine Simulationsumgebung integrieren

- Der Sperrschicht-Feldeffekttransistor (JFET) als Schalter

- Die Leckstromkomponenten in Kurzkanal-MOS-Transistoren verstehen

- Im Einklang mit dem Herzen eines Kupferatoms

- MoS2 mit kontrollierter Dicke für die elektrokatalytische Wasserstoffentwicklung

- Oberflächeneffekt auf den Öltransport in Nanokanälen:eine molekulardynamische Studie

- Die Untersuchung eines neuartigen, durch Nanopartikel verbesserten wurmähnlichen Mizellensystems

- Die Optimierung der Programmierung von kapazitiven 1T DRAM basierend auf dem Dual-Gate-TFET

- Einwandige Kohlenstoff-Nanoröhrchen-dominierte mikrometerbreite Streifenmusterbasierte ferroelektrische Feldeffekttransistoren mit HfO2-Defektkontrollschicht

- Kanal-Plasmon-Nanodraht-Laser mit V-Groove-Hohlräumen