Analog/HF-Leistung eines T-Gate-Dual-Source-Tunnel-Feldeffekttransistors

Zusammenfassung

In diesem Beitrag wird ein siliziumbasierter T-Gate-Dual-Source-Tunnel-Feldeffekttransistor (TGTFET) vorgeschlagen und durch TCAD-Simulation untersucht. Als Kontraststudie werden die Struktur, die Charakteristik und die analoge/HF-Leistung von TGTFET, LTFET und UTFET diskutiert. Die durch das T-förmige Gate eingeführte Gate-Überlappung kann die Effizienz des Tunnelübergangs verbessern. Die Dual-Source-Regionen im TGTFET können den Durchlassstrom erhöhen (I EIN ) durch das Angebot einer verdoppelten Tunnelverbindungsfläche. Um die Geräteleistung weiter zu verbessern, wird die n+-Tasche in den TGTFET eingeführt, um die Tunnelrate von Band zu Band weiter zu erhöhen. Simulationsergebnisse zeigen, dass das I . des TGTFET EIN und Schaltverhältnis (I EIN /Ich AUS ) erreichen 81 μA/μm und 6,7 × 10 10 bei 1 V Gate-zu-Source-Spannung (V g ). Der durchschnittliche unterschwellige Swing von TGTFET (SSavg , von 0 bis 0,5 V V g ) erreicht 51,5 mV/dez und der minimale unterschwellige Ausschlag des TGTFET (SSmin , bei 0,1 V V g ) erreicht 24,4 mV/Dez. Darüber hinaus wurde festgestellt, dass TGTFET eine starke Robustheit gegenüber dem Drain-induzierten Barrieresenkungseffekt (DIBL) aufweisen. Die Auswirkungen der Dotierungskonzentration, der geometrischen Abmessungen und der angelegten Spannung auf die Geräteleistung werden untersucht, um die TGTFET-Designrichtlinie zu erstellen. Darüber hinaus ist die Transkonduktanz (g m ), Ausgangsleitwert (g ds ), Gate-Source-Kapazität (C gs ), Gate-Drain-Kapazität (C gd ), Grenzfrequenz (f T ) und die Verstärkungsbandbreite (GBW) des TGTFET erreichen 232 μS/μm, 214 μS/μm, 0,7 fF/μm, 3,7 fF/μm, 11,9 GHz und 2,3 GHz bei 0,5 V Drain-Source-Spannung (V d ), bzw. Der TGTFET profitiert vom strukturellen Vorteil und erzielt im Vergleich zu UTFET und LTFET bessere DC/AC-Eigenschaften. Zusammenfassend lässt sich sagen, dass die beachtlich gute Leistung TGTFET zu einer sehr attraktiven Wahl für die nächste Generation von Low-Power- und Analog-/RF-Anwendungen macht.

Hintergrund

Die Verkleinerung von Metall-Oxid-Halbleiter-Feldeffekttransistoren (MOSFETs) bringt eine signifikante Verbesserung des Stromverbrauchs integrierter Schaltungen (IC), der Schaltcharakteristik, der Schaltungsfunktion und der IC-Dichte [1, 2]. Aber der unüberbrückbare Widerspruch zwischen der Skalierung der Versorgungsspannung und der Reduzierung der Sperrströme (I AUS ) führt schließlich zu einem inakzeptabel hohen Stromverbrauch [3]. Gleichzeitig wird die Verschlechterung der Zuverlässigkeit durch Kurzkanaleffekte (SCEs) immer gravierender [4, 5]. Um diese Probleme anzugehen, ist es gültig, den Subthreshold-Swing (SS) und die Versorgungsspannung der Geräte zu reduzieren. Basierend auf dem Band-zu-Band-Tunnelmechanismus erreichen Tunnel-Feldeffekttransistoren (TFETs) den Subthreshold-Swing (SS) kleiner als 60 mV/dec und könnten die Versorgungsspannung effektiv reduzieren [6,7,8,9,10] . Darüber hinaus hat der TFET aufgrund des Tunnelübergangs in der Nähe der Source normalerweise eine kleine Gate-Source-Kapazität (C gs ) [1, 11], was sich positiv auf die Frequenzleistung des Geräts auswirkt.

Jüngste Studien zeigen, dass TFET ein vielversprechender Kandidat für zukünftige Low-Power-Anwendungen [12,13,14,15,16] und analoge/RF-Anwendungen [17,18,19] zu sein scheint. Aufgrund der kleinen effektiven Tunnelfläche wird der begrenzte Tunnelstrom jedoch zu einem inhärenten Nachteil bei herkömmlichen P-I-N-TFET, was zu einem niedrigen Betriebsstrom im Durchlasszustand (I EIN ). Um die TFET-Leistung zu verbessern, wurden in den letzten Jahren viele neue Strukturen vorgeschlagen [20,21,22,23,24,25]. Ausgehend von dem vertieften Gate wurden L-förmige Tunnel-Feldeffekttransistoren (LTFET) [23, 24] und U-förmige Tunnel-Feldeffekttransistoren (UTFET) [25] vorgeschlagen, um hohe I EIN mit kompaktem Geräteaufbau. Es gibt jedoch noch viel Raum für Verbesserungen bei LTFET und UTFET und es muss mehr Aufwand betrieben werden, um die analoge/HF-Leistung dieser Geräte zu untersuchen.

In diesem Papier wird ein T-Gate-Dual-Source-Tunnel-Feldeffekttransistor (TGTFET) mit Dual-Source vorgestellt und durch TCAD-Simulation untersucht. Der entwickelte TGTFET kann die Tunnelübergangsfläche im Vergleich zu LTFET und UTFET verdoppeln. Die durch das entworfene T-Form-Gate eingeführte Gate-Überlappung kann die Band-zu-Band-Tunnelrate (BBT-Rate) verbessern. Die Simulationsergebnisse zeigen, dass der vorgeschlagene TGTFET ein höheres I . erreicht EIN (8,1 × 10 − 5 A/μm bei V d = 1 V) als LTFET und UTFET unter den gleichen Bedingungen. Beide SSmin (bei V g = 0,1 V) und der SSDurchschn. (0~0,5 V V g ) des TGTFET sind niedriger als 60 mV/Dez (24,4 mV/Dez bzw. 51,5 mV/Dez). TGTFET gewinnt bessere Eingangs-/Ausgangscharakteristik (g m = 232 μS/μm, g ds = 214 μS/μm) als bei UTFET und LTFET. Darüber hinaus werden die Kapazitätseigenschaften von TGTFET, UTFET und LTFET ausführlich diskutiert. Schließlich erreicht der TGTFET eine bessere analoge/HF-Leistung (f T = 11,9 GHz und GBW =2,3 GHz) im Vergleich zu UTFET und LTFET. Als Ergebnis können TGTFET mit beachtlich guter Leistung erhalten werden. Die Strukturen dieses Papiers sind wie folgt:Der Abschnitt „Methoden“ enthält die Beschreibung der Struktur und der Parameter von TGTFET, LTFET [23, 24] und UTFET [25 ] sowie die TCAD-Simulationsmethoden. Der Abschnitt „Ergebnisse und Diskussion“ enthält die Beschreibung der Simulationsergebnisse. In diesem Abschnitt werden der Mechanismus, die Charakteristik und die analoge/HF-Leistung von TGTFET untersucht und mit LTFET und UTFET verglichen. Auch der Einfluss der Geräteparameter auf den TGTFET wird detailliert analysiert. Der Abschnitt „Schlussfolgerungen“ gibt einen Abschluss dieses Dokuments.

Methoden

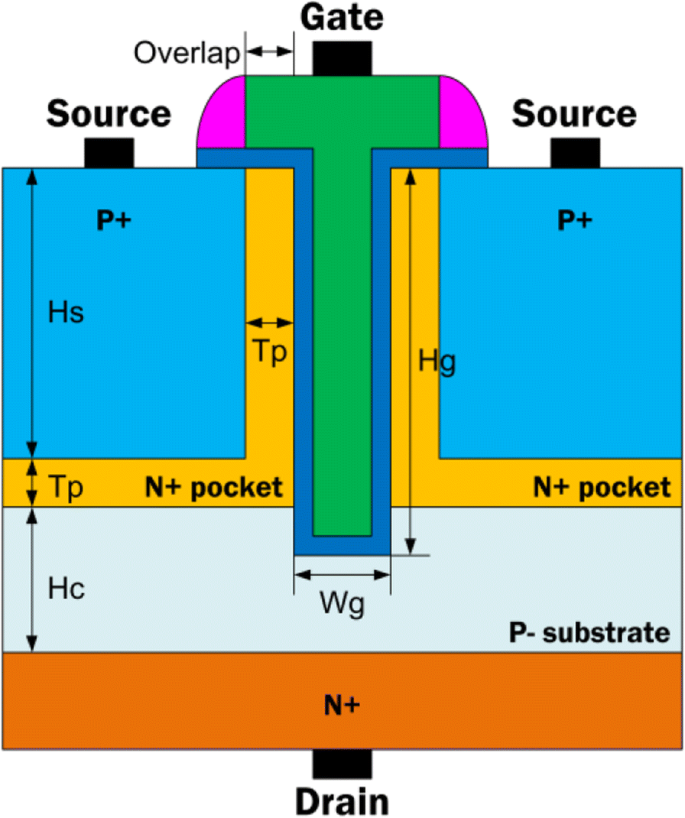

Die Struktur des T-Gate-Dual-Source-Tunnel-Feldeffekttransistors (TGTFET) ist in Abb. 1 dargestellt. Die Form des Gates ähnelt dem Buchstaben „T“ (grüner Bereich). Die Dual-Source-Gebiete befinden sich auf zwei Seiten des Gates (Saphir-Gebiete). Zwei n+ Taschen (gelbe Regionen) werden eingefügt, um die Tunnelrate des Kanals zu erhöhen [20,21,22]. Der n+-Drain wird im Boden des Kanals platziert. Daher überlappt das T-förmige Gate die n+ Taschen sowohl in vertikaler als auch in seitlicher Richtung. Auf diese Weise kann das elektrische Feld am oberen Ende des Tunnelübergangs erhöht werden. Die Verstärkung des elektrischen Felds bewirkt, dass sich das Energieband steiler biegt. Schließlich wird die Elektronentunnelrate aufgrund der Verstärkung des elektrischen Eckfelds erhöht [26].

Schema des vorgeschlagenen T-Gate-Dual-Source-Tunnel-Feldeffekttransistors (TGTFET)

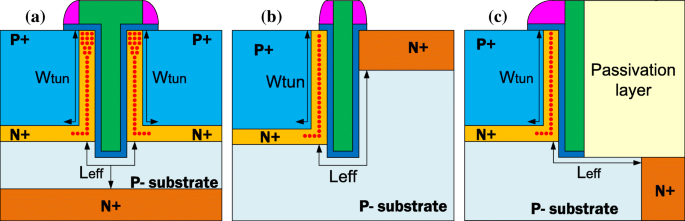

Abbildung 2 zeigt die Gerätestruktur von LTFET [23, 24], UTFET [25] und TGTFET. Die Gate-Überlappung kann dazu beitragen, die Tunneleffizienz von TGTFET zu verbessern. Die Dual-Source-Regionen in TGTFET können die Tunnelübergangsfläche im Vergleich zu LTFET und UTFET verdoppeln.

Vergleich von a der vorgeschlagene TGTFET, b UTFET und c LTFET

Die Parameter von siliziumbasierten TGTFET, UTFET und LTFET, die in Simulationen verwendet werden, sind wie folgt:Hs =30 nm (Höhe des Source-Bereichs), Hg =40 nm (Höhe des vertieften Gates), Wg =6 nm (Breite des Gate-Bereich), Hc =15 nm (Höhe des Kanalbereichs), Tp =5 nm (Dicke der n+-Tasche), ϕ = 4. 33 eV (Gate-Austrittsarbeit), Tox =2 nm (Dicke des HfO2 Gatedielektrikum), N S = 1 × 10 20 cm −3 (p+ Dotierungskonzentration der Quelle), N D = 1 × 10 19 cm −3 (n+ Drain-Dotierungskonzentration), N sub = 1 × 10 17 cm −3 (p-Substrat-Dotierungskonzentration) und N P = 5 × 10 18 cm −3 (n+ Taschen-Dotierungskonzentration). Der Breitenkoeffizient in der Simulation beträgt standardmäßig 1 μm.

Simulationen von TGTFET, UTFET und LTFET werden in TCAD-Tools von Silvaco Atlas durchgeführt. In dieser Simulation wird ein nicht-lokales BTBT-Modell eingeführt, um die räumliche Variation des Energiebandes zu berücksichtigen, was dazu beitragen kann, die Genauigkeit des BTBT-Tunnelprozesses zu erleichtern. Es wird angenommen, dass das Lombardi-Mobilitätsmodell die Kanalmobilität genauer macht (indem die Oberflächenstreuung einschließlich des transversalen Felds und der Dotierungskonzentration berücksichtigt wird). Fermi-Statistiken und Bandlücken-Verengungsmodell werden berücksichtigt, um den Effekt der hochdotierten Bereiche anzupassen. Auch das Shockley-Read-Hall-Rekombinationsmodell wird in diesem Papier berücksichtigt.

Ergebnisse und Diskussion

Gerätemechanismus und DC-Eigenschaften mit unterschiedlichen Parametern

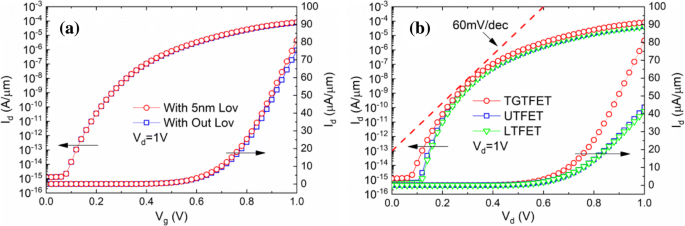

Abbildung 3a zeigt die Übertragungseigenschaften des TGTFET mit und ohne Gate-Überlappung. Mit der zusätzlichen Torüberlappung wird das I EIN erhöht sich von 7,5 × 10 −5 bis 8,1 × 10 −5 A/μ m um V g = V d = 1 V. Abbildung 3b zeigt die Übertragungskennlinien von TGTFET, UTFET und LTFET. Um den Vergleich genauer zu gestalten, werden die Simulationsmodelle und geometrischen Abmessungen dieser drei Geräte identisch eingestellt. Als Ergebnis weist der TGTFET einen etwa zweifachen Anstieg des I . auf EIN im Vergleich zu LTFET und UTFET, wie in Abb. 3b gezeigt. SSmin des TGTFET beträgt 24,4 mV/dec bei V g = 0,1 V und SSDurchschn. 51,5 mV/dez beträgt, wenn 0 V < V g < 0,5 V. Die Schaltverhältnisse (I EIN /Ich AUS ) sind 6,7 × 10 10 bei V g = V d = 1 V und 6,5 × 10 8 bei V g = V d = 0,5 V.

Simuliertes a Übertragungseigenschaften von TGTFET mit/ohne Gate-Überlappung und b Übertragungseigenschaften von TGTFET, UTFET und LTFET

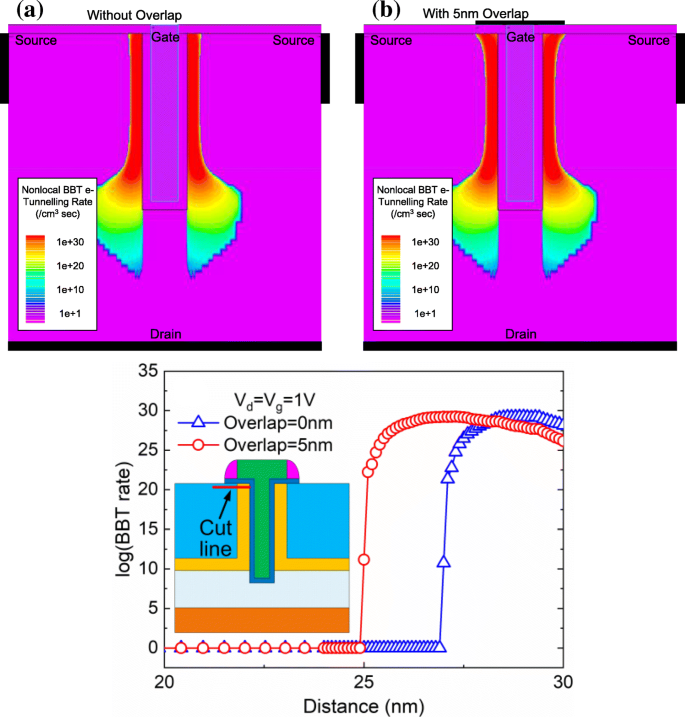

Abbildung 4a, b zeigen die BBT-Rate von TGTFET mit und ohne 5-nm-Gate-Überlappung. Aus Abb. 4c können wir deutlich erkennen, dass das Gerät mit einer Gate-Überlappung von 5 nm einen breiteren Elektronentunnelbereich unter der Oberfläche des Geräts hat, was zu I . führen kann EIN zunehmend.

Simulierte BBT-Elektronentunnelratendiagramme von a Gerät ohne Torüberlappung, b Gerät mit 5-nm-Gate-Überlappung und c die BBT-Elektronentunnelrate von zwei Geräten bei 1 nm unter der Geräteoberfläche; V g = V d = 1 V

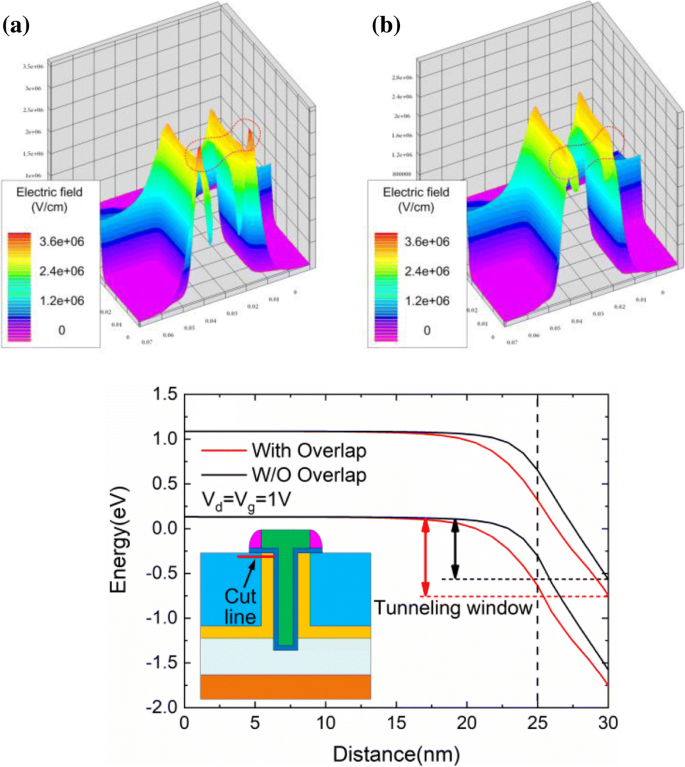

Abbildung 5a, b zeigt das 3D-Diagramm der elektrischen Felder von TGTFET mit und ohne Gate-Überlappung. In einem TGTFET mit einer Gate-Überlappung von 5 nm treten zwei Spitzen des elektrischen Felds auf, wie in dem gestrichelten Kreis in Abb. 5a gezeigt. In Fig. 5b erscheint kein Peak des elektrischen Felds, der auf das Fehlen der Gate-Überlappung zurückzuführen ist. Abbildung 5c zeigt die Energiebandstruktur unter der Oberfläche des Geräts. Der Einschub in Abb. 5c zeigt die Position der Schnittlinie. Mit der Gate-Überlappung kann ein größeres Tunnelfenster erhalten werden. Daher eine höhere BBT-Rate und I EIN erreicht werden kann.

3D-Schemadiagramm der elektrischen Felder des Geräts a mit Überlappung und b ohne Überlappung; simuliert c Energiebanddiagramme von der Quelle bis zur Taschenregion (1 nm unterhalb der Oxidgrenzfläche)

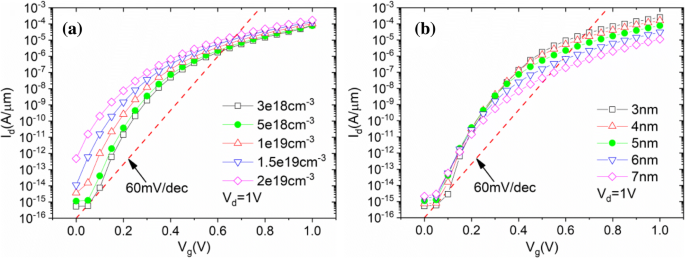

Abbildung 6 zeigt die Auswirkungen von n+-Pocket auf die Leistung des TGTFET. Das Ich AUS steigt mit zunehmender n+-Taschen-Dotierungskonzentration schnell an, wie in Fig. 6a gezeigt. Die niedrigere SS und die größere I EIN kann durch Verringern der Dicke der n+ Tasche (Tp) von 7 auf 3 nm erhalten werden, wenn N P = 5 × 10 18 cm −3 , wie in Abb. 6b gezeigt. Gleichzeitig ist in Fig. 6b kein signifikanter Strom unterhalb der Schwelle angegeben. Aus Fig. 6a kann bestätigt werden, dass eine relativ niedrige Dotierungskonzentration der n+-Tasche dazu beiträgt, den Strom unter der Schwelle zu unterdrücken.

Simulierte Drainströme mit verschiedenen n+ Taschen a Konzentrationen und b Dicken bei V d = 1 V

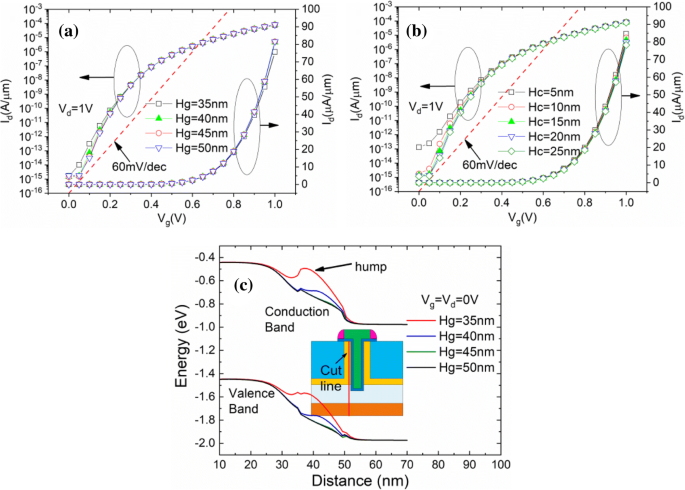

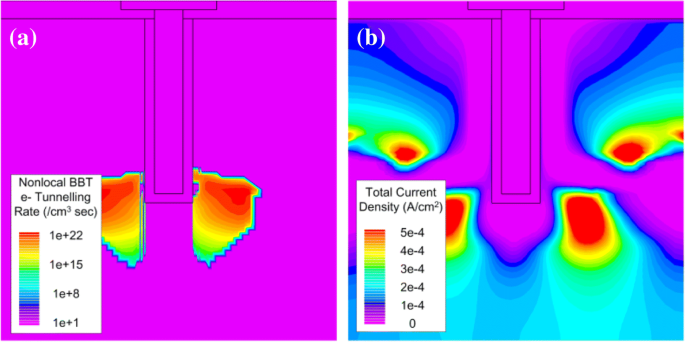

Der Einfluss der Gate-Höhe (Hg) und der Kanaldicke (Hc) ist in Abb. 7a, b separat dargestellt. Ein kleines Ich EIN und SS-Verbesserung tritt auf, wenn Hg ansteigt. Denn bei Hg = 35 nm gibt es einen offensichtlichen Energiebandbuckel auf dem Durchlassstrompfad, der zu einem gewissen Hindernis für die Glückselektronen (Elektronen, die den Tunnelübergang passiert haben) wird, wie in Abb. 7c gezeigt, was zu . führen kann Ich an verkleinern. Wenn Hg ansteigt, wird der Energiebandbuckel geschwächt, was zu einem I . führt EIN und SS-Verbesserung. Ein leichtes Ich EIN eine Verbesserung wird mit abnehmendem Hc erzielt, wie in Fig. 7b gezeigt. Wenn Hc auf 5 nm abfällt, kann jedoch eine starke Verschlechterung der unterschwelligen Charakteristik beobachtet werden. Dies kann durch den zunehmenden Tunnelstrom unter der Schwelle an der Ecke der n+ Tasche erklärt werden, wie in 8 gezeigt. 8a zeigt das offensichtliche Band-zu-Band-Tunneling-Phänomen im ausgeschalteten Zustand, wenn Hc = 5 nm, während 8b zeigt das Ich AUS Stromdichte bei Hc = 5 nm.

Simulierte Übertragungseigenschaften von TGTFET mit a verschiedene Hg, b verschiedene Hc und c der Leitungsbandbuckel auf dem Strompfad

Simulierte Diagramme des Aus-Zustands a BTBT-Elektronentunnelrate und b Stromdichte bei Hc = 5 nm

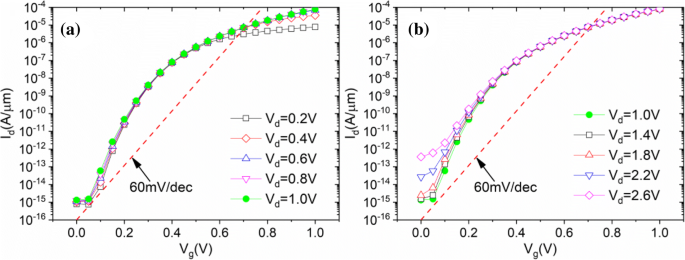

Wie in Abb. 9 gezeigt, ist der Einfluss der Drain-Source-Spannung (V d ) wird in diesem Beitrag ebenfalls berücksichtigt. Für V d < 0,6 V, Ich EIN steigt offensichtlich mit zunehmendem V d , wie in Abb. 9a gezeigt. Dies wird durch die Tatsache erklärt, dass das Potenzial des p-Kanals als Reaktion auf das zunehmende V . langsam wächst d und führt zu einem abnehmenden Widerstand des p-Kanals. Für V d> 1,8 V, gezeigt in Abb. 9b, das I EIN steigt fast nicht mit zunehmendem V d , aber ich AUS nimmt erheblich zu. Dies liegt daran, dass der Tunnelstrom unter der Schwelle an der Ecke der n+-Tasche mit zunehmendem V . schnell ansteigt d . Schließlich für 0,6 V < V d < 1,8 V, TGTFET zeigt eine gute und stabile Leistung. Infolgedessen ist der TGTFET robust gegenüber einer Drain-induzierten Barrieresenkung (DIBL) und weist eine gute und stabile Leistung in einem größeren Dynamikbereich der angelegten Spannung auf.

Simulierte Drainströme für a V d ≤ 1 V und b V d ≥ 1 V

Analog-/HF-Leistung von TGTFET, UTFET und LTFET

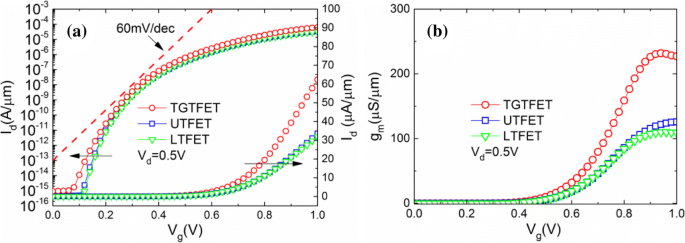

Abbildung 10 zeigt die Übertragungseigenschaften und Steilheitskurven von TGTFET, UTFET und LTFET bei V d = 0,5 V. Die Steilheit (g m ) lässt sich aus der ersten Ableitung der Übertragungskennlinie nach Gl. (1) [27,28,29]:

$$ {g}_{\mathrm{m}}={dI}_{\mathrm{d}s}/{dV}_{\mathrm{gs}} $$ (1)

a Übertragungseigenschaften und b Transkonduktanzkurven von TGTFET, UTFET und LTFET bei V d = 0,5 V

Infolgedessen ist die maximale Transkonduktanz von TGTFET (232 μS/μm) etwa doppelt so groß wie die von UTFET (120 μS/μm) und LTFET (110 μS/μm), wie in Abb. 10 gezeigt. Dies wird von . profitiert die Stromverstärkung, die durch die duale Source- und Gate-Überlappung beigetragen wird.

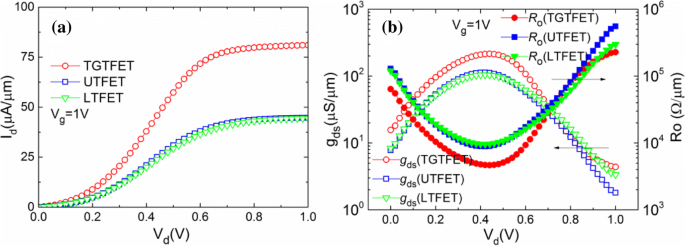

Abbildung 11 zeigt die Ausgangseigenschaften, die Ausgangsleitfähigkeit (g ds ) und Ausgangsimpedanz (R o ) Kurven des TGTFET, UTFET und LTFET. Wie in Abb. 11a gezeigt, ist deutlich zu erkennen, dass der Ausgangsstrom des Geräts mit der Zunahme von V . ansteigt d , aber wenn V d über 0,6 V erreicht, neigt der Ausgangsstrom zur Sättigung. Durch Beobachtung lässt sich leicht feststellen, dass der Ausgangsstrom von TGTFET doppelt so hoch ist wie der von UTFET und LTFET. Abbildung 11b zeigt die Ausgangsleitfähigkeit (g ds ) und Ausgangsimpedanz (R o ) Kurven des TGTFET, UTFET und LTFET. Die g ds erhält man durch die Ableitung des Ausgangsstroms, wie in Gl. (2) [27, 29] während R o kann als Kehrwert der Ausgangsleitfähigkeit ausgedrückt werden.

$$ {g}_{\mathrm{ds}}={dI}_{\mathrm{ds}}/{dV}_{\mathrm{ds}} $$ (2)

a Ausgangseigenschaften, b Ausgangsleitwert (g ds ) und c Ausgangsimpedanz (R o ) Kurven von TGTFET, UTFET und LTFET

Aufgrund der Vorteile beim Ausgangsstrom gewinnt der TGTFET den höchsten g ds und das minimale R o dieser drei Geräte. Unter einer Gate-Bias-Bedingung von 1 V erreichte der TGTFET das maximale g ds von 214 μS/μm und dem minimalen R o von 4,6 kΩ/μm unter 0,45 V V d . Unter der gleichen Gate-Bias-Bedingung erreichten UTFET und LTFET das maximale g ds von 113 μS/μm und 105 μS/μm und dem minimalen R o von 9,0 kΩ/μm und 9,6 kΩ/μm unter 0,4 V V d .

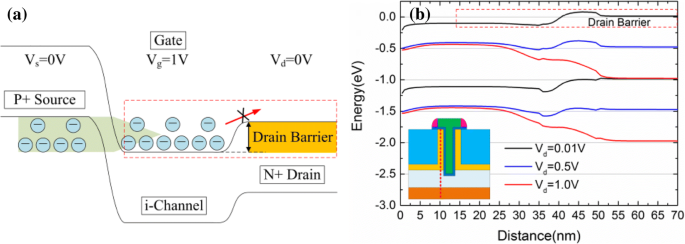

Darüber hinaus ist es in Fig. 11 nicht schwer herauszufinden, dass der lineare Bereich der Geräteausgangscharakteristik eine gewisse Nichtlinearität zeigt. Wie in Abb. 11a gezeigt, R o nimmt zuerst ab und steigt dann mit zunehmendem V d . Einige Forschungsgruppen geben den entsprechenden physikalischen Prozess zu diesem Phänomen an [7, 30], aber es gibt noch einige Probleme, die nicht klar erklärt wurden. Wie wir wissen, R o wird durch den Widerstand des Kanalgebiets und des Tunnelübergangs bestimmt. Wenn V d < 0,4 V, R o nimmt mit zunehmendem V ab d . Betrachten Sie die folgenden Situationen, wenn V d = 0 V und V g = 1 V, keines der Glückselektronen kann zur Drain-Seite geleitet werden, und fast alle Elektronen werden im Kanalgebiet durch eine relativ hohe Drain-Barriere gefangen, wie im roten gestrichelten Linienrahmen in Abb. 12a, b gezeigt. Wenn 0 V < V d < 0,4 V, mit Zunahme von V d , wird die Abflussbarriere schwächer (wie in Abb. 12b gezeigt). Somit können die im Kanalbereich eingefangenen Elektronen die Drain-Barriere passieren und dann durch den Drain gesammelt werden. Dies ist ein thermischer Anregungsprozess von Elektronen vom Kanal zum Drain. Schließlich, da die Tunnelverbindung vollständig eingeschaltet wurde (wenn V g = 1 V), ist der Tunnelstrom immer im Überschuss und der durch den Tunnelübergang eingeführte Widerstand kann ignoriert werden. Zu diesem Zeitpunkt R o wird bestimmt durch den Kanalwiderstand und R o wird durch den elektronenthermischen Anregungsprozess über die Drain-Barriere entschieden. Also, R o nimmt mit zunehmendem V . ab d . Wenn V d> 0,6 V gelangen diese drei Geräte allmählich in den Sättigungsbereich und R o wird größer. Dies liegt daran, wenn V d groß ist, werden fast alle Elektronen durch den Tunnelübergang durch das relativ hohe elektrische Feld zur Drain-Seite geleitet. Der Tunnelstrom wird zur Grenze des Drainstroms. In diesem Zustand R o wird hauptsächlich durch den Tunnelübergang bestimmt. Die Tunneleffizienz kann jedoch nicht signifikant gesteigert werden, während V d nimmt zu. V d hat einen kleinen Einfluss auf die Energiebandstruktur des Tunnelübergangs (n+-Taschenseite), wie in Abb. 12b gezeigt. Als Ergebnis kann der Tunnelstrom nicht offensichtlich ansteigen und es gibt fast kein I EIN steigen mit dem stetig steigenden V d (wenn V d> 0,6 V), was bedeutet, dass eine Impedanz ansteigt. Außerdem, wenn 0,4 V < V d < 0,6 V, R o wird sowohl durch den Kanalwiderstand als auch durch den Tunnelübergang bestimmt.

a Schematische Darstellung des Energiebandes bei V d = 0 V und V g = 1 V. b Simulationsergebnisse des Energiebanddiagramms bei verschiedenen Bias von V d

Aus der obigen Analyse kann abgeleitet werden, dass der R o des TFET wird sowohl durch den Tunnelprozess als auch durch den thermischen Kanalelektronenanregungsprozess beeinflusst. Die wichtigsten physikalischen Mechanismen können dominieren R o wechselt mit V d Variation. Schließlich die R o nimmt zuerst ab und steigt dann an, wodurch die Nichtlinearität der Ausgangskennlinie verursacht wird. Übrigens ist durch die Beobachtung von Fig. 11b leicht zu erkennen, dass die Ausgangsimpedanz des TGTFET viel kleiner ist als die des UTFET und LTFET. Dies ist auf die bessere Tunneleffizienz zurückzuführen, die sich aus der Dual-Source- und der lateralen Gate-Überlappungsstruktur des TGTFET ergibt.

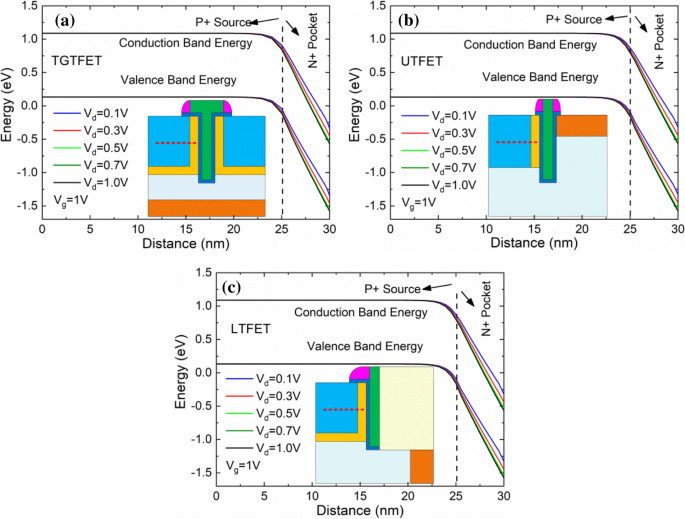

Abbildung 13 zeigt die Energiebandstruktur von TGTFET, UTFET und LTFET mit unterschiedlichen angelegten Spannungen. Die rot gepunkteten Linien im Einschub stellen die Position zum Zeichnen des Energiebands dar (das 15 nm unter der Oberfläche liegt, genau auf der halben Höhe der Quellregion). Es ist zu sehen, dass mit einem V d von 0,1 auf 0,5 V erhöhen, weist die Bandstruktur von TGTFET, UTFET und LTFET einen offensichtlichen Biegetrend auf. Dies liegt daran, dass die Drainspannung das elektrische Potential des Tunnelübergangs nahe der Drainseite herabziehen kann. Dies weist darauf hin, dass für TGTFET, UTFET und LTFET der Anstieg von V d von 0,1 bis 0,5 V ist für die Tunneleffizienz von Vorteil. Wenn jedoch V d> 0.5 V, die Änderung des Energiebandes mit V d Erhöhung ist nicht der Rede wert. Dies stimmt mit den Analyseergebnissen in Abb. 12b überein.

Die Energiebandstruktur von a TGTFET, b UTFET und c LTFET bei V g = 1

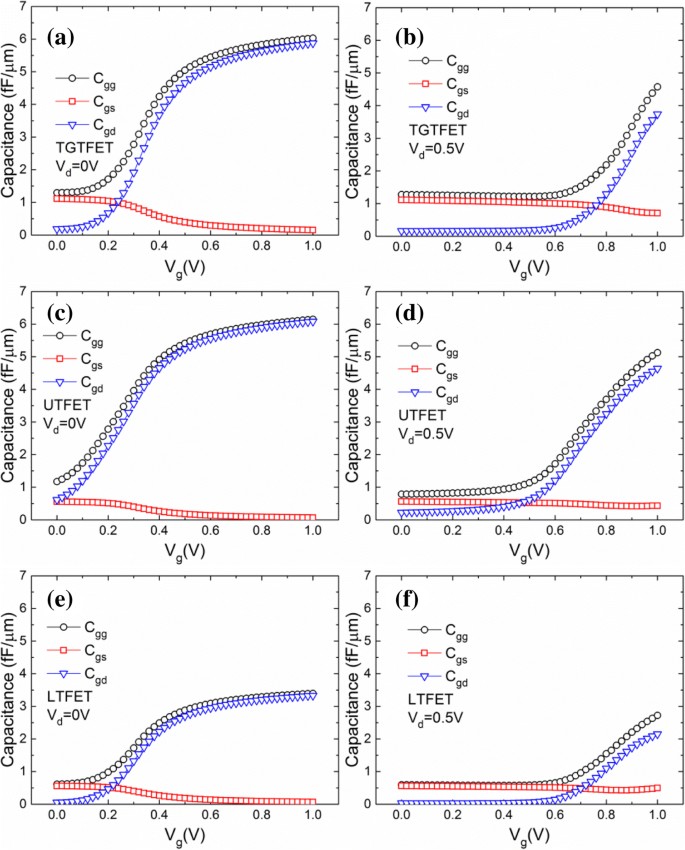

Wie wir wissen, ist die Gate-Kapazität (C gg ) des Geräts kann die Frequenzeigenschaften der integrierten Schaltungen stark beeinflussen. Für TGTFET, UTFET und LTFET, C gg besteht im Allgemeinen aus C gs (Kapazität von Gate zu Source) und C gd (Gate-zu-Drain-Kapazität). Daher ist die Eigenschaft von C gg , C gs , und C gd ist von großer Bedeutung, um die Frequenzeigenschaften und die analoge Anwendungsfähigkeit von Geräten zu bewerten. Insbesondere für TFET unterscheiden sich die Kapazitätseigenschaften stark von MOSFET. Aufgrund des Tunnelübergangs im Sourcebereich hat TFET normalerweise einen kleinen C gs [1, 11]. Daher ist das C gg von TFET wird hauptsächlich durch C . bestimmt gd . Abbildung 14 zeigt die Kapazität von TGTFET, UTFET und LTFET im Vergleich zu V g unter V d = 0,5 V und V d = 0 V, separat.

Kapazität von TGTFET im Vergleich zu V g unter a V d = 0 V und b V d = 0,5 V. Kapazität von UTFET gegenüber V g unter c V d = 0 V und d V d = 0,5 V. Kapazität des LTFET gegenüber V g unter e V d = 0 V und f V d = 0,5 V

Durch die Beobachtung von Abb. 14a, b ist es leicht zu finden, dass das C gs des TGTFET unter 1-V-Gate-Spannung beträgt 0,15 fF/μm bei V d = 0 V und 0,7 fF/μm bei V d = 0,5 V, was viel kleiner ist als das des C gd (5,8 fF/μm bei V d = 0 V und 3,7 fF/μm bei V d = 0,5 V). Somit ist das C gg von TGTFET wird hauptsächlich durch C . bestimmt gd . Wenn V d = 0 V, C gg und C gd schnell mit zunehmendem V . zunehmen g , wie in Abb. 14a gezeigt. Dies liegt daran, dass mit der Zunahme von V g , werden Elektronen an der Gate-Grenzfläche im Gerätekanal aggregiert, wodurch die Kapazität schnell ansteigt. Wenn V d = 0,5 V, C gd steigt offensichtlich nicht bis V g auf mehr als 0,6 V erhöht, wie in Abb. 14b gezeigt. Dies liegt daran, wenn V g niedrig ist, können nur wenige glückliche Elektronen den Tunnelübergang passieren und in den Kanal gelangen. Einige dieser glücklichen Elektronen werden am Rekombinationsprozess teilnehmen, und die meisten anderen werden aufgrund der 0,5-V-Drain-Spannung schnell vom Drain gesammelt. Daher ist es für diese Glückselektronen sehr schwierig, im Gerätekanal zu bleiben. Mit dem V g erhöhen, nimmt die Zahl der Glückselektronen rapide zu. In diesem Moment kann weder der Drain-Sammlungs- noch der Elektron-Loch-Rekombinationsprozess diese glücklichen Elektronen schnell abbauen. Somit steigt die Elektronenkonzentration im Kanal und die Kapazität steigt schnell an. Als Ergebnis neigt die kapazitive Kennlinie dazu, sich nach rechts zu verschieben, während V d erhöht, wie in Abb. 14a, b gezeigt. Die obige Analyse und die obigen Phänomene sind auch auf UTFET und LTFET anwendbar, wie in Abb. 14c–f gezeigt. Darüber hinaus beträgt die Gate-Kapazität des UTFET bei 0 V und 0,5 V V d erreichte 6,2 fF/μm bzw. 5,1 fF/μm und die des LTFET erreichte 3,4 fF/μm bzw. 2,7 fF/μm.

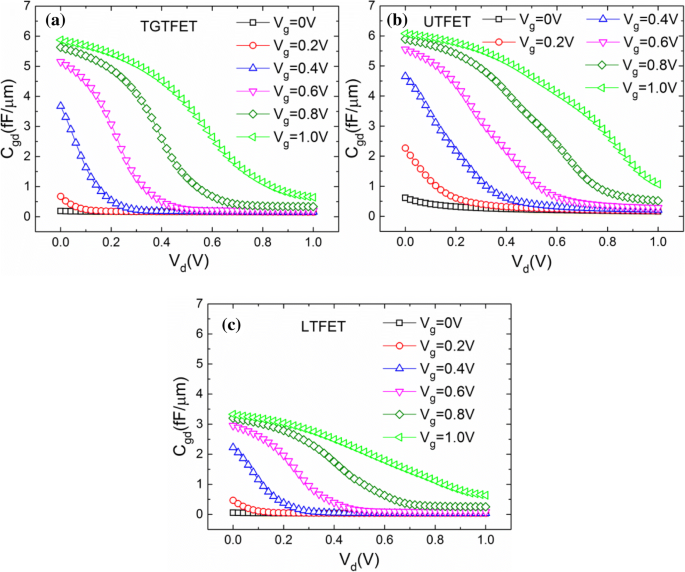

Da es keine direkte Überlappung zwischen Gate und Drain des LTFET gibt und der Abstand zwischen Gate und Drain relativ groß ist, hat der LTFET die besten Kapazitätseigenschaften und das kleinste C gg . Im Gegensatz dazu gibt es eine direkte Überlappung zwischen Gate und Drain des UTFET. Daher werden Elektronen in der Nähe der Drain-Seite leichter durch das Gate kontrolliert, was zu einem großen C . führt gg von UTFET. Bei TGTFET ist der Abstand zwischen Gate und Drain zwar gering, aber es gibt einen leicht dotierten Kanalbereich, der Gate und Drain isolieren kann. Somit ist die Kapazität des TGTFET besser als die des UTFET, aber etwas schlechter als die des LTFET. Abbildung 15 zeigt das C gd Eigenschaften von TGTFET, UTFET und LTFET gegenüber V d unter verschiedenen V g . Aus der Beobachtung von Abb. 15a–v ist nicht schwer zu erkennen, dass das C gd Die Eigenschaften dieser drei Geräte sind ähnlich. Das heißt, für ein festes V g , C gd nimmt mit der Zunahme des V . ab d . Andererseits für ein festes V d , C gd steigt mit der Zunahme von V g .

C gd Eigenschaften von a TGTFET, b UTFET und c LTFET im Vergleich zu V d unter verschiedenen V g

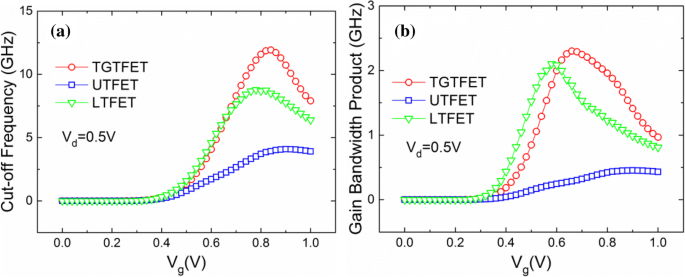

Wie wir wissen, sind sowohl die Grenzfrequenz (f T ) und Verstärkungsbandbreite (GBW) sind die Bewertungskriterien für die Bewertung der Frequenzeigenschaften von Geräten. f T hängt vom Verhältnis von g . ab m zu C gg , wie in Gl. (3) [30, 31]. Bei einer bestimmten DC-Verstärkung von 10 kann GBW durch das Verhältnis von g . ausgedrückt werden m zu C gd , wie in Gl. (4) [17]:

$$ {f}_T=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gs}}\sqrt{1+2{C}_{\mathrm{gd} }/{C}_{\mathrm{gs}}}}\approx \frac{g_{\mathrm{m}}}{2\pi \left({C}_{\mathrm{gs}}+{C }_{\mathrm{gd}}\right)}=\frac{g_{\mathrm{m}}}{2\pi {C}_{\mathrm{gg}}} $$ (3) $$ \ mathrm{GWB}={g}_{\mathrm{m}}/2\pi 10{C}_{\mathrm{gd}} $$ (4)Abbildung 16 zeigt die Kennlinien des f T und GBW von TGTFET, UTFET und LTFET. Dank der strukturellen Vorteile, wie der Überlappung von Dual-Source und lateralem Gate, die durch das T-förmige Gate eingeführt wird, erzielt TGTFET die herausragendsten Frequenzeigenschaften im Vergleich zu UTFET und LTFET. Unter der Bedingung V d = 0,5 V, die f T und GBW von TGTFET erreichten die Maximalwerte von 11,9 GHz bzw. 2,3 GHz. Der LTFET profitiert vom großen Abstand zwischen Gate und Drain und ohne Gate/Drain-Überlappung und erreicht einen kleinen C gg und gute Frequenzeigenschaften. Die f T und GBW von LTFET erreichen die 8,7 GHz und 2,1 GHz separat. Die Kapazitätseigenschaften von UTFET sind im Vergleich zu denen von TGTFET und LTFET schlechter. Dies liegt daran, dass sich das direkte Gate/Drain überlappt. Als Ergebnis ist der Maximalwert von f T and GBW of UTFET can only reach 4.1 GHz and 0.5 GHz separately.

The characteristic curves of a f T und b GBW of TGTFET, UTFET, and LTFET versus V g at V d = 0.5 V

Schlussfolgerungen

In this paper, a T-shape gate dual-source tunnel field-effect transistor (TGTFET) with good performance is proposed and investigated. The structure, mechanism, and the influence of device parameter on the characteristic of TGTFET are discussed. In addition, the characteristics of TGTFET, UTFET, and LTFET are discussed and compared in this paper. The dual-source regions are introduced to double the area of the tunneling junction. The gate overlap and the n+ pockets can obviously enhance the tunneling efficiency of the tunneling junction in TGTFET. Finally, the TGTFET with impressive characteristics (I ON = 8.1 × 10 −5 A/μm, I ON /Ich OFF = 6.7 × 10 10 and SSmin = 24.4 mV/dec) is obtained. At the same time, TGTFET is robust to DIBL, which means TGTFET can exhibit a good and stable performance in a larger applied voltage dynamic range. Furthermore, the analog/RF performance of TGTFET is studied and compared with UTFET and LTFET. The key parameter such as input/output characteristics, capacitance characteristics, GBW, and f T are analyzed. Benefiting from the no direct overlap between the gate and drain, TGTFET obtains a relatively small C gd und C gg . Finally, TGTFET with remarkable frequency characteristics (f T = 11.9 GHz and GBW = 2.3 GHz) is obtained. As a conclusion, it is expected that TGTFET can be one of the promising alternatives for the next generation of device in low-power and analog/RF applications.

Abkürzungen

- C gd :

-

Gate to drain capacitance

- C gs :

-

Gate to source capacitance

- f T :

-

Cut-off frequency

- GBW:

-

Gain bandwidth

- g ds :

-

Output conductance

- g m :

-

Transconductance

- Hc:

-

Height of the channel layer

- Hg:

-

Height of the gate electrode

- Hs:

-

Height of the source layer

- LTFET:

-

L-shape gate tunnel field-effect transistor

- N D :

-

Doping concentration of n+ drain

- N P :

-

Doping concentration of n+ pocket

- N S :

-

Doping concentration of p+ source

- N sub :

-

Doping concentration of p− substrate

- R o :

-

Output impedance

- TGTFET:

-

T-shape gate dual-source tunnel field-effect transistor

- Tox:

-

Thickness of the HfO2 gate dielectric

- Tp:

-

Thickness of n+ pocket

- UTFET:

-

U-shape gate tunnel field-effect transistor

- V d :

-

Drain to source voltage

- V g :

-

Gate to source voltage

- Wg:

-

Width of the gate electrode

Nanomaterialien

- Transistoren, Sperrschicht-Feldeffekt (JFET)

- Transistoren, Feldeffekt mit isoliertem Gate (IGFET oder MOSFET)

- Übergangs-Feldeffekttransistoren

- Feldeffekttransistoren mit isoliertem Gate (MOSFET)

- Der Sperrschicht-Feldeffekttransistor (JFET) als Schalter

- Tunnel

- Weltweit erster ultraschneller volloptischer Raumtemperaturtransistor

- Durch sichtbares Licht angetriebene photokatalytische Leistung von N-dotierten ZnO/g-C3N4-Nanokompositen

- Herstellung und photokatalytische Leistung von Hohlstruktur-LiNb3O8-Photokatalysatoren

- Ein neuartiger Bi4Ti3O12/Ag3PO4-Heteroübergang-Photokatalysator mit verbesserter photokatalytischer Leistung