Hochleistungsfähige zweidimensionale InSe-Feldeffekttransistoren mit neuartigem Sandwich-Ohmkontakt für Sub-10-nm-Knoten:eine theoretische Studie

Zusammenfassung

Zweidimensionale (2D) InSe-basierte Feldeffekttransistoren (FET) haben in experimentellen Berichten eine bemerkenswerte Ladungsträgermobilität und ein hohes Ein-Aus-Verhältnis gezeigt. Theoretische Untersuchungen zeigten auch, dass die hohe Leistung bei Knoten unter 10 nm im ballistischen Grenzbereich gut erhalten bleiben kann. Sowohl experimentelle Erfahrungen als auch theoretische Berechnungen haben jedoch gezeigt, dass die Erzielung einer hochwertigen ohmschen Leistung zum wichtigsten limitierenden Faktor für leistungsstarke 2D-FETs geworden ist. In dieser Arbeit schlugen wir einen neuen Sandwich-Ohmkontakt mit Indium für InSe-FET vor und bewerteten seine Leistung umfassend aus Sicht des Materials und der Vorrichtung basierend auf Ab-initio-Methoden. Die Materialeigenschaften zeigen, dass alle grundlegenden Probleme des ohmschen Kontakts, einschließlich der Tunnelbarriere, der Schottky-Barriere und der effektiven Dotierung, durch die Einführung der Sandwichstruktur gut berücksichtigt werden und ein ausgezeichneter Kontaktwiderstand erreicht wurde. Auf dem Leistungsniveau der Bauelemente wurden Bauelemente mit Gate-Längen von 7, 5 und 3 nm untersucht. Alle Metriken von sandwichartig kontaktierten Bauelementen übertreffen bei weitem die Anforderungen der International Technology Roadmap for Semiconductors (ITRS) und weisen eine deutliche Förderung im Vergleich zu herkömmlichen Strukturen auf. Die maximale Stromerhöhung mit 69,4 %, 50 % und 49 % wird für Bauelemente mit 7, 5 bzw. 3 nm Gatelänge erreicht. Inzwischen wird die maximale Reduzierung der intrinsischen Verzögerung mit 20,4 %, 16,7 % und 18,9 % erreicht. Darüber hinaus wird ein Benchmark des Energieverzögerungsprodukts (EDP) im Vergleich zu anderen 2D-FETs präsentiert. Alle InSe-FETs mit Sandwich-Ohmkontakt übertreffen MoS2 FETs sowie Anforderung von ITRS 2024. Das beste Ergebnis nähert sich der Obergrenze eines idealen BP-FET, was auf ein überlegenes Übergewicht von Sandwichstrukturen für InSe-FETs in der nächsten Generation der komplementären Metalloxid-Halbleiter (CMOS)-Technologie hinweist.

Einführung

Zweidimensionale (2D) Halbleiter haben aufgrund ihrer attraktiven Anwendungen für die nächste Generation der komplementären Metall-Oxid-Halbleiter-(CMOS)-Technologie großes Interesse in elektronischen Geräten geweckt [1, 2]. Ihre ultradünne Dicke und ihre guten dielektrischen Eigenschaften können eine ausgezeichnete elektrostatische Gate-Steuerung bieten, um die wohlbekannten Kurzkanaleffekte zu unterdrücken [3]. Da außerdem nur wenige Schichten von 2D-Materialien normalerweise eine glatte Oberfläche ohne Dangle-Bonds aufweisen, kann die Überlegenheit der Trägermobilität von 2D-Materialien in ultradünnen Körpersystemen im Vergleich zu herkömmlichen Halbleitern gut erhalten bleiben [4]. Mit Ausnahme des lückenlosen Graphens besitzen die meisten synthetisierten 2D-Halbleiter wie Übergangsmetalldichalkogenide (TMDs), schwarzer Phosphor (BP) und Indiumselenid (InSe) eine Bandlücke ungleich null und haben sich als geeignet für Feldeffekttransistoren (FET .) erwiesen ). TMD-basierte FETs haben ein hohes Ein-Aus-Verhältnis von bis zu 10 8 . gezeigt und niedriger Leckstrom in Kurzkanalgeräten, die von der hohen effektiven Masse profitieren [5]. FETs auf BP-Basis weisen aufgrund der hohen Mobilität von ~ 1000 cm 2 . hervorragende Strom- und Schalteigenschaften auf [6] /V s und anisotrope Transporteigenschaft [7]. Kürzlich wurde gezeigt, dass InSe eine überlegene Mobilität von ~ 2000 cm 2 . aufweist /V s bei Raumtemperatur [8, 9] und FET auf InSe-Basis zeigte ein hohes Ein-Aus-Verhältnis von 10 8 [10]. First-Principle-Rechnungen ergaben auch, dass InSe-FET im ballistischen Limit gut auf unter 10 nm herunterskaliert werden kann [11, 12]. Aufgrund der Vernachlässigung des Kontaktwiderstands und der Hypothese einer starken Dotierung ist es jedoch in realen Anwendungen immer noch schwierig, sich der theoretischen Grenze zu nähern. Da ein zuverlässiges Dotierungsverfahren und ein Weg zu einem qualitativ hochwertigen ohmschen Kontakt noch immer fehlen, sind FETs auf Basis von 2D-Materialien einschließlich InSe normalerweise Schottky-Barriere-(SB)-FETs [13,14,15,16]. Das SB an den aktiven Gebieten ergibt einen großen Kontaktwiderstand und ein niedriges Dotierungsniveau verschlechtert die Stromdichte weiter. Das Erzielen eines niedrigen Kontaktwiderstands mit ausreichend dotierten aktiven Regionen ist zum wichtigsten limitierenden Faktor für 2D-Material-basierte FETs (2D-FET) geworden, um eine hohe Leistung zu erreichen [17,18,19].

Mit dem Ziel der obigen Probleme haben wir einen neuartigen Sandwich-Ohmkontakt für InSe-FET vorgeschlagen. Als Elektrodenmetall wurde Indium ausgewählt, da neuere experimentelle und theoretische Studien darauf hindeuten, dass Indium ein vielversprechender Kandidat für InSe-FET sein kann, um eine gute Leistung zu erzielen [20,21,22]. Wir haben die ohmsche Kontaktqualität und Leistung von Bauelementen mit Gate-Längen von 7, 5 und 3 nm theoretisch im Rahmen der International Technology Roadmap for Semiconductors 2013 (ITRS) [23] bewertet. Es sei darauf hingewiesen, dass ITRS zwar durch die International Roadmap for Devices and Systems (IRDS) [24] ersetzt wurde, ITRS2013 jedoch einen klaren Skalierungstrend für Transistoren zeigt und in neueren Studien immer noch übernommen wurde [25, 26]. Dieses Manuskript ist wie folgt aufgebaut:Zunächst werden die elektrischen Eigenschaften von Sandwich- und konventionellen (oberen) Kontakten untersucht. Zweitens werden Geräteleistungsmetriken wie der Durchlassstrom und die intrinsische Verzögerung bewertet und mit den Anforderungen von ITRS verglichen. Schließlich wird ein Benchmark des Leistungsverzögerungsprodukts gegenüber der intrinsischen Verzögerung vorgestellt, um ihn mit anderen auf 2D-Materialien basierenden Geräten zu vergleichen.

Methoden

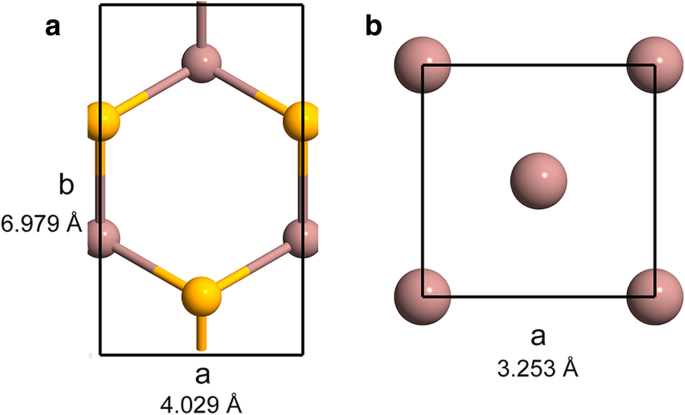

Alle atomaren Strukturen wurden von VASP optimiert [27]; Bei allen Berechnungen wurde ein Energieschnitt von 335 eV verwendet. Die Elementarzelle von InSe wurde mit einem Stresskriterium von 0,01 eV/Å im Rahmen von MetaGGA von SCAN [28] gelockert. Gitterparameter des Metalls Indium wurden dem Handbuch für Chemie und Physik entnommen [29]. Wie in Abb. 1 gezeigt, beträgt die Gitterkonstante von InSe 4.029 , was sehr gut mit experimentellen Berichten übereinstimmt [30, 31].

Draufsicht der Elementarzelle für InSe (a ) und Indium (b ) bzw.

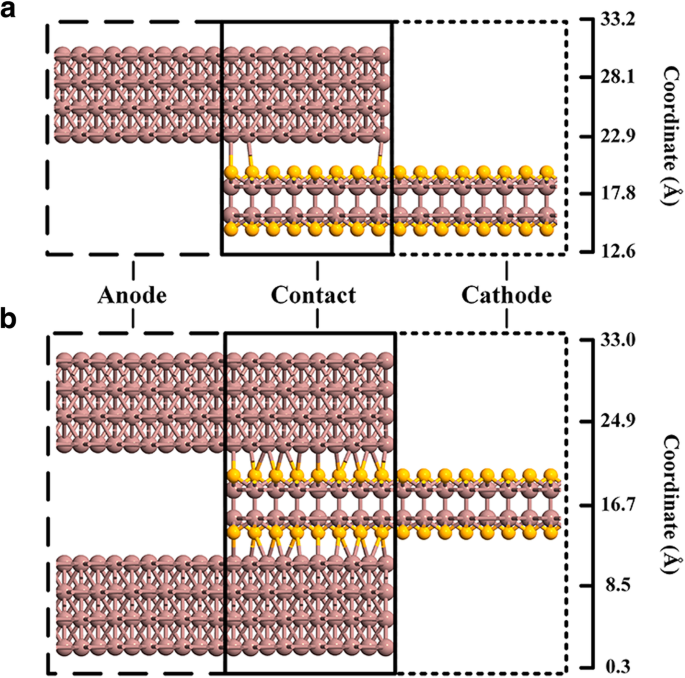

Die ursprüngliche Struktur von Indium auf InSe wurde mit 4 × 1 × 1 und 5 × 2 × 1 Elementarzellen der InSe- bzw. Indium(001)-Oberfläche aufgebaut. Die mittlere absolute Dehnung betrug 1,32%, was ausreichend ist, um die intrinsischen Eigenschaften des Materials zu erhalten. Wie in Fig. 2a, b gezeigt, wurde die Sandwichstruktur mit Indium/InSe/Indium-Schichten aufgebaut, wobei Indium der Unter- und Oberseite spiegelsymmetrisch mit der Mitte von InSe ist. Beide Hybridstrukturen wurden mit dem Van-der-Waals-(vdW)-Funktional von optb88 mit einem Kraftkriterium auf jedes Atom von weniger als 0,02 eV/Å relaxiert [32, 33]. Die Endkontaktfläche beträgt 16,19 × 6,41 . Der Widerstand des ohmschen Kontakts wurde dann durch eine Zwei-Sonden-Vorrichtung bewertet, wie in Fig. 2a, b gezeigt. Um unnötigen Widerstand von Halbleitern außerhalb der Kontaktbereiche zu beseitigen, wurde InSe in der Kathode stark mit 1 × 10 14 . dotiert e/cm 2 sowohl für obere als auch Sandwichkontakte.

Atomare Kontaktstrukturen und zugehörige Zwei-Sonden-Vorrichtung zur Bewertung des Kontaktwiderstands. a , b sind für Top- bzw. Sandwich-Kontakte. Die Koordinaten bezeichnen die Lage der Atome in Richtung außerhalb der Ebene

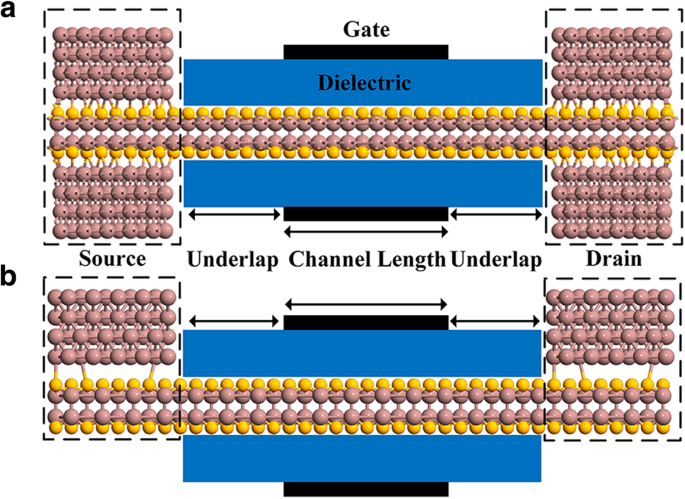

Was die Bewertung der Geräteleistung betrifft, so ist die Geometrie des InSe-FET mit Sandwich- und oberen ohmschen Kontakten in Fig. 3a bzw. b gezeigt. Alle Geräte- und Knotennamen folgen den Anforderungen von ITRS bzw. IRDS. Die Geräteparameter sind in Tabelle 1 aufgelistet. Um das Intraband-Tunneln zu unterdrücken, wurde 1 nm Unterlappung (UL) bei einer Gatelänge von 3 nm angewendet. Im Gegensatz zur ohmschen Kontaktmodellierung wurde keines der Teile in Geräten absichtlich dotiert. Die Geräte wurden gebaut, indem Source, Drain und Kanal entlang der Transportrichtung zusammengeführt wurden. Der Kanal und seine beiden Grenzflächen mit aktiven Regionen wurden zusätzlich mit fester Source und Drain gelockert. Alle Simulationen basierten auf der Theorie der Nichtgleichgewichts-Green-Funktion (NEGF) und wurden von QuantumATK mit vollständig selbstkonsistenter Berechnung durchgeführt [34,35,36], die normalerweise verwendet wurde, um Transistoren an Sub-10-nm-Knoten zu entwerfen und zu untersuchen [17 , 37,38,39]. Doppelzeta-polarisierte Basissätze wurden mit Mech-Cut-Off von 90 Rydberg verwendet. Das K-Punkt-Netz des Monkhorst-Packs wurde mit einer Dichte von 8/Å −1 . abgetastet × 11/Å −1 × 180/Å −1 . Aus Effizienzgründen wird der parallele konjugierte Gradientenlöser als Poisson-Löser gewählt. Den Strom aller Geräte erhält man dann durch Lösen der Landauer-Büttiker-Formel [40]:

$$ I\left({V}_{\textrm{Bias}}\right)=\frac{2e}{h}\int T\left(E,{V}_L,{V}_R\right)\ left[{f}_{\textrm{R}}\left(E,{V}_R\right)-{f}_L\left(E,{V}_L\right)\right] dE $$

Geometrien von InSe-FETs mit sandwichartiger (a ) und oben (b ) Kontakte

Wo,V Voreingenommenheit ist der Bias und kann erreicht werden durch:V Voreingenommenheit = V R ‐ V L , T (E , V L , V R ) ist der Transmissionskoeffizient von Trägern, f R (E , V R ) und f L (E , V L ) sind die Fermi-Dirac-Verteilungsfunktion für Kathode (Drain) bzw. Anode (Source).

Ergebnisse und Diskussion

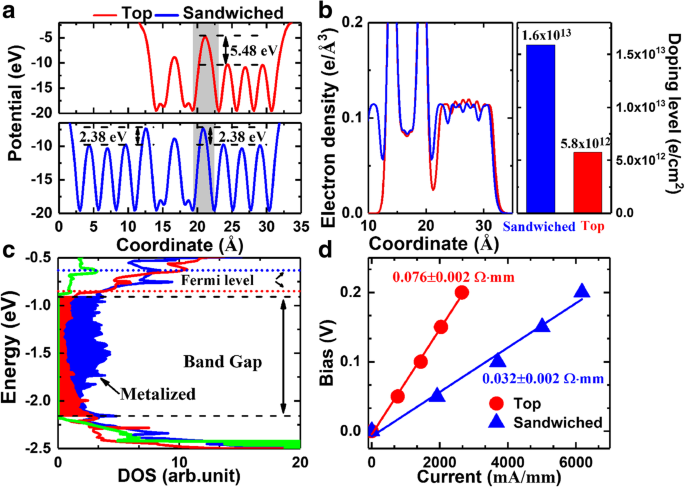

Im Allgemeinen gibt es drei Schlüsselfaktoren, die mit der ohmschen Kontaktqualität in 2D-Materialien korrelieren [18], nämlich die Tunnelbarriere und der Abstand, die aus der vdW-Lücke abgeleitet werden, die Orbitalüberlappung zwischen Elektrode und Halbleiter sowie die SB-Höhe. Zuerst wurden die Tunnelbarriere und der Abstand durch das in Fig. 4a gezeigte effektive Potential beschrieben. Im Vergleich zum oberen Kontakt bietet die Einführung des Sandwichkontakts nicht nur einen zusätzlichen Transportweg an der Unterseite, sondern führt auch zu einer Verringerung der Tunnelbarriere von 5,48 auf 2,38 eV, was zu einer Reduzierung von 56,6% führt. In der Zwischenzeit wird der Grenzflächenabstand mit 0,66 Å ebenfalls leicht verringert, was bedeutet, dass die Breite der Tunnelbarriere ebenfalls verringert wird. Zweitens kann die Orbitalüberlappung anhand der Valenzladungsverteilung in Fig. 4b bewertet werden. Es ist zu bemerken, dass der Sandwichkontakt mehr Valenzelektronen im Grenzflächenbereich besitzt als der obere Kontakt, was auf eine stärkere Orbitalüberlappung zwischen Indium und InSe hinweist. Diese Funktion trägt auch dazu bei, einen Dotierungseffekt in InSe einzuführen, und die Anzahl der überschüssigen Elektronen kann mithilfe der Mulliken-Population berechnet werden. Wir haben die Gesamtzahl der Elektronen in InSe von sandwichartig bzw. von oben kontaktierten Strukturen extrahiert. Dann kann das Dotierungsniveau durch Dividieren der Elektronenzahl durch die Fläche des Kontaktgebiets erhalten werden, da die Nettoladung von isoliertem InSe immer Null sein sollte. Wie im rechten Feld von Fig. 4b gezeigt, ergibt ein Sandwichkontakt ein sehr hohes Dotierungsniveau von 1,6 × 10 13 . e/cm 2 , die fast 2,8-mal höher ist als die des oberen Kontakts. Ein so hohes Niveau hat sich in Simulationen von 2D-Tunnel-FETs, die normalerweise ein viel stärkeres Dotierungsniveau als Metalloxid-Halbleiter-FETs aufweisen, der Hypothese genähert. Drittens ist die Zustandsdichte (DOS) von InSe in unberührten, sandwichartig angeordneten und von oben kontaktierten Strukturen in Abb. 4c gezeigt. Orbitale Überlappung zwischen Indium und InSe an der Grenzflächenregion metallisierte die Bandlücke von InSe, und ein Sandwich führt zu einem höheren Niveau. Dieses Merkmal verbessert die Ladungsträgerinjektion durch die vdW-Tunnelbarriere im Grenzflächenbereich erheblich, da die metallisierten Zustände in der Bandlücke zusätzliche Tunnelkanäle bieten. Darüber hinaus liegen die Fermi-Niveaus oberhalb des Leitungsbandminimums, was zu einer Energieentartung von ~ 0.07 bzw. 0.27 eV für obere bzw. Sandwich-Kontakte führt. Daher werden die SB zwischen Indium und InSe vollständig eliminiert. Viertens wurde der ohmsche Kontaktwiderstand basierend auf der Vorspannungsstromkurve berechnet, die von den Zwei-Sonden-Vorrichtungen erhalten wurde, und alle Ergebnisse sind in Fig. 4d gezeigt. Wir können feststellen, dass beide Kontakte aufgrund der linearen Entwicklungen ohmsch sind. Auf theoretischer Ebene, d. h. unter Vernachlässigung von Oberflächenrauheit, Grenzflächenverunreinigungen usw., führt die Sandwichstruktur zu einem sehr niedrigen Kontaktwert von 0,032 ± 0,002 mm, was den Widerstand des oberen Kontakts mehr als halbiert. Basierend auf den obigen Diskussionen ist es interessant festzustellen, dass die doppelte Kontaktregion immer zu einer mehr als doppelten Verbesserung des ohmschen Kontakts führt. Da der obere Kontakt mit Indium kürzlich experimentell bestätigt wurde, um die Leistung von InSe-basierten Bauelementen zu steigern [21, 22], kann die Sandwichstruktur eine attraktive ohmsche Kontaktlösung für InSe-FETs sein.

a Wirkpotential senkrecht zur Transportrichtung. Die Koordinate entspricht der Lage der Atome und ist in Abb. 1 definiert. Die dunklen Bereiche entsprechen der vdW-Lücke. b Ebenengemittelte Elektronenverteilung senkrecht zur Transportrichtung. Das rechte Panel ist das Dopingniveau. Die Koordinate entspricht der Lage der Atome und ist in Abb. 1 definiert. c DOS von InSe. Das Grün entspricht dem unberührten InSe. d Stromabhängige Vorspannung der beiden Sondenvorrichtungen. Alle Rot und Blau entsprechen den oberen bzw. Sandwichkontakten

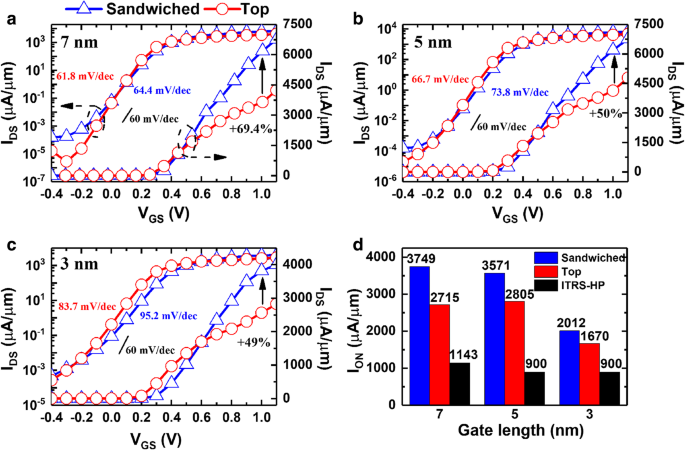

Dann wurde die Geräteleistung bewertet, und die Übertragungseigenschaften des InSe-FET an den Knoten 2019, 2021 und 2024 wurden in Abb. 5 gezeigt , und SS am Knoten 2019 zeigen nahezu ideale Schalteigenschaften von 61,8 bzw. 64,4 mV/dec für Top- bzw. Sandwich-Kontaktierte, was auf eine hervorragende elektrostatische Kontrolle in InSe-FETs hinweist. Darüber hinaus führen Sandwichkontakte zu einer deutlichen Verbesserung des IDS . im Vergleich zu den Top-Knoten mit einer maximalen Steigerung von 69,4 %, 50 % bzw. 49 % bei den Knoten 2019, 2021 und 2024. Außerdem bin ichON wurde nach der Anforderung von High Performance (HP) im ITRS extrahiert. Wie in Fig. 5d gezeigt, ist ION aller Systeme liegt weit über der HP-Anforderung. Im Vergleich zu Geräten mit Top-Kontakt bieten Sandwichsysteme immer noch eine Förderung von 38,2 %, 27,3 % bzw. 20,5 % für die Knoten 2019, 2021 und 2024.

Übertragungseigenschaften von InSe-FETs am Knoten. a 2019, b 2021 und c 2024-Knoten bzw. d Vergleiche von ION gemäß HP-Anforderung von ITRS

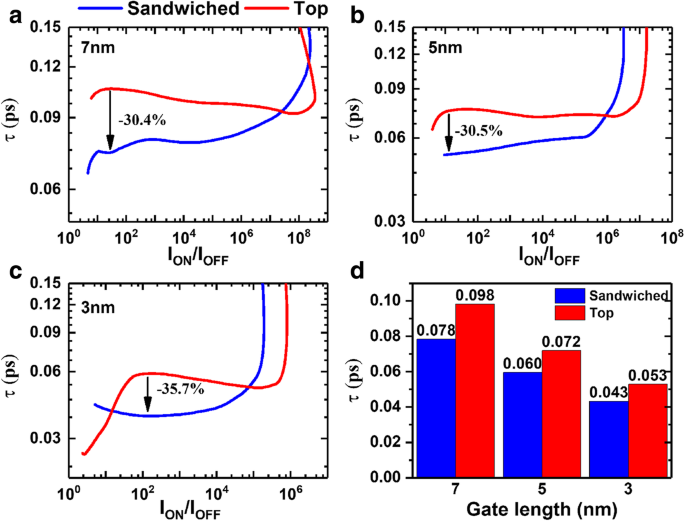

Eine weitere wesentliche Metrik von FETs ist die intrinsische Verzögerung (τ), die die Obergrenze der Schaltgeschwindigkeit in der logischen Schaltung angibt. Das τ wurde von τ . erhalten = (QON − QOFF )/ION , wobei QON und QOFF sind Ladungen im Ein- bzw. Aus-Zustand. Die Ein- und Aus-Zustände sind auf |VDS . beschränkt |=0,68, 0,64 und 0,64 V für die Knoten 2019, 2021 und 2024. Die intrinsische Verzögerung als Funktion des Ein-Aus-Verhältnisses ist in Abb. 6 dargestellt. Trotz der nicht monotonen Entwicklung bei großer Verzögerung, die aus dem Tunneln bei niedrigen Gatespannungen abgeleitet wird [41], liegen alle Verzögerungen unter 0,15 ps und sind ausreichend niedriger als die ITRS-Anforderung von 0,44-0,46 ps. Darüber hinaus führen sandwichartig kontaktierte Bauelemente zu einer Reduzierung von mehr als 30 % in Bereichen von ION /IAUS ≤ 10 7 , 10 6 , 10 5 für die Knoten 2019, 2021 und 2024. Auf der Grundlage der in Abb. 6d gezeigten HP-Anforderungen können Sandwich-Kontaktierte die Schaltgeschwindigkeit mit 20,4 %, 16,7 % bzw. 18,9 % für die Knoten 2019, 2021 und 2024 noch steigern.

Eigenverzögerung als Funktion des Ein-Aus-Verhältnisses am Knoten. a 2019, b 2021 und c 2024-Knoten bzw. d Vergleiche der intrinsischen Verzögerung nach HP-Anforderung von ITRS

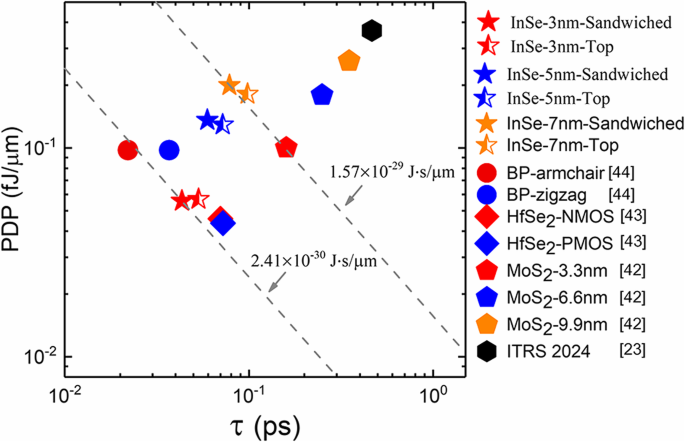

Um die Geräteleistung intuitiver zu bewerten, wird das Leistungsverzögerungsprodukt (PDP) gegenüber der intrinsischen Verzögerung extrahiert. PDP entspricht der Leistungsaufnahme bei einem einzelnen Schaltereignis und ist definiert durch PDP = (QON − QOFF )VDS mit allen Parametern, die aus der HP-Anforderung von ITRS abgeleitet sind. Ergebnisse und Vergleich mit anderen 2D-FETs sind in Abb. 7 dargestellt. Zunächst wurden alle 2D-FETs nach der Regel ausgewählt, dass sie in Versuchsberichten als Transistoren vorläufig verifiziert wurden, was für die CMOS-Technologie noch einen Schritt weiter geht. Zweitens außer InSe und MoS2 [42] wurden alle anderen Bauelemente mit starker Dotierung in aktiven Bereichen und Vernachlässigung des ohmschen Übergangswiderstands simuliert [43, 44], daher entsprechen die Ergebnisse der oberen Leistungsgrenze. Wie zu sehen ist, liegen alle Energieverzögerungsprodukte (EDP) unter den Anforderungen von ITRS 2024, was auf die attraktive Zukunft von 2D-FETs hinweist. Das Maximum an EDP gehört zu MoS2 FET bei 9,9 nm, und das Beste ist von BP FET. Bei InSe-FETs leisten Sandwich-Kontaktierte an allen Knoten immer eine bessere Leistung als oben kontaktierte. Die höchste EDP von sandwichartig kontaktierten Bauelementen liegt bei einer Gate-Länge von 7 nm (2019-Knoten) und übertrifft alle MoS2 FETs. Der niedrigste liegt bei einer Gatelänge von 3 nm (2024 Knoten) und nähert sich in Sesselrichtung sogar der Obergrenze von BP FET, die für die hervorragenden Transporteigenschaften bekannt ist. Dementsprechend zeigt die EDP von InSe-FETs an, dass Sandwich-Kontaktierte Bauelemente eine ausreichende Wettbewerbsfähigkeit zwischen 2D-FETs aufweisen.

Leistungsverzögerungsprodukt gegenüber intrinsischer Verzögerung bestehend aus InSe und anderen 2D-FETs. Die grau gestrichelten Richtlinien entsprechen der spezifischen EDV

Schlussfolgerungen

In dieser Arbeit wurde ein neuer Sandwich-Ohmkontakt mit Indium für InSe-FET vorgeschlagen. Der Sandwich-Ohmkontakt verdoppelt nicht nur den Kontaktbereich, sondern fördert auch die Kontaktqualität um mehr als das Doppelte, was zu einem hervorragenden Kontaktwiderstand führt. Auf dem Leistungsniveau der Bauelemente mit Gate-Längen von 7, 5 und 3 nm bieten InSe-FETs mit Sandwich-Ohmkontakt eine universelle Leistungssteigerung im Vergleich zu herkömmlichen oben kontaktierten Bauelementen. Unter der Anforderung von HP von ITRS werden der Einschaltstrom und die intrinsische Verzögerung um 38,2 ~ 20,5% bzw. 20,4 ~ 16,7% verbessert. Ein EDP-Benchmark mit anderen 2D-FETs zeigt auch, dass InSe-FETs mit Sandwich-Ohmkontakt Vorteile gegenüber anderen 2D-FETs haben. Unsere Studie bietet einen neuen Weg zu Hochleistungs-InSe-FETs.

Verfügbarkeit von Daten und Materialien

Die in der aktuellen Studie verwendeten und/oder analysierten Datensätze sind auf begründete Anfrage beim entsprechenden Autor erhältlich.

Abkürzungen

- 2D:

-

Zweidimensional

- CMOS:

-

Komplementärer Metalloxid-Halbleiter

- TMDs:

-

Übergangsmetalldichalkogenide

- BP:

-

Schwarzer Phosphor

- InSe:

-

Indiumselenid

- FET:

-

Feldeffekttransistoren

- SB:

-

Schottky-Barriere

- 2D-FET:

-

2D-materialbasierter FET

- ITRS:

-

Internationale Technologie-Roadmap für Halbleiter

- vdW:

-

van der Waals

- UL:

-

Unterlappung

- NEGF:

-

Nicht-Gleichgewichts-Green-Funktion

- DOS:

-

Die Zustandsdichte

- SS:

-

Schwung unter der Schwelle

- HP:

-

Hohe Leistung

- τ:

-

Eigenverzögerung

- PDP:

-

Power-Delay-Produkt

- EDV:

-

Energieverzögerungsprodukt

Nanomaterialien

- Luftabstandshalter für 10-nm-Chips

- Nexam versorgt Diab mit eigenschaftenverbesserndem Nexamite für Hochleistungs-PET-Schaum

- Aktivkohlefasern mit hierarchischer Nanostruktur aus Baumwollhandschuhabfällen als Hochleistungselektroden für Superkondensatoren

- Mehrschichtige SnSe-Nanoflake-Feldeffekttransistoren mit niederohmigen Au-Ohm-Kontakten

- Die Untersuchung eines neuartigen, durch Nanopartikel verbesserten wurmähnlichen Mizellensystems

- Entwicklung der Kontaktfläche bei Normallast für raue Oberflächen:von atomaren zu makroskopischen Skalen

- Atomschichtabscheidung von Indiumoxid-Nanoschichten für Dünnschichttransistoren

- Zweidimensionale mesoporöse VO2-Mikroarrays für Hochleistungs-Superkondensatoren

- Einwandige Kohlenstoff-Nanoröhrchen-dominierte mikrometerbreite Streifenmusterbasierte ferroelektrische Feldeffekttransistoren mit HfO2-Defektkontrollschicht

- Eine neuartige Nanocone-Cluster-Mikrostruktur mit Antireflexions- und superhydrophoben Eigenschaften für Photovoltaikanlagen