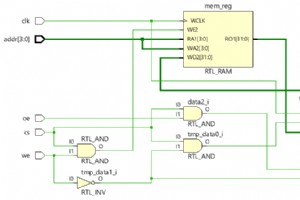

Gestaltung module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe );

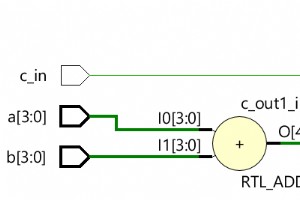

Ein Addierer ist eine digitale Komponente, die die Addition von zwei Zahlen durchführt. Es ist die Hauptkomponente innerhalb einer ALU eines Prozessors und wird zum Inkrementieren von Adressen, Tabellenindizes, Pufferzeigern und an vielen anderen Stellen verwendet, an denen eine Addition erforderlic

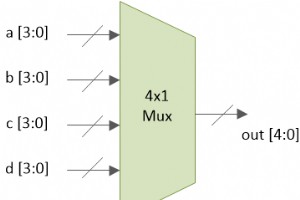

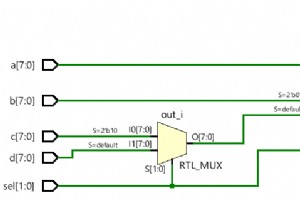

Was ist ein Mux oder Multiplexer? Ein Multiplexer oder mux kurz gesagt, ist ein digitales Element, das basierend auf dem Auswahlsignal Daten von einem der N Eingänge zum Ausgang überträgt. Der unten gezeigte Fall ist, wenn N gleich 4 ist. Zum Beispiel hätte ein 4-Bit-Multiplexer N Eingänge mit jewe

Gestaltung module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; e

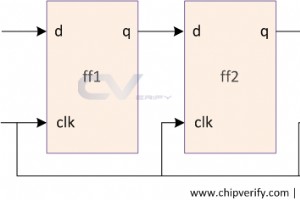

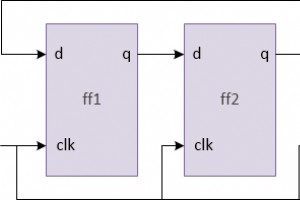

In der Digitalelektronik ein Schieberegister ist eine Kaskade von Flipflops, bei denen der Ausgangspin q eines Flops ist mit dem Dateneingangspin (d) des nächsten verbunden. Da alle Flops mit demselben Takt arbeiten, verschiebt sich das im Schieberegister gespeicherte Bit-Array um eine Position. Wen

Gestaltung module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (i

Gestaltung module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else

Gestaltung module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i

Gestaltung module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+

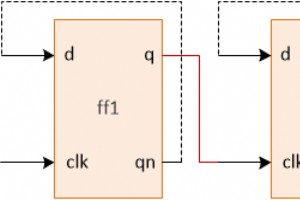

Eine Welle Zähler ist ein asynchroner Zähler, bei dem alle Flops außer dem ersten vom Ausgang des vorhergehenden Flops getaktet werden. Gestaltung module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (

Der 4-Bit-Zähler beginnt von 4b0000 bis 4h1111 zu inkrementieren und springt dann zurück auf 4b0000. Es zählt weiter, solange es mit einer laufenden Uhr versehen ist und Reset hoch gehalten wird. Der Rollover findet statt, wenn das signifikanteste Bit der letzten Addition verworfen wird. Wenn der Z

Ein Flip-Flop erfasst Daten an seinem Eingang an der positiven oder negativen Flanke einer Uhr. Es ist wichtig zu beachten, dass alles, was mit den Daten nach der Taktflanke bis zur nächsten Taktflanke passiert, nicht in der Ausgabe widergespiegelt wird. Ein Riegel erfasst andererseits nicht an der

Gestaltung module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule Testbench module tb; reg clk;

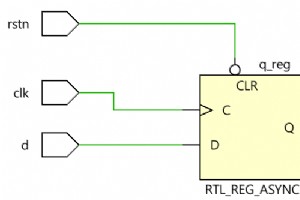

Ein D-Flipflop ist ein sequentielles Element, das dem Eingangspin d folgt am gegebenen Rand einer Uhr. Design Nr. 1:Mit asynchronem Active-Low-Reset module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn)

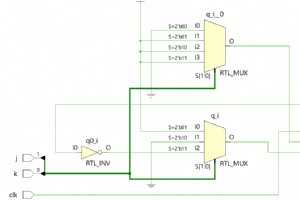

Gestaltung module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule

Es ist immer am besten, mit einem sehr einfachen Beispiel zu beginnen, und keines erfüllt den Zweck am besten, außer Hello World !. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some f

Verilog hat Systemaufgaben und Funktionen, die Dateien öffnen, Werte in Dateien ausgeben, Werte aus Dateien lesen und in andere Variablen laden und Dateien schließen können. Öffnen und Schließen von Dateien module tb; // Declare a variable to store the file handler integer fd; initial begi

Standardzeitskala Obwohl von Verilog-Modulen erwartet wird, dass vor dem Modul eine Zeitskala definiert wird, können Simulatoren eine Standardzeitskala einfügen. Die tatsächliche Zeitskala, die auf jeden Bereich in einer von Verilog ausgearbeiteten Hierarchie angewendet wird, kann mit der Systemauf

Die Verilog-Zeitskalendirektive spezifiziert Zeiteinheit und Genauigkeit für Simulationen. Verilog $timeformat Systemfunktion spezifiziert %t Berichtsstil für Formatbezeichner in Anzeigeanweisungen wie $display und $strobe . Syntax $timeformat(<unit_number>, <precision>, <suffix

Verilog-Mathematikfunktionen können anstelle von konstanten Ausdrücken verwendet werden und unterstützen sowohl Integer und echt Mathematik. Ganzzahlige mathematische Funktionen Die Funktion $clog2 gibt die Obergrenze von log2 zurück des gegebenen Arguments. Dies wird normalerweise verwendet, um d

Verilog