VHDL hat einen eingebauten Pseudozufallsgenerator, kann aber nur Gleitkommazahlen zwischen 0 und 1 erzeugen. Glücklicherweise können Sie daraus jedes andere zufällige Datenformat ableiten, das Sie benötigen. Lesen Sie diesen Artikel weiter, um herauszufinden, wie Sie real herstellen oder integer Wer

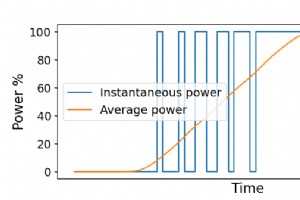

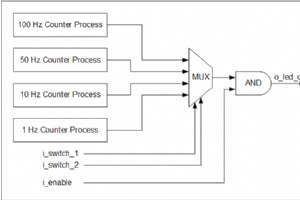

Pulsweitenmodulation (PWM) ist eine effiziente Möglichkeit, analoge Elektronik von rein digitalen FPGA-Pins aus zu steuern. Anstatt zu versuchen, die analoge Spannung zu regulieren, schaltet PWM den Versorgungsstrom schnell bei voller Leistung zum analogen Gerät ein und aus. Diese Methode gibt uns e

Mir ist aufgefallen, dass viele der Gadgets, die ich in den letzten Jahren gekauft habe, sich von LED-Blinken zu LED-Atmung verlagert haben. Die meisten elektronischen Spielereien enthalten eine Status-LED, deren Verhalten Aufschluss darüber gibt, was im Inneren des Geräts vor sich geht. Meine elek

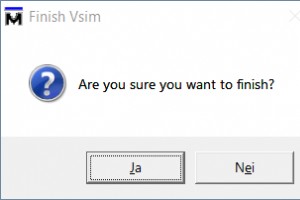

Wie stoppen Sie den VHDL-Simulator, wenn die Simulation abgeschlossen ist? Dazu gibt es mehrere Möglichkeiten. In diesem Artikel untersuchen wir die gängigsten Methoden, um einen erfolgreichen Testbench-Lauf zu beenden. Der hier vorgestellte VHDL-Code ist universell und sollte in jedem leistungsfäh

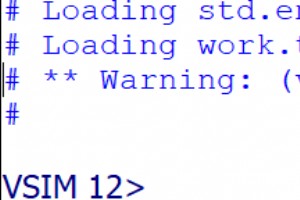

Die meisten VHDL-Simulatoren verwenden die Tool Command Language (Tcl) als Skriptsprache. Wenn Sie einen Befehl in die Konsole des Simulators eingeben, verwenden Sie Tcl. Außerdem können Sie mit Tcl Skripte erstellen, die im Simulator laufen und mit Ihrem VHDL-Code interagieren. In diesem Artikel e

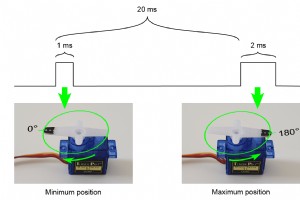

Funkgesteuerte (RC) Modellservos sind winzige Aktuatoren, die typischerweise in Bastlermodellflugzeugen, Autos und Booten verwendet werden. Sie ermöglichen dem Bediener, das Fahrzeug über eine Funkverbindung fernzusteuern. Da es RC-Modelle schon seit langer Zeit gibt, ist die De-facto-Standardschnit

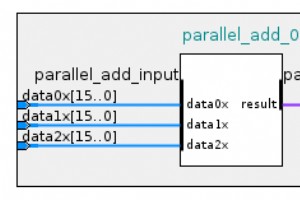

Die Generate-Anweisung in VHDL kann automatisch einen Codeblock in Closures mit identischen Signalen, Prozessen und Instanzen duplizieren. Es ist eine for-Schleife für die Architekturregion, die verkettete Prozesse oder Modulinstanzen erstellen kann. Im Gegensatz zu einer regulären for-Schleife,

Textzeichenfolgen in VHDL sind im Allgemeinen auf Zeichenarrays mit fester Länge beschränkt. Das ist sinnvoll, weil VHDL Hardware beschreibt und Zeichenfolgen generischer Länge dynamischen Speicher benötigen. Um ein String-Array zu definieren, müssen Sie zur Kompilierzeit Speicherplatz für die höch

Dieses Tutorial behandelt die Verwendung des Integrated Logic Analyzer (ILA) und Virtuelle Eingabe/Ausgabe (VIO) Cores zum Debuggen und Überwachen Ihres VHDL-Designs in der Xilinx Vivado IDE. In vielen Fällen müssen Designer eine On-Chip-Verifizierung durchführen. Das heißt, Zugriff auf das Verhalt

Bei der Entwicklung von VHDL für sicherheitskritische FPGA-Anwendungen reicht es nicht aus, nach bestem Wissen und Gewissen Testbenches zu schreiben. Sie müssen nachweisen, dass das Modul bestimmungsgemäß und ohne unerwünschte Nebeneffekte funktioniert. Formale Verifikationstechniken können Ihnen d

VUnit ist eines der beliebtesten Open-Source-VHDL-Verifizierungsframeworks, die heute verfügbar sind. Es kombiniert einen Python-Testsuite-Runner mit einer dedizierten VHDL-Bibliothek, um Ihre Testbenches zu automatisieren. Um Ihnen dieses kostenlose VUnit-Tutorial zu geben, engagiert VHDLwhiz Ah

Wollten Sie schon immer eine VHDL-Simulation ausführen, die einen Quartus-IP-Core über das VUnit-Verifizierungsframework enthält? Das hatte FPGA-Ingenieur Konstantinos Paraskevopoulos im Sinn, konnte aber kein passendes Tutorial dafür finden. Glücklicherweise nutzte er sein Talent, um herauszufinde

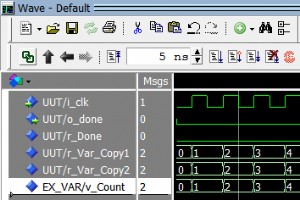

Variablen in VHDL verhalten sich ähnlich wie Variablen in C. Ihr Wert ist genau an der Stelle im Code gültig, an der die Variable geändert wird. Wenn also ein Signal den Wert der Variablen vorher verwendet die Zuweisung, hat sie den alten Variablenwert. Wenn ein Signal den Wert der Variablen after v

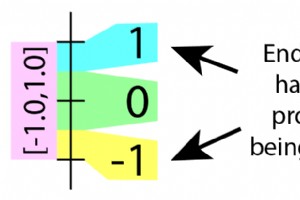

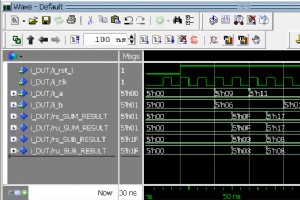

Alle Digital Designer müssen verstehen, wie Mathematik in einem FPGA oder ASIC funktioniert. Der erste Schritt dazu ist zu verstehen, wie signierte und unsignierte Signaltypen funktionieren. Vorzeichenbehaftete und unsignierte Typen existieren in numeric_std Paket, das Teil der ieee-Bibliothek ist.

Das Record-Konstrukt in VHDL kann verwendet werden, um Ihren Code zu vereinfachen. Datensätze ähneln Strukturen in C . Datensätze werden am häufigsten verwendet, um einen neuen VHDL-Typ zu definieren. Dieser neue Typ enthält eine beliebige Gruppe von Signalen, die der Benutzer wünscht. Meistens wird

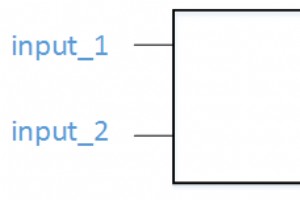

Prozeduren sind Teil einer Gruppe von Strukturen, die Unterprogramme genannt werden. Prozeduren sind kleine Codeabschnitte, die eine Operation ausführen, die im gesamten Code wiederverwendet wird. Dies dient dazu, Code zu bereinigen und Wiederverwendbarkeit zu ermöglichen. Prozeduren können Eingabe

Numeric_Std- und Std_Logic_Arith-Paketdateien verwenden Nachfolgend sind die am häufigsten in VHDL verwendeten Konvertierungen aufgeführt. Die Seite ist in zwei Bereiche aufgeteilt. Die erste Hälfte der Seite zeigt Konvertierungen mit der Numeric_Std-Paketdatei. Die zweite Hälfte der Seite zeigt Ko

Teil 1:Design von VHDL oder Verilog Dieses Tutorial zeigt den Aufbau von VHDL- und Verilog-Code, der eine LED mit einer bestimmten Frequenz blinkt. Sowohl VHDL als auch Verilog werden angezeigt, und Sie können auswählen, was Sie zuerst lernen möchten. Wann immer Designcode geschrieben wird, muss de

VHDL-Prozess oder Verilog Always Blocks verwenden Dieses Tutorial zeigt, wie Sie entweder VHDL- oder Verilog-Blöcke schreiben, die in einem Prozess enthalten sind oder ein Immer blockieren beziehungsweise. Prozesse (in VHDL) und Always Blocks (in Verilog) sind grundlegend und müssen gut verstanden

VHDL ist ein schreckliches Akronym. Es steht für V HSIC H Hardware D Beschreibung L Sprache. Ein Akronym in einem Akronym, genial! VHSIC steht für V ery H hohes S pinkelte ich integriertes C Schaltung. Daher ist VHDL expandiert V ery High Speed Integrated Circuit H Hardware D Beschreibung L Sprach

VHDL