Lateraler, doppelt diffundierter Metall-Oxid-Halbleiter-Transistor mit extrem niedrigem spezifischen On-Widerstand mit verbessertem Dual-Gate und partieller P-vergrabener Schicht

Zusammenfassung

Ein extrem niedriger spezifischer Einschaltwiderstand (R an,sp ) wird in dieser Arbeit ein lateraler doppelt diffundierter Metall-Oxid-Halbleiter-Transistor (LDMOS) mit verbessertem Dual-Gate und partieller P-vergrabener Schicht vorgeschlagen und untersucht. Das analytische On-Widerstandsmodell für den vorgeschlagenen LDMOS wurde erstellt, um einen tiefen Einblick in die Beziehung zwischen dem Widerstand der Driftregion und dem Widerstand der Kanalregion zu geben. Eine N-vergrabene Schicht wird unter die P-Wanne eingefügt, um einen Leitungspfad mit niedrigem Widerstand bereitzustellen und den Widerstand des Kanalbereichs signifikant zu reduzieren. Eine verbesserte Dual-Gate-Struktur wird durch eine N-vergrabene Schicht gebildet, während der vertikale Durchgriffsdurchschlag im ausgeschalteten Zustand vermieden wird. Eine teilweise P-vergrabene Schicht mit optimierter Länge wird unter dem N-Driftbereich verwendet, um den vertikalen Verarmungsbereich zu erweitern und die elektrische Feldspitze im ausgeschalteten Zustand zu entspannen, was die Durchbruchspannung (BV) mit niedrigem Widerstand des Driftbereichs erhöht. Für den LDMOS mit verbessertem Dual-Gate und partieller P-vergrabener Schicht zeigt das Ergebnis, dass R an,sp ist 8,5 mΩ·mm 2 während BV 43 V beträgt.

Hintergrund

Angesichts der steigenden Nachfrage nach komplexeren und schnelleren Logikfunktionen in analogen Leistungs-ICs ist es wichtig, die Leistung des lateralen doppelt diffundierten Metall-Oxid-Halbleiter-Transistors (LDMOS) zu verbessern, insbesondere durch Minimierung des spezifischen Einschaltwiderstands ( R an,sp ) und Maximieren der Durchbruchspannung im ausgeschalteten Zustand (BV) [1,2,3,4,5,6,7,8,9]. Die meisten entwickelten Technologien konzentrieren sich auf die Optimierung der Driftregion, um den Kompromiss von R . zu verbessern an,sp vs. BV für LDMOS-Geräte [10,11,12,13,14,15,16,17,18,19,20]. In unserer vorherigen Arbeit wurde der LDMOS mit ultra-flacher Trench-Isolation (USTI) vorgeschlagen [21]. Die Tiefe und der Eckenwinkel von USTI wurden optimiert, um eine erstklassige Leistung zu erzielen. Für den Niederspannungs-LDMOS verliert die Driftregion jedoch die Dominanz in R an,sp und der Beitrag der Kanalregion kann nicht ignoriert werden.

Methode

In dieser Arbeit wird ein neuartiges LDMOS mit ultraniedrigem spezifischem Durchlasswiderstand mit verbessertem Dual-Gate und partieller P-vergrabener Schicht untersucht. In der numerischen Simulation werden die physikalischen Modelle IMPACT.I, BGN, CONMOB, FLDMOB, SRH und SRFMOB verwendet. Ein analytisches On-Widerstandsmodell wird vorgeschlagen, um einen tiefen Einblick in die Beziehung zwischen dem Widerstand der Driftregion und dem Widerstand der Kanalregion zu geben. Basierend auf dem Modell werden die N-vergrabene Schicht und die teilweise P-vergrabene Schicht optimiert, um ein niedriges R . zu erreichen an,sp und hohe BV.

Ergebnisse und Diskussion

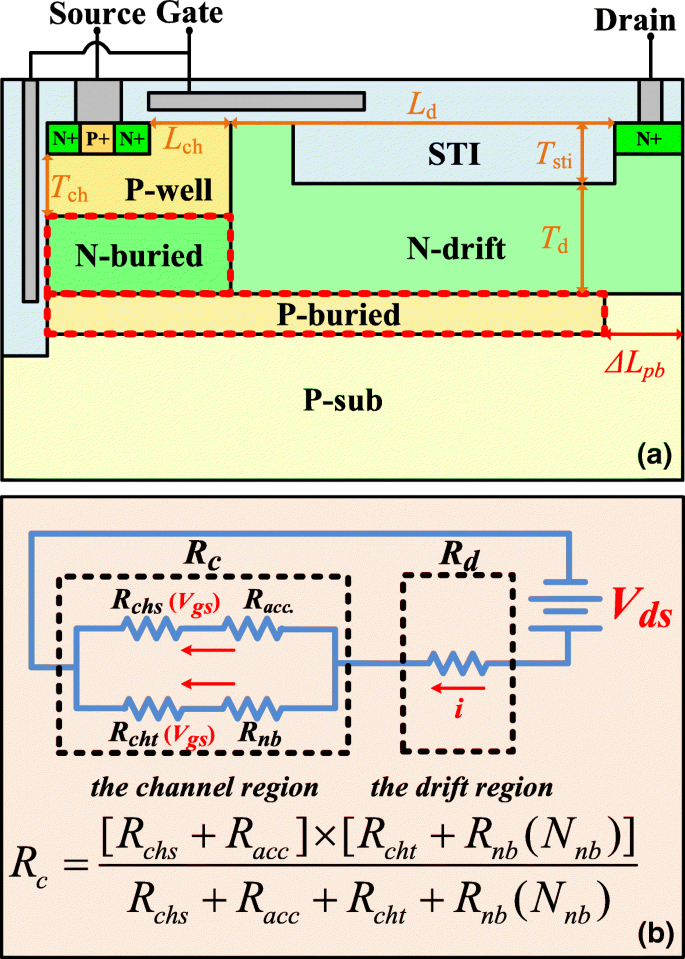

Abbildung 1a zeigt den schematischen Querschnitt eines LDMOS mit extrem niedrigem spezifischem Durchlasswiderstand mit verbessertem Dual-Gate und partieller P-vergrabener Schicht. Der LDMOS verfügt über das Dual-Gate mit N-vergrabener Schicht und die partielle P-vergrabene Schicht, die zur Reduzierung von R . beiträgt an,sp bzw. BV verbessern. Im Kanalbereich wird das verbesserte Dual-Gate durch ein Trench-Gate und eine hochdotierte N-vergrabene Schicht gebildet. Im Vergleich zu einer herkömmlichen Dual-Gate-Struktur reduziert die N-vergrabene Schicht den Widerstand des Kanalgebiets signifikant, indem sie einen leitenden Pfad mit niedrigem Einschaltwiderstand unter der P-Wanne im eingeschalteten Zustand bereitstellt. In der Driftregion wird die partielle P-vergrabene Schicht mit hoher Dotierungskonzentration unter die N-Driftregion eingeführt, um BV zu verbessern, während ein niedriges R . aufrechterhalten wird an,sp . Die partielle P-vergrabene Schicht trägt dazu bei, das vertikale elektrische Feld im ausgeschalteten Zustand zu reduzieren, ohne das Ladungsgleichgewicht in der Driftregion zu brechen. Die Schlüsselgröße des neuartigen Geräts ist in Tabelle 1 aufgeführt.

a Schematische Querschnittsansicht eines LDMOS mit extrem niedrigem spezifischem Durchlasswiderstand mit verbessertem Dual-Gate und partieller P-vergrabener Schicht. b Schematischer äquivalenter Einschaltwiderstand für das vorgeschlagene LDMOS

Abbildung 1b zeigt das schematische äquivalente Ein-Widerstandsmodell für das vorgeschlagene LDMOS. Der gesamte Durchlasswiderstand wird als Widerstand der Driftregion (R d ) und der Widerstand der Kanalregion (R c ) in Serie. In der Kanalregion verläuft der Oberflächenkanal-Leiterweg parallel zum Grabenkanal-Leitweg. Also, R c ist gleich (R chs + R Zusatz )//(R cht + R nb ), wobei R chs , R Zusatz , R cht , und R nb sind die Widerstände des Oberflächen-Gate-Kanals, des Akkumulationsgebiets, des Graben-Gate-Kanals bzw. der N-vergrabenen Schicht. Basierend auf dem vorgeschlagenen On-Resistance-Modell ist die Reduzierung von R c durch Verringerung von R . erreichen würde nb ohne die anderen Leistungen zu beeinträchtigen, da die anderen Widerstände hauptsächlich durch die Prozesstechnologie, die Betriebsspannung und die Schwellenspannung bestimmt werden. Die R d wurde reduziert, indem eine P-vergrabene Schicht unter der N-Drift-Region eingeführt wurde, um den Effekt der Reduzierung des Oberflächenfelds (RESURF) in unserer vorherigen Arbeit zu verstärken. In dieser Arbeit wird die teilweise P-vergrabene Schicht verwendet, um die BV zu verbessern, während das niedrige R . beibehalten wird d .

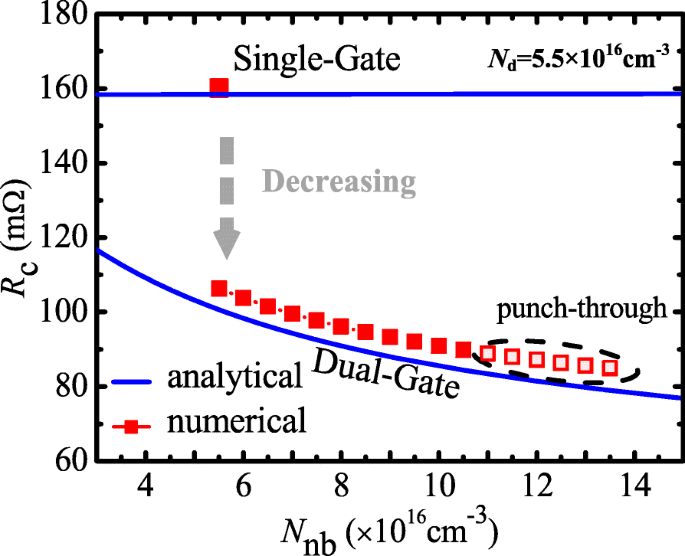

Mit dem Ziel der Reduzierung von R c , wird die N-vergrabene Schicht mit hoher Dotierungskonzentration unter die P-Wanne eingebracht. Abbildung 2 zeigt numerische und analytische R c als Funktionen der Dotierungskonzentration der N-vergrabenen Schicht (N nb ) mit Single-Gate und Dual-Gate. Es wird darauf hingewiesen, dass die Dual-Gate-Struktur dazu beiträgt, R . zu reduzieren c im Vergleich zum Einzeltor. Wenn N nb = N d = 5,5 × 10 16 cm −3 , R c beträgt 110 m². Gemäß dem On-Widerstand-Modell ist R nb ist der Hauptbeitrag zu R c . Und dann die R nb soll abnehmen mit dem Ziel kleinerer R c . Wie in Abb. 2a gezeigt, R c wird mit N . reduziert nb zunehmend. Wenn N nb = 1,35 × 10 17 cm −3 , R c auf 85 m² reduziert. Abb. 2 zeigt jedoch auch, dass N nb durch einen Durchschlagszusammenbruch begrenzt wäre. Aufgrund des Hinzufügens von Trench-Gate, R c wird zunächst um 34 % mit N . verringert nb = N d = 5,5 × 10 16 cm −3 . Als N nb erhöht, R c nimmt kontinuierlich ab. Mit optimiertem N nb = 1,05 × 10 17 cm −3 , R c wird zuletzt um 45% verringert. Wenn N nb> 1,05 × 10 17 cm −3 , Punch-Through-Durchbruch wird in P-Wanne auftreten. Das analytische Ergebnis von R an,sp in Abb. 2 gezeigt, zeigt an, dass das vorgeschlagene Modell eine gute Anpassung an numerische Simulationsergebnisse bietet. Daher ist das Modell glaubwürdig, um das Optimierungsdesign zu leiten.

Numerische und analytische R c als Funktion von N nb mit Single-Gate und Dual-Gate (Z = 1 cm). N d ist die Dotierungskonzentration der N-Drift-Region

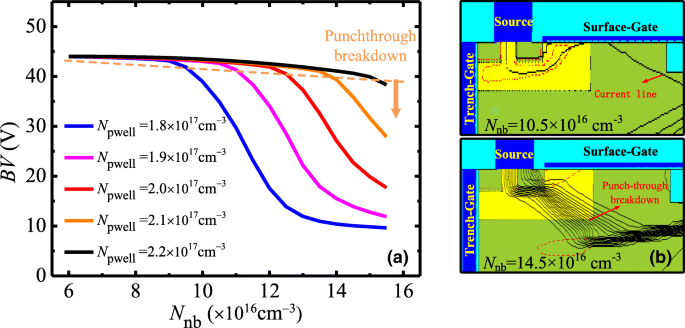

Abbildung 3a zeigt die numerische BV als Funktion von N nb mit unterschiedlicher Dotierungskonzentration der P-Wanne (N pwell ). N nb wirkt sich nicht nur auf den R aus c , aber auch die BV. Für ein gegebenes N pwell , BV bleibt unverändert bei kleinem N nb , und nimmt dann mit N . ab nb zunehmend. Wenn N nb erhöht sich auf 1,2 × 10 17 cm −3 , BV beginnt mit N . zu sinken pwell = 2 × 10 17 cm −3 . Der Abfall von BV wird dem Punch-Through-Durchbruch in der P-Wannenregion zugeschrieben, wie in Fig. 3b gezeigt. Wenn die Drainspannung ansteigt, erstreckt sich der Verarmungsbereich in der P-Wanne bis zur Source. Wenn der Verarmungsbereich den N+/P-Wannenübergang angreift, tritt der Durchgriffsdurchschlag auf. Für ein großes N pwell , erstreckt sich die Verarmung hauptsächlich auf den Driftbereich, und der Durchschlagsdurchbruch wird vermieden, ohne die BV zu verschlechtern. Obwohl eine P-Wanne mit hoher Dotierungskonzentration Vorteile bei der Vermeidung des Durchschlagsdurchbruchs hat, würde sie die Schwellenspannung erhöhen. Also, N pwell von 2 × 10 17 cm −3 wird unter Berücksichtigung der Schwellenspannung und des Kompromisses zwischen BV und R . ausgewählt an,sp .

a Numerische BV als Funktion von N nb mit verschiedenen N pwell . b Aktuelles Dichteprofil für N nb = 10.5 × 10 16 cm −3 und 14,5 × 10 16 cm −3 während N pwell = 2 × 10 17 cm −3 bei Panne

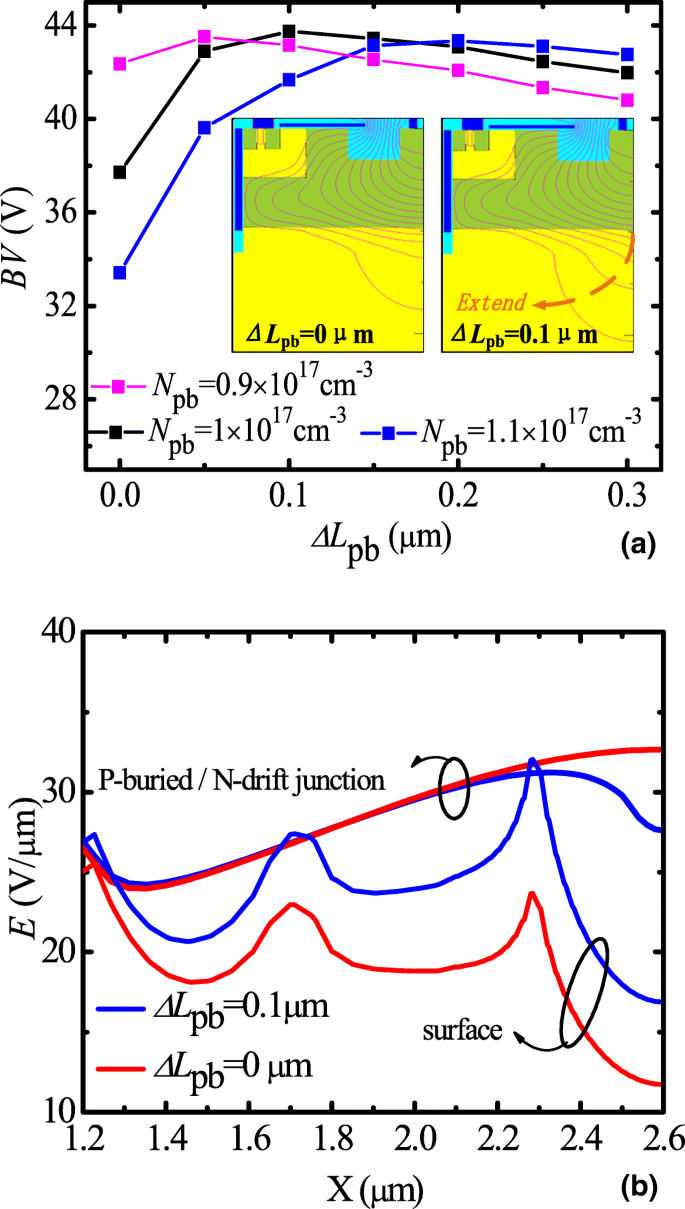

Um einen niedrigen R . zu erreichen d und eine teilweise P-vergrabene Schicht mit hohem BV wird unter dem N-Drift-Bereich eingeführt. Abbildung 4a zeigt BV als Funktion von ΔL pb mit verschiedenen N pb . Für ein gegebenes N pb , als ΔL pb steigt, BV steigt und fällt dann leicht ab. Wenn ΔL pb = 0.1 μm, N pb = 1 × 10 17 cm −3 , BV erreicht den Maximalwert 43 V Die Einlage zeigt das Äquipotentialkonturprofil mit N pb = 1 × 10 17 cm −3 . Es wird darauf hingewiesen, dass sich die Äquipotentialkontur in der partiellen P-vergrabenen Schichtstruktur im Vergleich zur vollständigen P-vergrabenen Schicht mehr auf das Substrat erstreckt. Abbildung 4b zeigt die Verteilung des elektrischen Felds an der Oberfläche und der Grenzfläche zwischen P-vergrabenem/N-Drift-Übergang. Für optimierte konventionelle LDMOS tritt der Durchbruch normalerweise an der N-Drift/P-vergrabenen Schnittstelle auf. Für den vorgeschlagenen LDMOS ersetzt der Übergang von N-Drift/P-sub den Übergang von N-Drift/P-vergraben, um das vertikale elektrische Feld zu entspannen und den Verarmungsbereich zu erweitern, was zu einer höheren BV führt, während ein niedriges R . beibehalten wird d .

a BV als Funktion von ΔL pb mit verschiedenen N pb . Die Einlage ist das Äquipotentialkonturprofil mit N pb = 1 × 10 17 cm −3 . b Verteilung des elektrischen Feldes an der Oberfläche und der Grenzfläche zwischen P-vergrabenem/N-Drift-Übergang

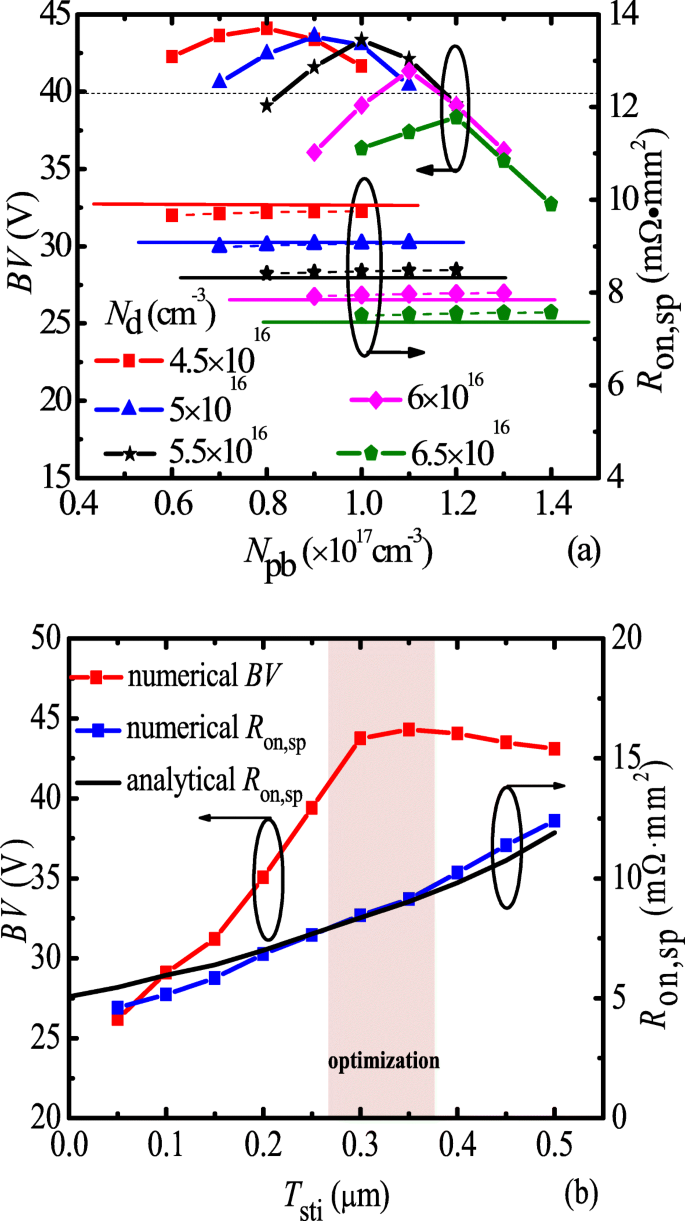

Ein Ladungsausgleich zwischen N-Drift und teilweise P-vergrabener Schicht ist erforderlich, um eine hohe BV zu erreichen. Abbildung 5a zeigt, dass numerische und analytische BV und R an,sp als Funktion der Dotierungskonzentration des P-vergrabenen (N pb ) für verschiedene N d . Für ein gegebenes N d , BV hat einen Maximalwert mit unterschiedlichen N pb , und das Maximum von BV steigt mit der Abnahme von N d . R an,sp kann als N . erhöht werden d abnehmend. Wegen BV höher als 40 V erforderlich, die N d = 5,5 × 10 16 cm −3 und N pb = 1 × 10 17 cm −3 sind auserwählt. Abbildung 5b zeigt numerische und analytische BV und R an,sp als Funktion der Dicke der STI-Schicht (T sti ). T sti hat starken Einfluss auf BV und R an,sp , und es sollte sorgfältig entworfen und optimiert werden, ebenso wie unsere bisherigen Arbeiten [21]. Für T sti < 0,3 μm, der Durchbruchspunkt unter dem Rand der Polyfeldplatte weist eine hohe elektrische Feldspitze auf. Als T sti nimmt zu, die Spitze des elektrischen Felds wird entspannt und dann BV steigt. Für T sti = 0,3 μm, BV von 43 V wird erhalten. Für T sti ≥ 0,3 μm, die elektrische Feldspitze unter dem Rand der Polyfeldplatte ist ausreichend niedrig, als Ergebnis überträgt sich der Durchbruchspunkt auf den P/N-Übergang unter der Drain-Seite. Als T sti steigt, BV steigt und sättigt sich dann.

a Numerisch (gestrichelte Linie) und analytisch (durchgezogene Linie) BV und R an,sp als Funktionen von N pb für verschiedene N d . b Numerisch (gestrichelte Linie) und analytisch (durchgezogene Linie) BV und R an,sp als Funktionen von T sti

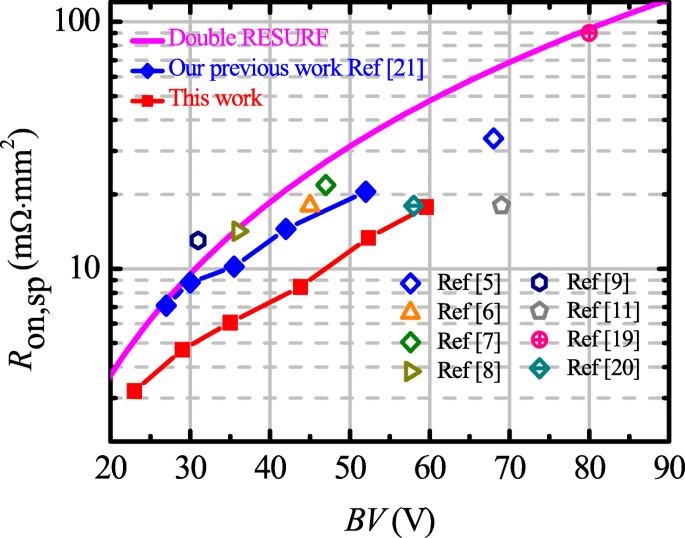

Abbildung 6 zeigt den Benchmark bestehender Bipolar-CMOS-DMOS (BCD)-Technologien und des vorgeschlagenen LDMOS. Offensichtlich ist die Prozesstechnologie für das vorgeschlagene LDMOS mit unserer entwickelten BCD-Technologie kompatibel, die die klassenbeste Leistung von LDMOS erreicht hat. Bei dem Herstellungsprozess für den vorgeschlagenen LDMOS könnte die N-vergrabene Schicht dieselbe Maske mit der P-Wanne teilen. Für das vorgeschlagene LDMOS, R an,sp ist 8,5 mΩ·mm 2 während BV = 43 V, was im Vergleich zu unserer vorherigen Arbeit um etwa 37% reduziert ist.

Der Maßstab bestehender BCD-Technologien und des vorgeschlagenen LDMOS

Schlussfolgerung

In diesem Beitrag wird ein neuartiger LDMOS mit extrem niedrigem spezifischen On-Widerstand mit verbessertem Dual-Gate und partieller P-vergrabener Schicht vorgeschlagen und durch numerische Simulation untersucht. N-vergrabene Schicht mit hoher Dotierungskonzentration wird verwendet, um ein verbessertes Dual-Gate mit reduziertem R . zu erreichen c . Eine partielle P-vergrabene Schicht wird unter der N-Drift-Region eingeführt, um BV . zu verbessern unter Beibehaltung des Ladungsausgleichs. Der Herstellungsprozess des LDMOS in dieser Arbeit ist mit der bestehenden BCD-Technologie kompatibel, über die in unserer vorherigen Arbeit berichtet wurde. Das Ergebnis zeigt, dass die R an,sp des vorgeschlagenen LDMOS wird bei einer BV von 43 V im Vergleich zu früheren Arbeiten um 37 % reduziert. Da die Halbleiterverarbeitungstechnologie auf Nanometerebene geht, ist die R an,sp kann mit abnehmender Kanallänge weiter reduziert werden.

Abkürzungen

- BCD:

-

Bipolar-CMOS-DMOS

- BV:

-

Durchbruchspannung

- LDMOS:

-

Lateraler doppelt diffundierter Metall-Oxid-Halbleiter-Transistor

- RESURF:

-

Oberflächenfeld reduzieren

- R an,sp :

-

Spezifischer Einschaltwiderstand

- USTI:

-

Ultraflache Grabenisolation

Nanomaterialien

- Nanofasern und Filamente für eine verbesserte Wirkstoffabgabe

- Grenzflächen-, elektrische und Bandausrichtungseigenschaften von HfO2/Ge-Stapeln mit in situ gebildeter SiO2-Zwischenschicht durch plasmaunterstützte Atomlagenabscheidung

- Ein neuartiger Bi4Ti3O12/Ag3PO4-Heteroübergang-Photokatalysator mit verbesserter photokatalytischer Leistung

- Einfluss der erhöhten thermischen Stabilität der Trägerschicht aus Aluminiumoxid auf das Wachstum vertikal ausgerichteter einwandiger Kohlenstoffnanoröhren und ihre Anwendung in Nanofiltrationsmem…

- Einfluss von in einer TiO2-Kompaktschicht eingebetteten Ag-Nanopartikeln unterschiedlicher Größe und Konzentration auf die Konversionseffizienz von Perowskit-Solarzellen

- Antiproliferatives und Apoptose-auslösendes Potenzial von Paclitaxel-basierten Targeted-Lipid-Nanopartikeln mit verbesserter zellulärer Internalisierung durch Transferrinrezeptoren – eine Studie in …

- Omnidirektionaler Absorber durch den Void-Plasmon-Effekt im sichtbaren Bereich mit stark verstärktem lokalisiertem elektrischem Feld

- SnSe2-Feldeffekttransistor mit hohem Ein-/Aus-Verhältnis und umschaltbarer Polarität

- TiO2-Nanomembranen, hergestellt durch Atomlagenabscheidung für Superkondensatorelektroden mit erhöhter Kapazität

- poröse ZnO-Nanoblätter mit partieller Oberflächenmodifikation für verbesserte Ladungstrennung und hohe photokatalytische Aktivität unter Sonnenbestrahlung