Ge-pMOSFETs hoher Mobilität mit amorpher Si-Passivierung:Einfluss der Oberflächenorientierung

Zusammenfassung

Wir berichten über die amorphe Si-Passivierung von Ge-pMOSFETs, die auf (001)-, (011)- und (111)-orientierten Oberflächen für fortschrittliche CMOS- und Dünnschichttransistoranwendungen hergestellt wurden. Die Passivierung von Ge mit amorphem Si wird durch Magnetron-Sputtern bei Raumtemperatur durchgeführt. Mit der festen Dicke von Si t Si , (001)-orientierte Ge-pMOSFETs erreichen den höheren Durchlassstrom I EIN und effektive Lochbeweglichkeit μ eff im Vergleich zu den Geräten auf anderen Ausrichtungen. Bei einer Inversionsladungsdichte Q inv von 3,5 × 10 12 cm −2 , Ge(001)-Transistoren mit 0,9 nm t Si zeigen einen Peak μ eff von 278 cm 2 /V × s, was 2,97 mal höher ist als die universelle Si-Mobilität. Mit der Abnahme von t Si , ich EIN der Ge-Transistoren nimmt aufgrund der Verringerung der kapazitiven effektiven Dicke zu, aber die unterschwelligen Swing- und Leckbodeneigenschaften werden verschlechtert, was auf die Zunahme von Midgap D . zurückzuführen ist es .

Hintergrund

Germanium (Ge) hat aufgrund seiner höheren Lochbeweglichkeit und der geringeren thermischen Budgetverarbeitung im Vergleich zu Si ein enormes Forschungsinteresse für fortschrittliche CMOS- und Dünnschichttransistoranwendungen auf sich gezogen [1,2,3,4,5,6]. Um die hohe Kanalbeweglichkeit zu erreichen, ist vor der Gatestapelbildung der Oberflächenpassivierungsprozess erforderlich, der zu einer hohen Grenzflächenqualität führt. Mehrere Oberflächenpassivierungstechniken wurden entwickelt, um die Vorteile der Ladungsträgermobilität in Ge-Metalloxid-Halbleiter-Feldeffekttransistoren (MOSFETs) zu erzielen [1, 2, 7,8,9,10]. Unter diesen Techniken war eine auf Ge passivierte Silizium (Si)-Kappe in den letzten Jahren aufgrund ihrer Vorteile der effektiven Unterdrückung von Grenzflächenzuständen und der guten thermischen Stabilität und Zuverlässigkeit der Hotspot [11]. Die Bildung von Si-Passivierungskappen wurde unter Verwendung von chemischer Gasphasenabscheidung (CVD) mit Vorläufern von SiH4 . ausführlich untersucht [1], Si2 H6 [4], Si3 H8 [12] und Elektronenstrahlverdampfung [13]. Obwohl das CVD-Verfahren die gleichförmigere Passivierungsschicht gegenüber der physikalischen Gasphasenabscheidung (PVD) bereitstellen könnte, weist seine Passivierungsrate eine starke Korrelation zwischen der Kanaloberflächenorientierung und der Prozesstemperatur auf. Die PVD-Technik könnte die verbesserte Passivierungsrate sogar bei Raumtemperatur bereitstellen, was die Vorteile eines geringen thermischen Budgets und niedriger Kosten hat, was sie besser für Dünnschichttransistoren und Back-End-of-Line-3D-Integrationsanwendungen geeignet macht. In diesem Brief haben wir Ge-pMOSFETs mit hoher Mobilität auf (001)-, (011)- und (111)-orientierten Oberflächen unter Verwendung von amorpher Si-Passivierung durch Magnetron-Sputtern hergestellt. Deutlich verbesserte effektive Lochbeweglichkeit μ eff wird bei Ge-Transistoren im Vergleich zur Si-Universalmobilität erreicht. Auswirkungen der Oberflächenorientierung und Dicke von amorphem Si t Si zur verstärkenden Wirkung der Passivierung von amorphem Si auf μ eff studiert werden.

Methoden

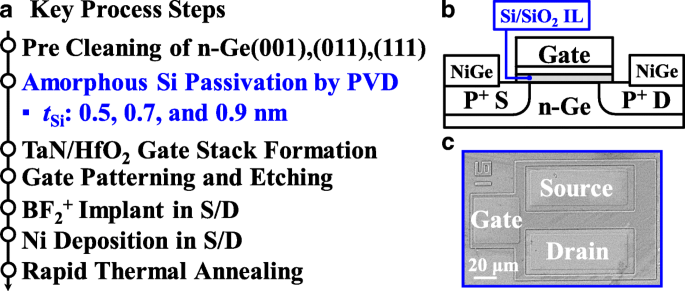

Abbildung 1a zeigt die wichtigsten Prozessschritte zur Herstellung von Ge-pMOSFETs auf (001)-, (011)- und (111)-orientierten Oberflächen. Nach der Reinigung vor dem Gate in verdünnter HF-Lösung (1:50) wurde eine ultradünne amorphe Si-Passivierungsschicht auf n-Ge-Substraten durch Magnetron-Sputtern bei einer Targetleistung von 50 W abgeschieden Drei Passivierungsdauern von 60 s, 80 s und 100 s wurden entsprechend der Abscheidung von 0.5, 0.7 und 0.9 nm t . verwendet si , bzw. Danach ein 5 nm dickes HfO2 Gate-Dielektrikum wurde bei 250°C durch Atomlagenabscheidung unter Verwendung von TDMAHf und H2 . abgeschieden O als Vorläufer von Hf bzw. O. Eine 50-nm-TaN-Gate-Elektrode wurde durch reaktives Sputtern abgeschieden. Als nächstes wurde die Gate-Elektrode strukturiert und geätzt, gefolgt von BF2 + Implantation in Source/Drain (S/D)-Regionen bei 30 KeV mit einer Dosis von 1 × 10 15 cm − 2 . Nicht selbstjustierte S/D-Metalle aus 15 nm Nickel wurden durch den Abhebeprozess gebildet. Schließlich wurde ein schnelles thermisches Ausheilen bei 400 °C zur Dotierstoffaktivierung und S/D-Metallisierung durchgeführt. Abbildung 1b zeigt das schematische Querschnittsschema des Ge-pMOSFET mit Si/SiO2 Grenzschicht (IL). Abbildung 1c zeigt ein Mikroskop-Draufsichtsbild eines hergestellten Ge-pMOSFET.

a Prozesssequenz mit den wichtigsten Schritten zur Herstellung der Ge-pMOSFETs mit unterschiedlichen t Si . b Querschnittsschema eines Ge-pMOSFET mit SiO2 IL. c Mikroskop-Draufsicht eines hergestellten Ge-pMOSFET

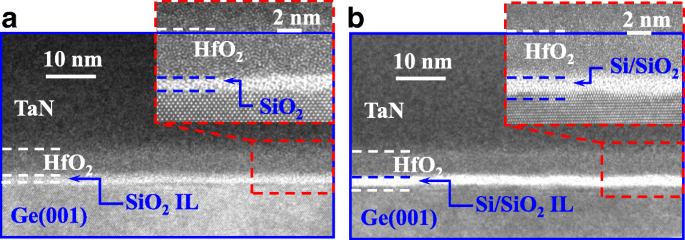

Abbildung 2a, b zeigt die Transmissionselektronenmikroskop(TEM)-Aufnahmen des High-κ/Metall-Gate-Stapels mit SiO2 /Si-Grenzflächenschicht (IL) auf Ge(001)-Kanal mit t Si von 0,5 bzw. 0,9 nm. Einschübe zeigen die hochauflösenden TEM (HRTEM) Bilder der Proben. Für das Gerät mit einem t Si von 0,5 nm wurde die amorphe Si-Schicht vollständig oxidiert, während für das Gerät mit 0,9 nm t Si , blieben nach den nachfolgenden Temperschritten etwa zwei Si-Monoschichten übrig.

Querschnitts-TEM-Bilder von Ge-pMOSFET-Gate-Stacks mit a 0,5 nm t Si und b 0,9 nm t Si . HRTEM-Bilder in Einschübe zeigen, dass Si/SiO2 IL wird zwischen HfO2 . gebildet und Ge-Kanal

Ergebnisse und Diskussion

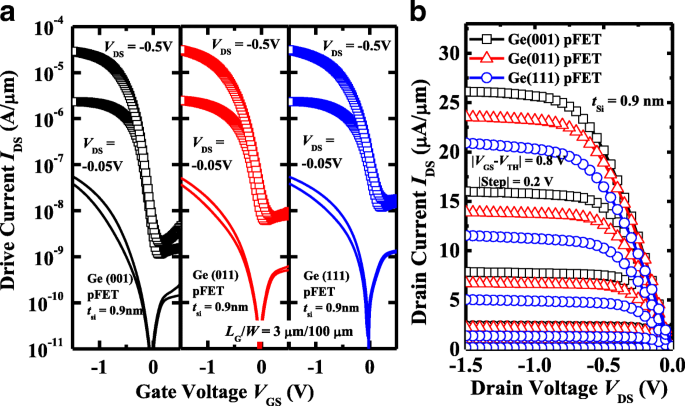

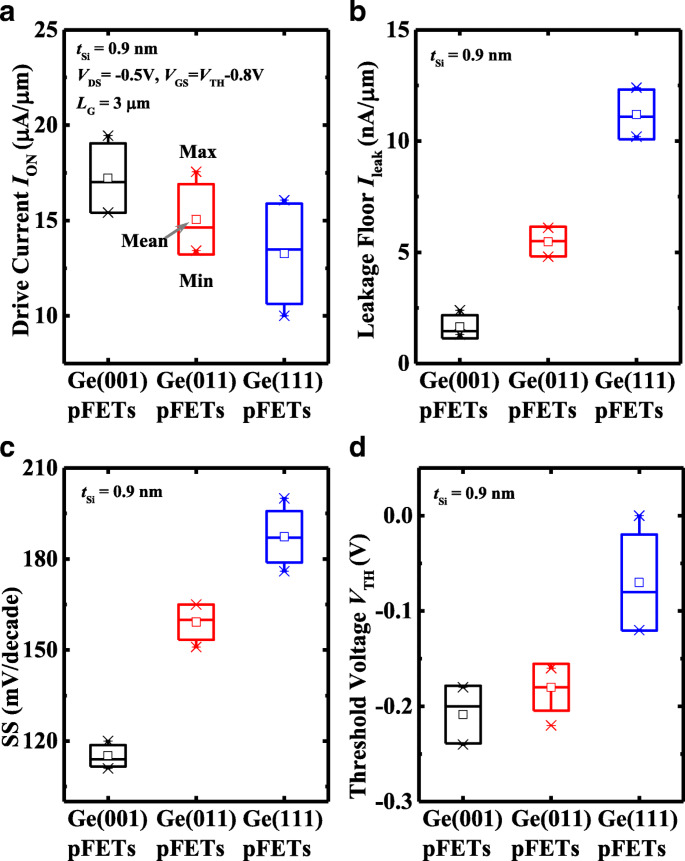

Abbildung 3a zeigt das gemessene I DS -V GS und ich G -V GS Kurven der typischen Ge-pMOSFETs auf (001)-, (011)- und (111)-orientierten Oberflächen mit 0,9 nm t Si , die die hervorragenden Übertragungseigenschaften zeigen. Alle Transistoren haben eine Gatelänge L G von 3 μm und einer Gate-Breite W von 100 µm. Die Kanalrichtung ist [110] für alle Ausrichtungen. Das Ich DS -V DS Kurven der Geräte gemessen bei verschiedenen Gate-Overdrive V GS -V TH sind in Abb. 3b dargestellt. Hier Schwellenspannung V TH ist definiert als das V GS bei ich DS von 10 −7 A/μm. Es wird beobachtet, dass der Ge(001)-pMOSFET den höheren Treiberstrom I . erreicht EIN im Vergleich zu den Transistoren auf (011)- und (111)-Oberflächen bei festem V GS -V TH . Später werden wir zeigen, dass dies darauf zurückzuführen ist, dass Ge(001)-pMOSFETs eine höhere effektive Lochbeweglichkeit μ . aufweisen eff im Vergleich zu den Geräten auf den anderen beiden Oberflächenausrichtungen. Wir führen einen umfassenden Vergleich der elektrischen Leistung der Geräte mit dem festen t . durch Si von 0,9 nm, einschließlich I EIN , Leckageboden I Leck , unterschwelliger Swing (SS) und V TH Eigenschaften. Ich Leck ist definiert als das minimale I DS bei V DS von − 0.05 V. Abbildung 4a zeigt den statistischen Plot des I EIN für Ge-pMOSFETs in verschiedenen Orientierungen und I EIN wurde definiert als ich DS bei einem V DS von − 0.5 V und einem V GS -V TH von − 0.8 V. Alle Transistoren in diesem Diagramm haben die L G von 3 μm und W von 100 µm. (001)-orientierte Geräte zeigen den verbesserten Mittelwert I EIN im Vergleich zu denen auf (011) und (111) Orientierungen, was dem höheren μ . zugeschrieben wird eff . Abbildung 4b vergleicht das I Leck für die Geräte, was zeigt, dass Ge(001)-Transistoren den niedrigsten I . haben Leck von ihnen, und Ge(011)-pMOSFETs haben das niedrigere I Leck als (111)-orientierte Geräte. Es sollte beachtet werden, dass das I Leck wird bestimmt durch den Rückstrom des p + /n-Übergang im Drain-Bereich, der durch die n-Dotierungskonzentration im Hintergrund im Ge-Substrat und die Aktivierung des implantierten p + . beeinflusst wird Dotierstoffe. Die n-Dotierungskonzentrationen in den Wafern mit verschiedenen Orientierungen sind nicht genau gleich. Die Oberflächenorientierung beeinflusst die Dotierstoffaktivierungsrate und die Rekristallisationsqualität von S/D-Gebieten. Obwohl das Ich G ist niedriger als I DS vor dem Einschalten der Transistoren würde es das I beeinflussen Leck . In ähnlicher Weise zeigen (001)-orientierte Ge-pMOSFETs die verbesserten SS-Eigenschaften im Vergleich zu anderen beiden Ausrichtungen, was darauf zurückzuführen ist, dass Transistoren auf der (001)-Oberfläche die niedrigere mittlere Lückendichte des Grenzflächenzustands D . aufweisen es im Vergleich zu den anderen Geräten. Abbildung 4d zeigt, dass die Geräte in verschiedenen Ausrichtungen die unterschiedlichen V . haben TH . Aus den Ergebnissen in Abb. 4 wird geschlossen, dass mit dem festen t Si von 0,9 nm erzielen (001)-orientierte Ge-pMOSFETs die besten elektrischen Eigenschaften.

a Gemessen I DS -V GS und ich G -V GS Kurven von (001)-, (011)- und (111)-orientierten Ge-pMOSFETs mit 0,9 nm t Si zeigt die hervorragenden Übertragungseigenschaften. b Ich DS -V DS Kurven gemessen bei verschiedenen V GS -V TH für die Geräte

Vergleich von a Ich EIN , b Ich Leck , c SS und d V TH für (001)-, (011)- und (111)-orientierte Ge-pMOSFETs mit einem t Si von 0,9 nm

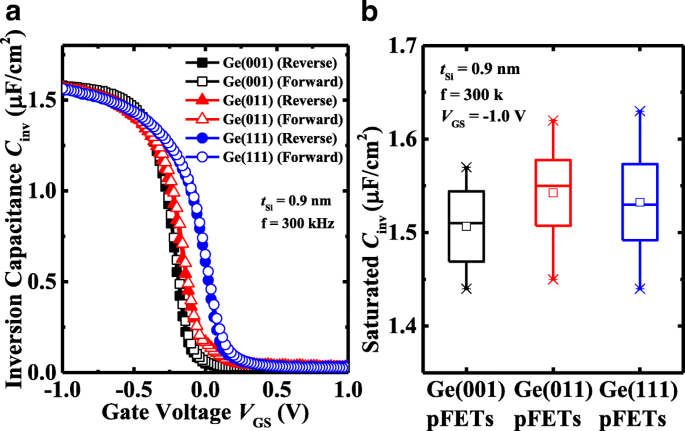

Die Dicken von Si/SiO2 IL in Transistoren mit 0,9 nm t Si auf verschiedenen Oberflächenorientierungen werden unter Verwendung der Inversionskapazität C . untersucht inv gegen V GS Messung, wie in Abb. 5 gezeigt. Vorwärts- und Rückwärts-Sweep-Messungen zeigen die vernachlässigbar kleine Hysterese in den Geräten. Die Transistoren weisen eine ähnliche Größe von C . auf inv , ~ 1,56 μF/cm 2 , entsprechend der kapazitiven effektiven Dicke (CET) von 2,2 nm. Abbildung 5b zeigt die statistischen Ergebnisse von gesättigtem C inv für die Geräte, die den sehr kleinen Unterschied in C . demonstrieren inv in den Transistoren auf unterschiedlichen Oberflächenorientierungen. Dies weist darauf hin, dass die Passivierungsrate von amorphem Si durch Magnetron-Sputtern unabhängig von der Oberflächenorientierung ist. Die Regel der Links-Rechts-Verschiebung des C inv -V GS Kurven stimmt gut mit der von V . überein TH für die Bauelemente in Fig. 4d, die durch die leicht unterschiedliche Dotierungskonzentration in Substraten mit unterschiedlicher Ausrichtung induziert werden könnten.

a Vergleich der Inversion C inv -V GS Kurven unter den Ge-pMOSFETs mit 0,9 nm t Si auf verschiedene Ausrichtungen. Sowohl Vorwärts- als auch Rückwärts-Sweep werden angezeigt. b Statistische Diagramme für das gesättigte C inv der Geräte mit den vernachlässigbaren Unterschieden in C inv im Inversionsregime

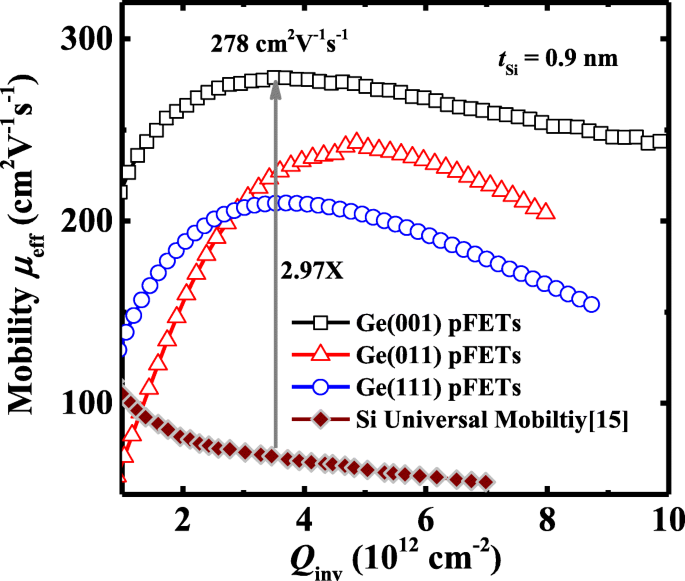

Abbildung 6 vergleicht die Mobilitätseigenschaften der Transistoren mit 0,9 nm t Si auf verschiedenen Oberflächenausrichtungen. Die μ eff wurde mit einer auf Gesamtwiderstandssteigung basierenden Methode extrahiert [14]. Ge(001)-pMOSFETs weisen im Vergleich zu den Bauelementen in (011)- und (111)-Ausrichtungen die viel höhere Kanalbeweglichkeit auf. Transistoren auf (001)-Substrat erreichen eine Spitze von μ eff von 278 cm 2 /V·s bei einer Inversionsladungsdichte Q inv von ~ 3,5 × 10 12 cm −2 , was 2,97-mal höher ist als die universelle Mobilität von Si. Oberflächenrauheit an der Si/Ge-Grenzfläche und Dichte der Grenzflächenzustände (D es ) kann μ . beeinflussen eff der Bauelemente bei hoher Inversionsträgerdichte. Es ist unwahrscheinlich, dass die im Handel erhältlichen Ge-Wafer mit verschiedenen Oberflächenorientierungen den offensichtlichen Unterschied in der Oberflächenrauheit aufweisen. Daher wird spekuliert, dass die Mobilitätsverbesserung in (001)-orientierten Geräten hauptsächlich auf eine verringerte Trägerstreuung zurückzuführen ist, die durch Grenzflächenzustände beigetragen wird. In dieser Arbeit evaluieren wir den Midgap D es der Geräte und mit dem festen t Si von 0,9 nm haben die (001)-orientierten Ge-pMOSFETs tatsächlich den unteren Midgap D es im Vergleich zu den anderen Ausrichtungen.

Plot von μ eff gegen Q inv für Ge-pMOSFETs mit 0,9 nm t Si auf (001)-, (011)- und (111)-orientierten Substraten. Ge(001)-pMOSFETs erreichen die 2,97-fache Verbesserung in μ eff bei einem Q inv von 3,5 × 10 12 cm −2 im Vergleich zur Si-Universalmobilität. Die μ eff wurde mit einer auf Gesamtwiderstandssteigung basierenden Methode extrahiert [17]

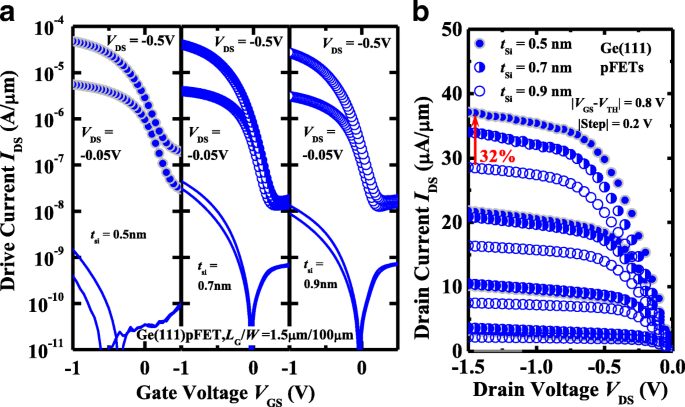

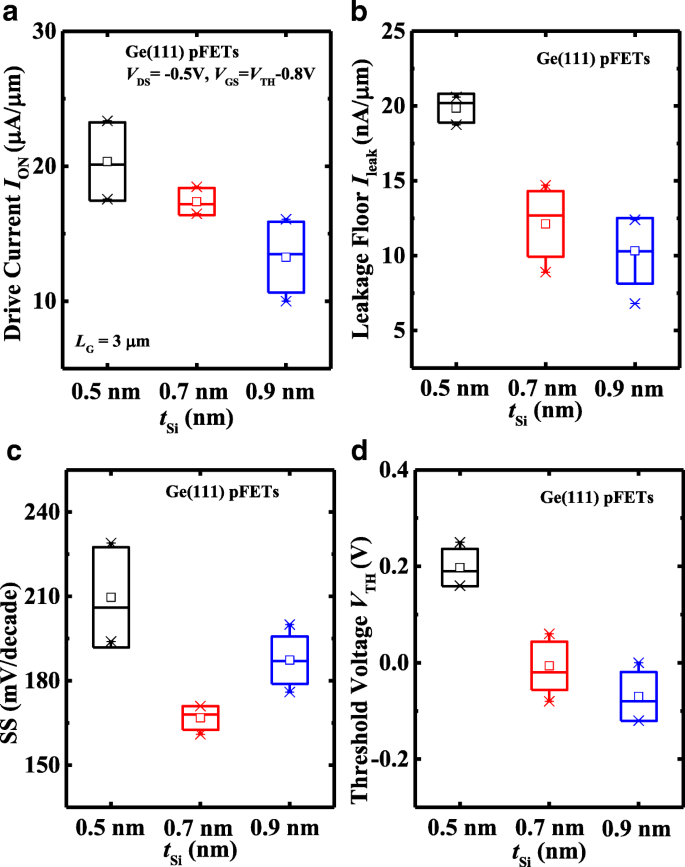

Die Wirkung von t Si auf die elektrische Leistung von Ge-pMOSFETs wird ebenfalls untersucht. Abbildung 7a, b zeigen das gemessene I DS -V GS und ich DS -V DS Kurven der (111)-orientierten Ge-pMOSFETs mit t Si von 0,5, 0,7 und 0,9 nm bei V DS von − 0.05 und − 0.5 V. Die Transistoren haben ein L G von 1,5 µm. Es wird beobachtet, dass Ge-pMOSFETs mit 0,9 nm t Si zeigen verbesserte Übertragungseigenschaften im Vergleich zu Geräten mit dünnerem t Si , aber ich EIN des Geräts nimmt mit zunehmendem t . ab Si . Bei V DS von − 1.5 V und V GS -V TH von − 0.8 V, Ge(111) pMOSFET mit 0.5 nm t Si zeigt eine 32-prozentige Verbesserung von I EIN im Vergleich zum Gerät mit 0,9 nm t Si . Abbildung 8 zeigt die statistischen Ergebnisse von I EIN , ich Leck , SS und V TH der Ge pMOSFETs auf (111)-Orientierung mit unterschiedlichen t Si . Aus Abb. 8a sehen wir, dass Transistoren mit 0,5 nm t Si das verbesserte I erreichen EIN im Vergleich zu den Geräten mit dickerem t Si , was auf den Transistor mit 0.5 nm t . zurückzuführen ist Si das eine kleinere CET hat, was zu einem höheren C führt inv . Es wird bemerkt, dass ich Leck nimmt mit zunehmendem t . ab Si (Abb. 8b) und Transistoren mit 0,5 nm t Si hat schlechtere SS-Eigenschaften als die Bauelemente mit 0,7 und 0,9 nm amorpher Si-Passivierungsschicht (Abb. 8c). Dies könnte an diesen Transistoren mit 0,5 nm t . liegen Si mit einem höheren Mittelabstand D es . Die Beziehung zwischen SS und Midgap D es von Ge pMOSFET kann ausgedrückt werden durch SS = ln(10) ⋅ (kT /q) ⋅ [1 + (C es + C d )/C Ochse ], wobei C Ochse , C d , und C es sind Oxidkapazität, Sperrschichtkapazität bzw. Kapazität von Grenzflächenfallen. C es kann berechnet werden durch q × D es , waren D es ist die Grenzflächenfallendichte. Obwohl Transistor mit 0,5 nm t Si hat das größere C Ochse im Vergleich zu den anderen beiden Geräten ist der mittlere Abstand D . höher es kann zu einer schlechteren SS führen als die Geräte mit dem dickeren t Si . Die Oberflächenpassivierung beeinflusst auch das I Leck vom Abfluss zur Quelle. Mit dem Streichen von V GS von Position zu negativ wechselt der Kanal vom Akkumulationsmodus in den Inversionsmodus. Wenn jedoch das D es hoch ist, werden einige Punkte in der Kanaloberfläche durch die Grenzflächenfallen fixiert und die Kriechpfade können gebildet werden, wodurch I . erhöht wird Leck vom Abfluss zur Quelle. Wie in Fig. 8d gezeigt, zeigen Ge(111)-pMOSFETs die Verschiebung von V TH zu negativ V GS Richtung mit der Erhöhung von t Si , was auf die erhöhte CET zurückzuführen ist. Darüber hinaus scheint die Dichte der Fallen in der unteren Bandlückenhälfte für das dünnere t . zuzunehmen Si , was zur Verschiebung von V . führen könnte TH [2].

a Ich DS -V GS und ich G -V GS und b Ich DS -V DS Kurven von Ge(111)-pMOSFETs mit verschiedenen t Si . Transistor mit 0,5 nm t Si zeigt eine 32-prozentige Verbesserung des I EIN im Vergleich zum Gerät mit 0,9 nm t Si bei V DS von − 1.5 V und V GS -V TH von − 0.8 V

Vergleich von a Ich EIN , b Ich Leck , c SS und d V TH für (111)-orientierte Ge-pMOSFETs mit 0,5, 0,7 und 0,9 nm t Si zeigt, dass Transistoren mit 0,5 nm t Si hab das bessere ich EIN , aber schlimmer SS und I Leck Eigenschaften im Vergleich zu Geräten mit dickerem t Si

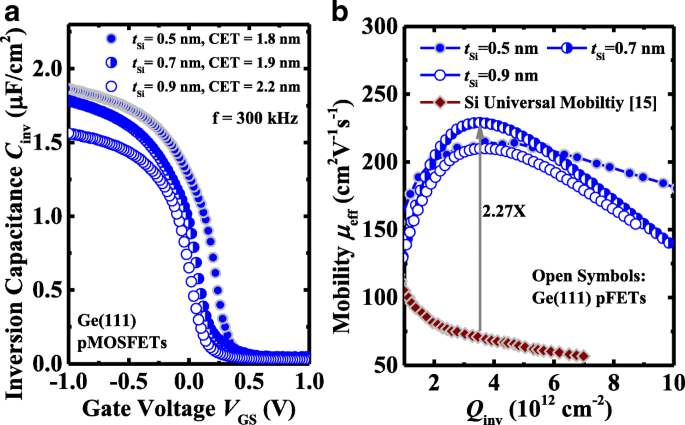

Abbildung 9a zeigt das C inv als Funktion von V GS Kurven für die Ge-pMOSFETs auf (111)-orientierter Oberfläche mit t Si von 0,5, 0,7 und 0,9 nm, gemessen bei einer Frequenz von 300 kHz. Die CET-Werte in Inversionsregionen werden mit 1,8, 1,9 und 2,2 nm für die Geräte mit 0,5, 0,7 und 0,9 nm t . extrahiert si , bzw. μ eff als Funktion von Q inv Eigenschaften der Geräte werden extrahiert und in Fig. 9b gezeigt. Der (111)-orientierte Ge-pMOSFET mit 0,7 nm t si erreicht die höchste Spitzenbeweglichkeit von 229 cm 2 /V s, was 2,27 mal höher ist als bei der Si-Universalmobilität. Zu beachten ist, dass die Geräte mit 0,5 nm t Si weisen ein deutlich verbessertes μ . auf eff über den Transistoren mit dickerem t Si bei hohem Q inv (z. B. 10 13 cm −2 ). Dies führt auch zum höheren Ich EIN bei hohem V GS -V TH in den Geräten mit 0.5 nm t Si im Vergleich zu den Geräten mit 0.7 und 0.9 nm t Si . Die μ eff bei hohem Q inv nimmt ab, wenn t Si steigt von 0,5 nm auf 0,7~0,9 nm an, was der Tatsache zugeschrieben wird, dass die größere Oberflächenrauhigkeit zu einer stärkeren Oberflächenrauhigkeitsstreuung der Träger führt. Bei der Passivierung der Ge-Oberfläche mittels Magnetron-Sputtern bei Raumtemperatur wird die Diffusion von Oberflächenatomen stark unterdrückt. Mit der Erhöhung von t Si , ist die Oberflächenrauheit größer, was aus den HRTEM-Bildern in Abb. 2 ersichtlich ist.

a C inv -V G Charakteristik gemessen bei 300 kHz für (111)-orientierte Geräte mit 0,5, 0,7 und 0,9 nm t Si . b μ eff als Funktion von Q inv für Ge-pMOSFETs [17]

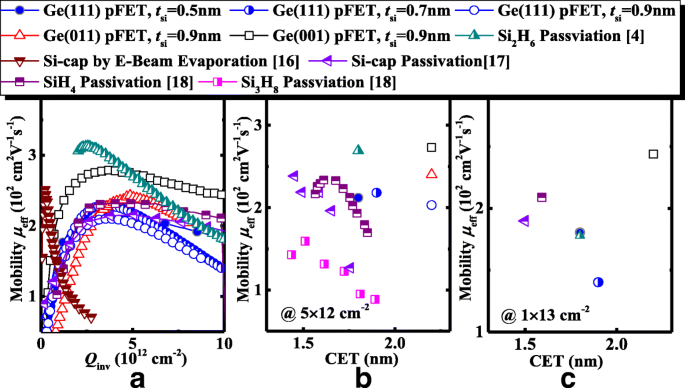

In Abb. 10 vergleichen wir die μ eff der Ge-pMOSFETs in dieser Arbeit mit denen der berichteten relaxierten Ge-Transistoren mit Si durch Elektronenstrahlverdampfung, SiH4 , Si2 H6, und Si3 H8 Passivierung. Im Vergleich zum amorphen Si durch Elektronenstrahlverdampfung in Lit. [15] zeigen die Ge-pMOSFETs in dieser Arbeit das deutlich verbesserte μ eff . Es ist zu sehen, dass Ge-pMOSFETs, die amorphe Si-Passivierung durch Magnetron-Sputtern verwenden, bei ähnlichen CET die niedrigeren μ . aufweisen eff im Vergleich zu den Geräten mit Si2 H6 Passivierung. Der Passivierungsprozess mit amorphem Si muss weiter optimiert werden, um die Ladungsträgermobilität zu erhöhen.

a μ eff für die Ge-pMOSFETs in dieser Arbeit im Vergleich zu den veröffentlichten Ergebnissen für entspannte Ge-pMOSFETs. b , c Benchmarking von μ eff extrahiert bei Q inv = 5 × 10 12 und 1 × 10 13 cm −2 , bzw. der Ge-pMOSFETs mit den unterschiedlichen CET-Werten [18, 19]

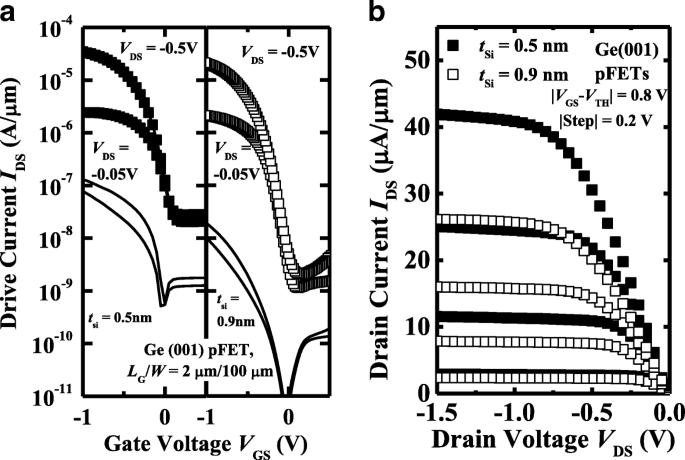

Ge pMOSFETs mit den verschiedenen t Si auf (001)-orientierter Oberfläche sind ebenfalls gekennzeichnet. Abbildung 11a, b veranschaulichen das gemessene I DS -V GS und ich DS -V DS Kurven eines Paares von Ge(001)-pMOSFETs mit 0.5 und 0.9 nm t Si . Ähnlich den (111)-orientierten Geräten, Ge(001) pMOSFET mit 0,5 nm t Si erhält die Verbesserung in I EIN aber die Verschlechterung in I Leck im Vergleich zum Transistor mit 0,9 nm t Si .

a Gemessen I DS -V GS und ich G -V GS Kurven von (001)-orientierten Ge-pMOSFETs mit 0.5 und 0.9 nm t Si . b Ich DS -V GS Kurven der Geräte

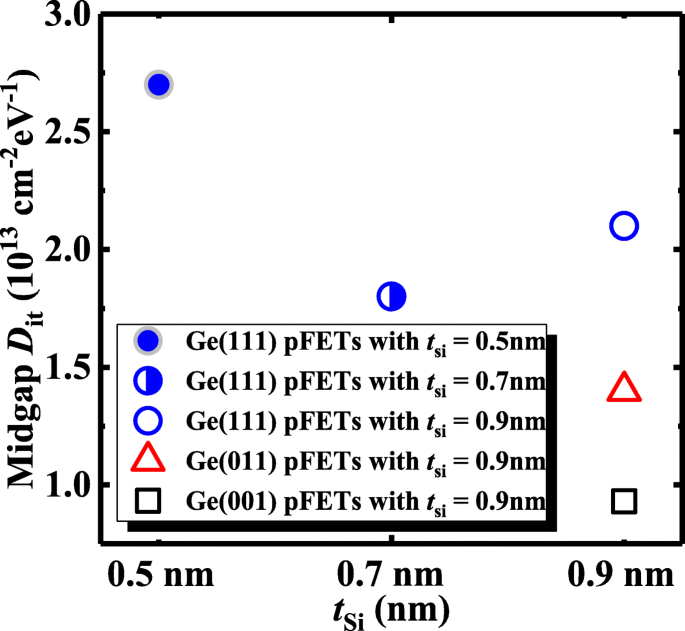

Die Midgap D es Eigenschaften von Ge-pMOSFETs werden mit der Methode in [16] untersucht, und Werte von D es werden berechnet durch D es = [SSlog(e)/(kT /q ) − 1]C G /q , [16] wobei q ist die Elektronenladung, k ist die Boltzmann-Konstante, T ist die absolute Temperatur und C G ist die gemessene Gate-Kapazität pro Flächeneinheit. Abbildung 12 zeigt D es als Funktion der Dicke von amorphem Si mit verschiedenen Ge-Oberflächenorientierungen. Für (111)-orientierte Oberfläche, ein Gerät mit 0,7-nm-t si hat das niedrigste D es Wert. Mit dem 0,9 nm t Si , (001)-orientiertes Gerät hat das niedrigere D es im Vergleich zu den Transistoren in anderen Ausrichtungen.

D es im Vergleich zur Dicke von amorphem Si mit verschiedenen Ge-Oberflächenorientierungen

Schließlich vergleichen wir in Tabelle 1 die wichtigsten elektrischen Eigenschaften von Ge-pMOSFETs in den verschiedenen Ausrichtungen. Mit einem festen t Si , Ge(001)-pMOSFET hat die verbesserte elektrische Leistung im Vergleich zu den anderen beiden Orientierungen. Der Antriebsstrom kann durch Reduzierung des t . erhöht werden Si von 0,9 nm auf 0,5 nm, was darauf zurückzuführen ist, dass das dünnere t Si bietet eine deutlich reduzierte CET, ohne eine Verschlechterung von μ . zu verursachen eff .

Schlussfolgerungen

Durch amorphes Si passivierte Ge-pMOSFETs werden auf (001)-, (011)- und (111)-orientierten Substraten demonstriert. Mit einem t Si von 0,9 nm, dem verbesserten I EIN und SS-Eigenschaften werden in (001)-orientierten Ge-pMOSFETs im Vergleich zu den Bauelementen in (011)- und (111)-Orientierungen aufgrund des höheren μ . erhalten eff und unterer Mittelabstand D es . Ge(001)-pMOSFETs mit 0,9 nm t Si erreichen eine maximale Mobilität von 278 cm 2 /V s bei einem Q inv von 3,5 × 10 12 cm −2 , was 2,97-mal höher ist als die universelle Mobilität von Si. Es wird gezeigt, dass ich EIN der Geräte wird mit der Verringerung von t . verbessert Si wegen der Kürzung der CET. Aber Ge pMOSFETs mit dickerem t Si weisen aufgrund dieses mittleren Abstands D . den überlegenen unterschwelligen Swing- und Leakage-Boden auf es kann durch Erhöhen von t . reduziert werden Si .

Abkürzungen

- ALD:

-

Atomlagenabscheidung

- BF2 + :

-

Borfluoridion

- MEZ:

-

Kapazitive effektive Dicke

- Ge:

-

Germanium

- GeOx :

-

Germaniumoxid

- HF:

-

Flusssäure

- HfO2 :

-

Hafniumdioxid

- HRTEM:

-

Hochauflösendes Transmissionselektronenmikroskop

- IL:

-

Grenzschicht

- MOSFETs:

-

Metall-Oxid-Halbleiter-Feldeffekttransistoren

- Ni:

-

Nickel

- Si:

-

Silizium

- SS:

-

Schwung unter der Schwelle

- TaN:

-

Tantalnitrid

- TDMAHf:

-

Tetrakis (dimethylamido) hafnium

Nanomaterialien

- KUHMUTE gestaltet Mobilität mit SLS-3D-Druck neu

- Hochgeschwindigkeits-3D-Druck mit AFPM

- Hochgeschwindigkeits-3D-Druck mit AION500MK3

- Hohe Leistung von PEDOT:PSS/n-Si-Solarzellen basierend auf strukturierter Oberfläche mit AgNWs-Elektroden

- Polarisationskonverter mit steuerbarer Doppelbrechung basierend auf einer hybriden volldielektrischen Graphen-Metaoberfläche

- Hochleistungsfähige organisch-nanostrukturierte Silizium-Hybridsolarzelle mit modifizierter Oberflächenstruktur

- Eine widerstandslose Spannungsreferenz im Nanomaßstab mit hohem PSRR

- poröse ZnO-Nanoblätter mit partieller Oberflächenmodifikation für verbesserte Ladungstrennung und hohe photokatalytische Aktivität unter Sonnenbestrahlung

- Ge-pMOSFETs mit GeOx-Passivierung durch Ozon- und Plasma-Nachoxidation

- Neue Erkenntnisse zu Faktoren, die den Trägertransport in sehr dünnen amorphen Sn-dotierten In2O3-Filmen mit hoher Hall-Mobilität einschränken