Ferroelektrische FETs mit nanokristallinem eingebettetem Isolator (NEI) für Geräte mit negativer Kapazität und nichtflüchtige Speicheranwendungen

Zusammenfassung

Wir berichten über einen neuartigen Nanokristall-Embedded-Isolator (NEI) ferroelektrischen Feldeffekttransistor (FeFET) mit sehr dünner vereinheitlicht-ferroelektrischer/dielektrischer (FE/DE) Isolierschicht, der vielversprechend für Niederspannungslogik und nichtflüchtige Speicher ist ( NVM)-Anwendungen. Die ferroelektrische Natur der NEI-Schichten aus orthorhombischem ZrO2 Nanokristalle eingebettet in amorphes Al2 O3 wird durch Polarisationsspannungsmessungen, Piezo-Response-Kraft-Mikroskopie und elektrische Messungen nachgewiesen. Die temperaturabhängige Leistung und das Lebensdauerverhalten eines NEI-FET mit negativer Kapazität (NCFET) werden untersucht. Ein FeFET mit 3,6 nm dickem FE/DE erreicht ein Speicherfenster von mehr als 1 V, was einen Weg für die ultimative Skalierung der FE-Dicke ebnet, um dreidimensionale FeFETs mit sehr kleinem Finnenabstand zu ermöglichen.

Hintergrund

Feldeffekttransistoren mit einer ferroelektrischen Gate-Isolatorschicht (FeFETs) haben für eine Vielzahl von Anwendungen integrierter Schaltungen großes Interesse auf sich gezogen. Aufgrund seiner inhärenten negativen Kapazitätseigenschaften (NC) kann ein FeFET ein steileres Schaltverhalten erreichen als ein konventioneller MOSFET, was einen Betrieb mit niedrigerer Spannung ermöglicht [1]. Verschiedene Kanalstrukturen [2,3,4] und Materialien [5,6,7] haben einen subthreshold-Swing (SS) von unter 60 mV/Dekade erreicht. Auch Hysterese in der Strom-Spannung (I -V ) Charakteristik durch Restpolarisation (P r ) kann für Anwendungen mit nichtflüchtigem Speicher (NVM) verwendet werden [8]. Die Materialentwicklung für FeFETs konzentrierte sich in letzter Zeit auf polykristallin dotiertes HfO2 aufgrund seiner besseren Dickenskalierbarkeit [9] und CMOS-Prozesskompatibilität [2]. Es gibt jedoch immer noch einen grundlegenden Grenzwert für HfO2 Dickenskalierung, um unerwünschte Gate-Leckströme zu vermeiden; dies begrenzt wiederum den FinFET [2]. Inspiriert vom Nanokristall-MOS- und Speicherbauelementkonzept [10, 11] wird in dieser Arbeit eine isolierende dielektrische (DE) Schicht mit eingebetteten ferroelektrischen (FE) Nanokristallen vorgestellt. Das resultierende neue Bauelementdesign, das in Abb. 1 dargestellt ist, wird als „Nanokristall-Embedded-Insulator“ (NEI) FeFET bezeichnet. Der Hauptvorteil dieses Designs ist eine dünnere vereinheitlichte FE/DE-Schicht, die die Anforderungen an ein geringes Gate-Leakage erfüllt.

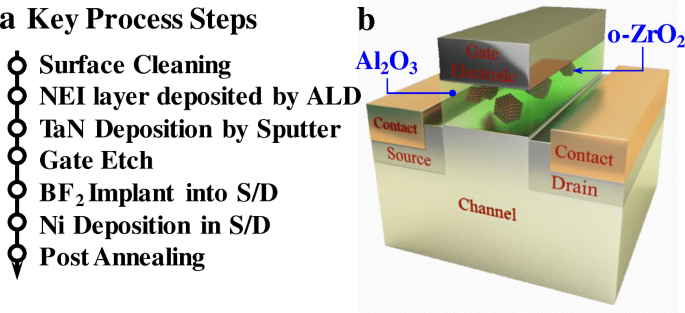

a Wichtige Prozessschritte zur Herstellung der ferroelektrischen NEI-Feldeffekttransistoren. b 3D-Schema des hergestellten NEI FeFET

In dieser Arbeit wird über NEI-FeFETs berichtet. Physikalische Eigenschaften und Ferroelektrizität der NEI-Schichten mit unterschiedlichen physikalischen Dicken werden charakterisiert. Die elektrische Leistung von NEI-FeFETs wird für Niederspannungslogik- und NVM-Anwendungen untersucht.

Methoden

Die wichtigsten Prozessschritte für die Herstellung von NEI-FeFETs sind in Abb. 1a dargestellt. Als Ausgangssubstrate wurden 4 Zoll n-Typ Ge(001)-Wafer mit einem spezifischen Widerstand von 0,088–0,14 cm verwendet. Nach der Pregate-Reinigung mit verdünnter HF wurden Ge(001)-Wafer in eine Atomlagenabscheidungskammer (ALD) geladen, um die NEI-Schicht mit ZrO2 . abzuscheiden Nanokristalle eingebettet in amorphes Al2 O3 Matrix. In dieser Arbeit wurden NEI-Schichten mit unterschiedlichen Dicken verwendet. TaN-Metallgate wurde auf den NEI-FeFETs unter Verwendung des reaktiven Sputterns abgeschieden. Nach dem Strukturieren und Ätzen des Gates wird BF2 + Ionen wurden mit einer Energie von 20 keV und einer Dosis von 1 × 15 cm –2 . in die Source-/Drain-Regionen implantiert . Dreißig-Nanometer-Nickel (Ni) wurde in Source/Drain-Gebieten unter Verwendung des Lift-Off-Prozesses abgeschieden. Schließlich wurde die Bauteilherstellung mit Rapid Thermal Annealing (RTA) abgeschlossen. Steuern Sie Metall-Oxid-Halbleiter-Feldeffekttransistoren (MOSFETs) mit einem rein dielektrischen Al2 O3 Gate-Isolierschicht wurden ebenfalls hergestellt.

Abbildung 1b zeigt das 3D-Schema des hergestellten NEI-FeFET, der FE-Nanokristalle umfasst, die in eine amorphe DE-Gate-Isolierschicht eingebettet sind. Obwohl das Volumen des FE-Materials klein ist, reicht es für NCFET- und NVM-Anwendungen aus. Das isolierende DE-Material ist der Schlüssel zum Erreichen eines geringen Gate-Leckstroms und einer niedrigen Betriebsspannung; es sollte sowohl eine große Bandlückenenergie als auch eine hohe dielektrische Permittivität (κ ). Es sollte auch für ein hohes Koerzitivfeld sorgen (E c ) der eingebetteten FE-Nanokristalle.

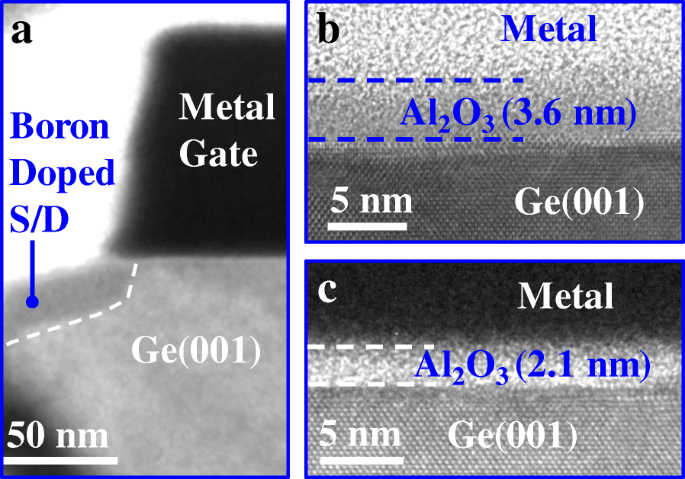

Das Querschnittsbild des Transmissionselektronenmikroskops (XTEM) in Fig. 2a zeigt die Source/Drain-, Kanal- und Gate-Randbereiche eines hergestellten FeFET. Die Abbildungen 2b und c zeigen die Dicken der in dieser Arbeit untersuchten NEI-Schichten mit 3,6 bzw. 2,1 nm. Beachten Sie, dass eine Grenzschicht aus GeOx existiert zwischen der NEI-Schicht und Ge, obwohl es nicht zu sehen ist.

a XTEM-Bild, das Gate-, Kanal- und Source-/Drain-Regionen von NEI-FeFET zeigt. b und c XTEM-Bilder eines Gate-Stapels von FeFETs mit 3,6 bzw. 2,1 nm dicken NEI-Schichten

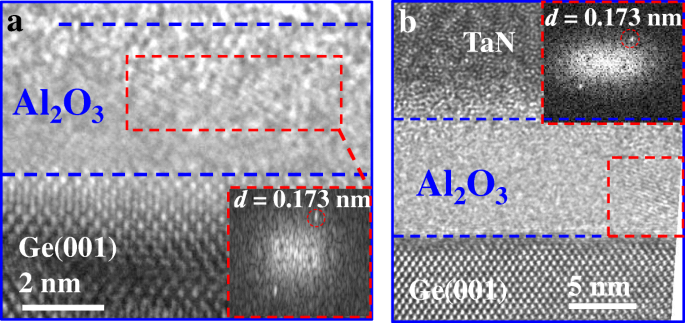

Hochauflösende TEM (HRTEM)-Bilder in Abb. 3 zeigen das ZrO2 Nanokristalle eingebettet in amorphes Al2 O3 auf Ge(001) in den NEI-Proben mit Dicken von 3,6 und 6 nm. In unseren früheren Arbeiten haben wir gezeigt, dass der Atomprozentsatz von Zr in der NEI-Schicht weniger als 0,5% beträgt [12]. Basierend auf den Beugungsmustern beträgt der Interplanarabstand d innerhalb der Nanokristalle wird mit 0,173 nm berechnet, was (111)-orientiertem orthorhombischem ZrO2 . entspricht Phase [13].

HRTEM-Bilder, die Nanokristalle zeigen, die in amorphes Al2 . eingebettet sind O3 für die Proben mit Dicken von a 3,6 nm und b 6 nm. Einschübe zeigen, dass der Interplanarabstand d im Nanokristall beträgt 0,173 nm, entsprechend o-ZrO2 (111)-Phase

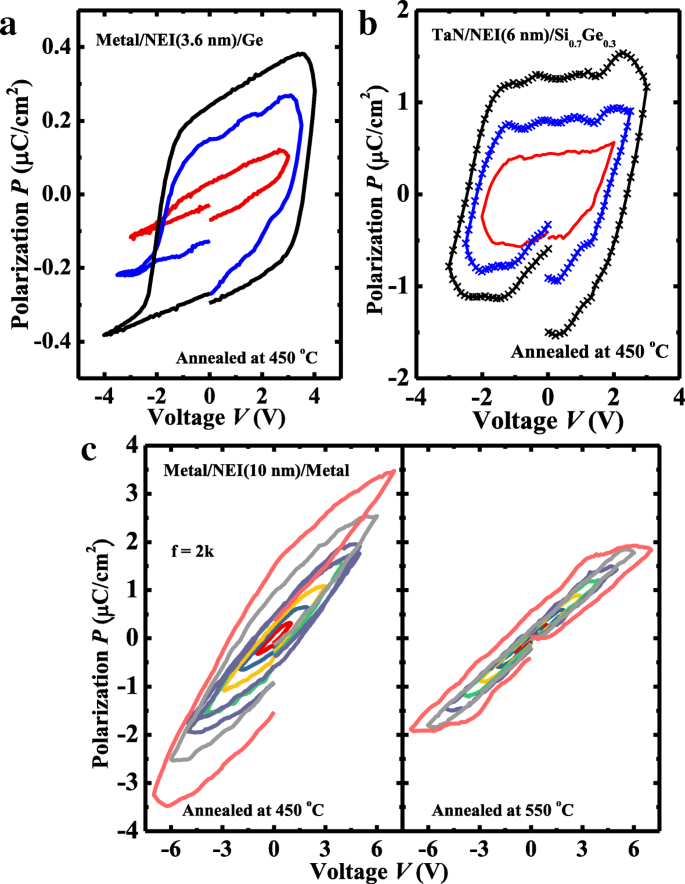

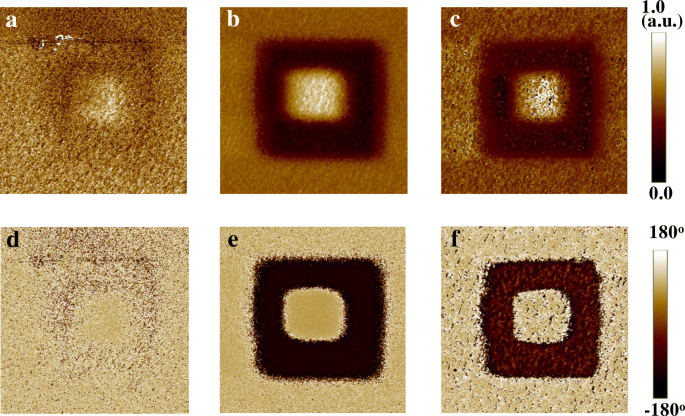

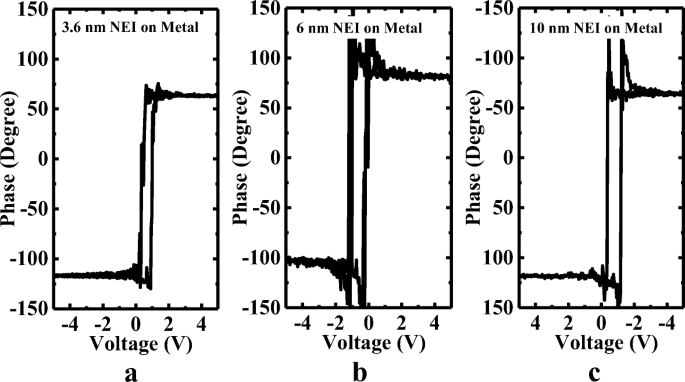

Polarisation vs. Spannung (P -V ) und piezoresponse force microscopy (PFM)-Messungen wurden an den NEI-Proben mit den unterschiedlichen Dicken durchgeführt. Um die Ferroelektrizität der NEI-Schicht zu charakterisieren, P -V Kurven von TaN/NEI (3,6 nm)/Ge, TaN/NEI (6 nm)/Si0,7 Ge0.3 und TaN/NEI (10 nm)/TaN-Kondensatoren sind in Fig. 4a, b bzw. c gezeigt. Die NEI-Schicht weist einen niedrigeren P . auf als die gemeldeten Werte von HfZrO2 (HZO) [14], was darauf zurückzuführen ist, dass das Volumenverhältnis von ZrO2 Nanokristall in Al2 O3 Matrix ist ziemlich niedrig. Man sieht, dass die Restpolarisation P r des NEI-Films nimmt mit zunehmender Filmdicke zu. P-V Kurven in Fig. 4c zeigen, dass die Ferroelektrizität der NEI-Schicht abnimmt, während die Glühtemperatur von 450 auf 550 °C ansteigt. Es wird darauf hingewiesen, dass der Grund für das nicht geschlossene P-V Schleifen liegt daran, dass tatsächlich ein Leck vorhanden ist. Es wurde berichtet, dass der resultierende Offset bei einem elektrischen Feld von null abnimmt, wenn der Spannungs-Sweep-Bereich verringert wird [3, 15, 16]. Die Amplituden- (oben) und Phasenbilder (unten) von 3,6 nm, 6 nm und 10 nm NEI wurden gemessen, wie in Fig. 5a, b bzw. c gezeigt. Wie in Fig. 6 gezeigt, zeigen Muster, die die entgegengesetzte Polarität anzeigen, die auf die Oberfläche von NEI auf TaN geschrieben sind, den deutlicheren Kontrast mit zunehmender Filmdicke.

a –c Gemessener P -V Kurven von TaN/NEI (3,6 nm)/Ge, TaN/NEI (6 nm)/Si0,7 Ge0.3 , bzw. TaN/NEI (10 nm)/TaN

a –c Amplituden- (oben) und Phasen- (unten) Bilder der PFM-Messung für 3,6, 6 bzw. 10 nm NEI auf TaN

a –c Phasenänderungscharakteristik von 3,6, 6 bzw. 10 nm NEI auf TaN. Es wird beobachtet, dass auf die Oberfläche der NEI-Schicht eine entgegengesetzte Polarität geschrieben werden kann

Ergebnisse und Diskussion

NEI-NCFET

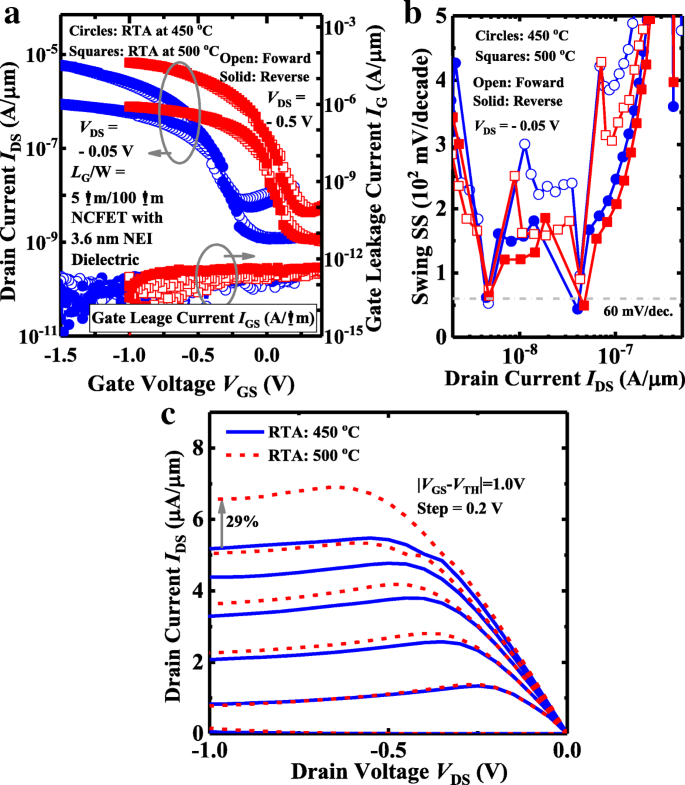

Abbildung 7a zeigt gemessenes I DS -V GS Kurven der NEI-NCFETs mit einer NEI-Dicke von 3,6 nm, getempert bei 450 °C und 500 °C. Die NCFETs zeigen eine geringe Hysterese, was auf die gute Anpassung zwischen der ferroelektrischen Kapazität und der MOS-Kapazität in den Transistoren hinweist. Die NCFETs zeigen den im Uhrzeigersinn induzierten NC-Effekt I-V Schleifen, die im Gegensatz zu den gegen den Uhrzeigersinn verlaufenden durch Ladungseinfang/-entnahme [17]. Die Gate-Leckage I G als Funktion von V GS des gleichen Gerätepaares zeigt, dass die Bildung von Nanokristallen in Al2 O3 erhöht nicht die Gate-Leckage. Abbildung 7b zeigt, dass die NCFETs die steilen SS-Punkte von unter 60 mV/Dekade für die Vorwärts- und Rückwärts-Sweeps erreichen. Die SS-Fluktuationen in NEI-NCFETs, die auch in NC-FinFETs beobachtet wurden [2, 18], könnten auf die Polarisationsumschaltung durch die verschiedenen ferroelektrischen Nanokristalle oder Domänen zurückzuführen sein. Das gemessene Ich DS -V DS Kurven für dasselbe Gerätepaar in Abb. 7c zeigen, dass bei ∣V GS − V TH ∣ = ∣ V DS ∣ = 1,0 V, der NCFET mit RTA bei 500 °C erreicht 29% größeres I DS im Vergleich zum bei 450 °C getemperten Transistor. Dies wird der Tatsache zugeschrieben, dass die Ladungsträgerbeweglichkeit in Kanal- und Kontaktwiderstandseigenschaften mit steigender Glühtemperatur verbessert werden kann [19]. Die typische durch die ferroelektrische Schicht induzierte Charakteristik, negativer differentieller Widerstand (NDR), wird im I . beobachtet DS -V DS Kurven für die bei den verschiedenen Temperaturen geglühten NCFETs.

a Gemessen I DS -V GS und ich G -V GS Kurven von NCFETs mit 3,6-nm-NEI, getempert bei 450 °C und 500 °C. b NEI NCFETs haben die Punkte unter 60 mV/Dekade für eine V DS Wert von − 0,05 V. c Ich DS -V DS Kurven für die NEI-NCFETs, die die offensichtlichen NDR-Phänomene zeigen. Bei 500 °C geglühter NC-Transistor erreicht einen I . von 29 % DS Verbesserung gegenüber dem Gerät mit RTA bei 450 °C bei einer Versorgungsspannung von 1,0 V

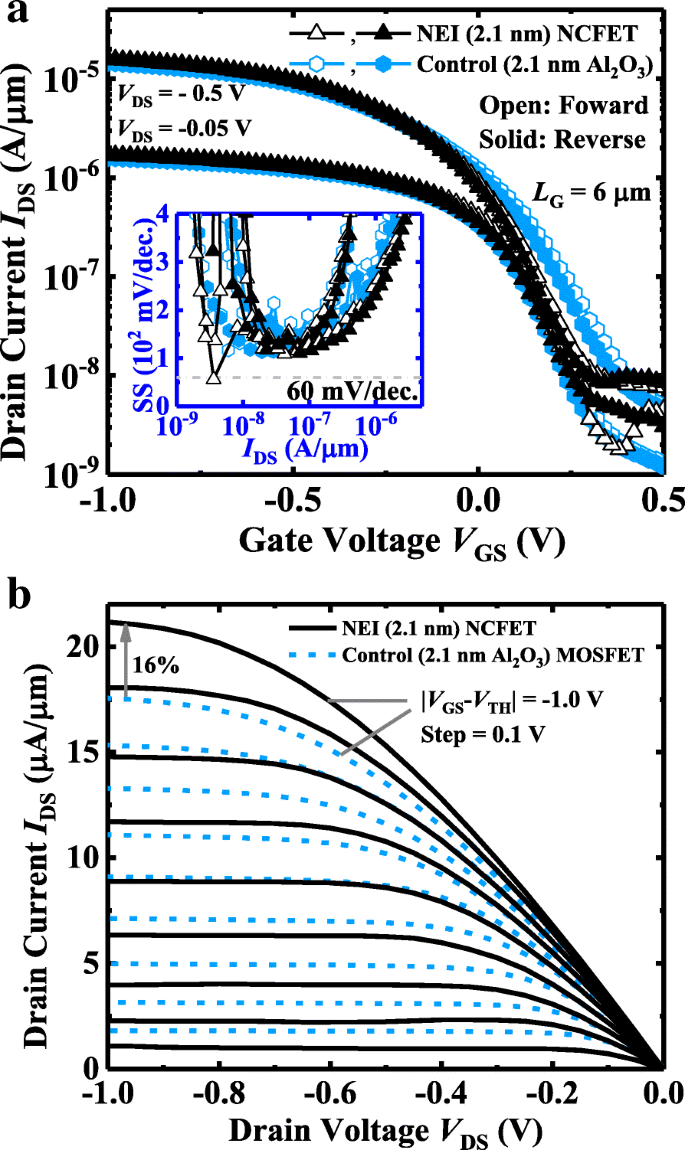

Abbildung 8a zeigt gemessenes I DS -V GS Kurven eines NEI-NCFET und eines Kontroll-MOSFET mit derselben Isolatordicke von 2,1 nm. Geräte haben ein L G von 6 µm. Der NCFET weist die hysteresefreien Eigenschaften auf. Der Einschub zeigt den Punkt SS vs. I DS Kurven für die Bauelemente, die zeigen, dass der NCFET im Vergleich zum Steuergerät eine verbesserte SS bis zur Schwellenspannung erreicht. Abbildung 8b zeigt das I DS -V DS Kurven des NEI-NCFET und des Steuer-MOSFET. NCFET zeigt das NDR-Phänomen für das niedrige V GS . Der NDR-Effekt entspricht den verbesserten Eigenschaften der Drain-induzierten Barrieresenkung (DIBL) im NCFET im Vergleich zum Steuer-MOSFET, wie in 8a gezeigt. Bei ∣V GS − V TH ∣ = ∣ V DS ∣ = 1,0 V, ein 16% I DS Beim NCFET wird eine Verbesserung im Vergleich zum Steuergerät erzielt. NCFET mit 2,1 nm NEI hat den weniger signifikanten NDR im Vergleich zum Transistor mit 3,6 nm NEI, was mit der Schlussfolgerung in [20] übereinstimmt.

a Ich DS -V GS Kurven eines NEI-NCFET und Steuer-MOSFET mit reinem Al2 O3 Dielektrikum. Beide Geräte verfügen über den 2,1-nm-Gate-Isolator. Der Einschub zeigt, dass der NCFET bis zur Schwellenspannung eine steilere SS als das Steuergerät hat. b Gemessen I DS -V DS Kurven für NCFET und Steuer-MOSFET. NDR wird für NCFET bei sehr niedrigen V . beobachtet GS . Bei ∣V GS − V TH ∣ = ∣ V DS ∣ = 1,0 V, NCFET erreicht 16% I DS Verbesserung gegenüber dem Steuergerät

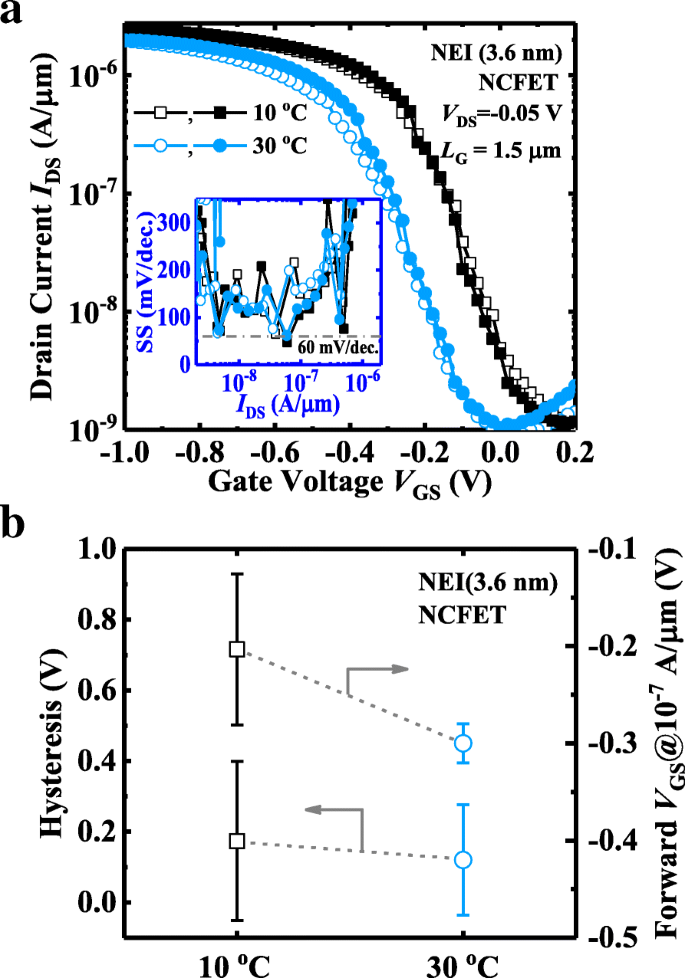

Hier wird die Temperaturabhängigkeit des NCFET mit 3,6 nm dickem NEI untersucht. Abbildung 9a zeigt I DS -V GS Kurven gemessen bei 10 °C und 30 °C. Der Einschub zeigt an, dass sich die SS-Leistung des Transistors bei den erhöhten Temperaturen nicht verschlechtert. Wenn die Temperatur steigt, wird das I -V Kurve verschiebt sich zu einem negativeren V GS aufgrund der dominierenden Wirkung der Ferroelektrizität, die dem Trend für einen herkömmlichen MOSFET entgegensteht. Abbildung 9b fasst die Verschiebungen der Hysteresespannung und der Vorwärtsschaltschwellenspannung mit der Temperatur zusammen. Weiter V GS verschiebt sich mit steigender Temperatur zu negativeren Werten, was möglicherweise auf ein erhöhtes E zurückzuführen ist c der NEI.

a Ich DS -V GS eines NEI (3,6 nm) NCFET gemessen bei 10 °C und 30 °C. Die Kurven zeigen erwartungsgemäß eine Verschiebung in Richtung negativerer Spannung mit steigender Temperatur. Einschub zeigt den Steilpunkt SS. b Statistische Diagramme der Hysterese (links) und des Vorwärts-V GS @ 10 −7 A/μm (rechts) für NCFETs mit 3,6-nm-NEI-Schicht. Weiter V GS verschiebt sich mit steigender Temperatur in die negative Richtung

NEI FeFET für nichtflüchtige Speicheranwendungen

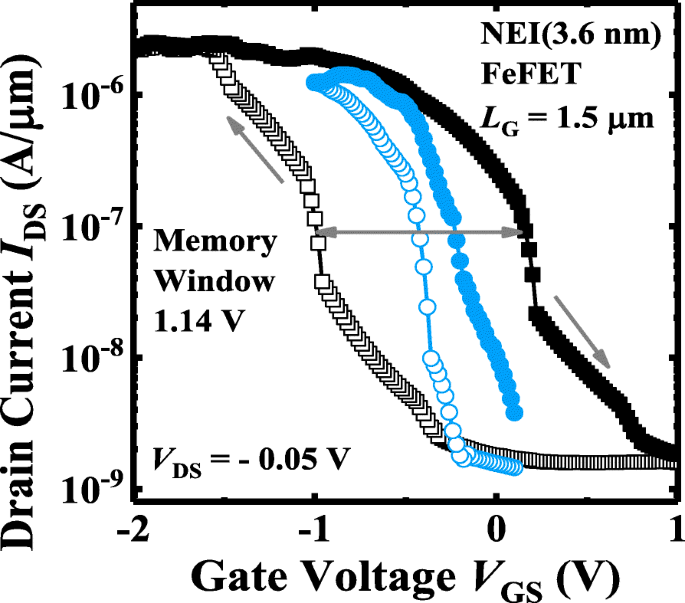

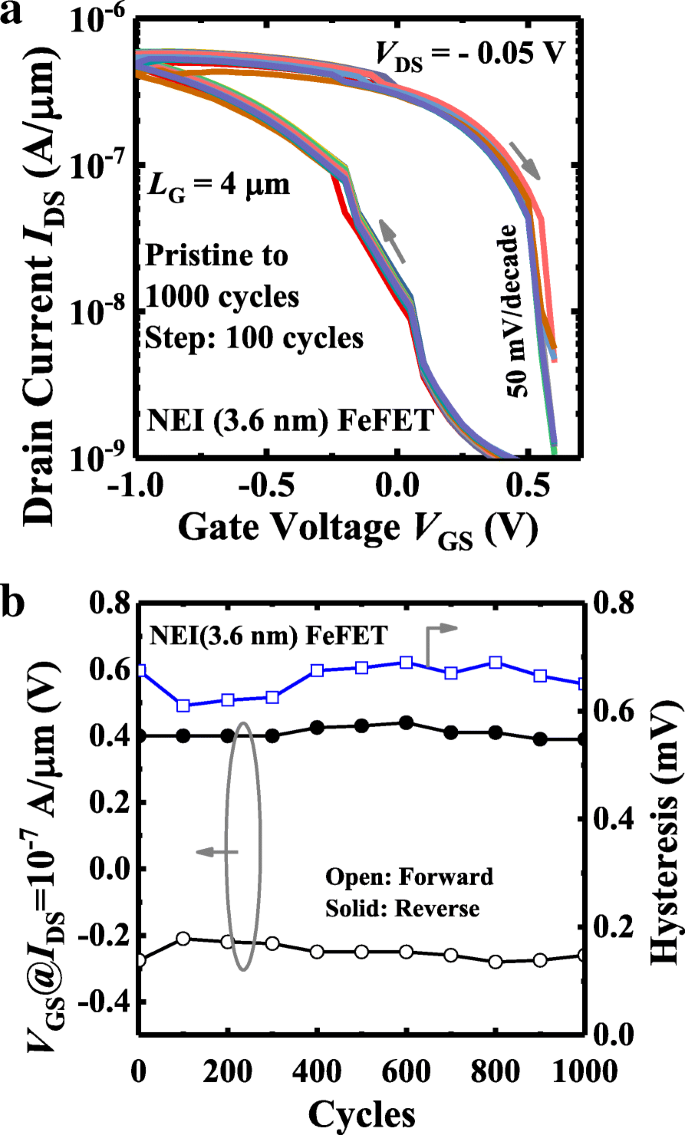

Durch Erhöhen des Bereichs von V GS Sweep kann die Hysteresespannung eines NEI-FeFET erhöht werden, um ein großes und stabiles Speicherfenster (MW) für Lese- und Schreibvorgänge zu erreichen. Wie in Abb. 10 gezeigt, zeigt ein FeFET mit 3,6-nm-NEI, dass das MW von 0,2 auf 1,14 V ansteigt, wenn V GS Wobbelbereich variiert von (0,1 V, − 0,1 V) bis (1 V, − 2 V). Die Gleichstrom-Sweep-Dauer einer anderen FeFET-Speichervorrichtung ist in Fig. 11a gezeigt, Fig. 11b veranschaulicht die Hysterese-Charakteristik als Funktion der Anzahl von Gleichstrom-Sweep-Zyklen. Stabiles I-V Hysteresefenster von ~ 0,65 V wird gesehen.

Für ein großes V GS DC-Sweep-Bereich, ein MW von 1,14 V wird für den NEI (3,6 nm) FeFET beobachtet

a Gemessen I DS -V GS Kurven für NEI (3,6 nm) FeFET, über 1000 DC-Sweep-Zyklen. b DC-Durchlauf-Ausdauermessungen zeigen, dass der NEI-FeFET ein stabiles MW über 1000 Zyklen hat

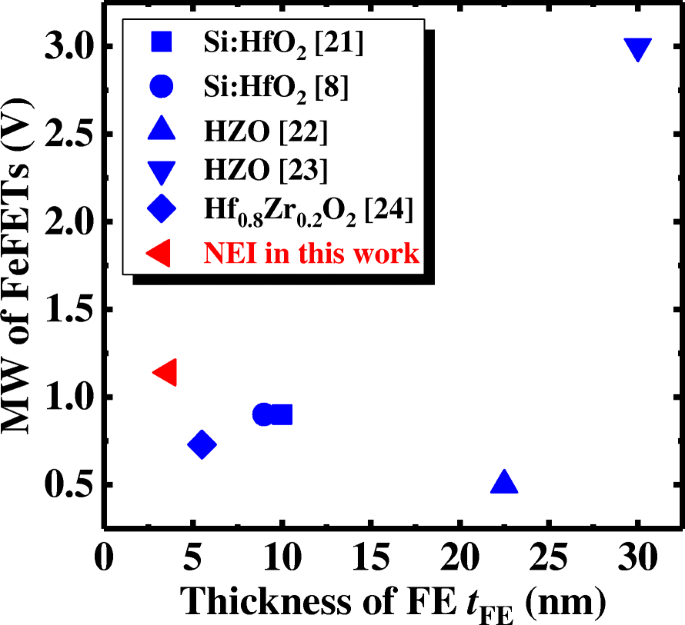

Abbildung 12 vergleicht das NEI-FeFET-Speicherbauelement mit den berichteten FeFETs in Bezug auf die MW- und FE-Schichtdicke [8, 21–24]. Es sollte beachtet werden, dass das NEI-FeFET-Bauelement in dieser Arbeit ein beträchtliches (> 1 V) MW mit der dünnsten berichteten FE-Dicke von 3,6 nm erreicht. Wir vermuten, dass es im Vergleich zu dotiertem HfO2 . einfacher ist, die stabile FE-Phase in NEI mit einer geringeren Dicke zu erreichen [28,29,30].

Benchmarking von NEI-FeFET-Speicherbausteinen mit gemeldeten FeFETs in Bezug auf MW und t FE . Dünnstes FE wird durch NEI FeFET-Speicherbaustein erreicht

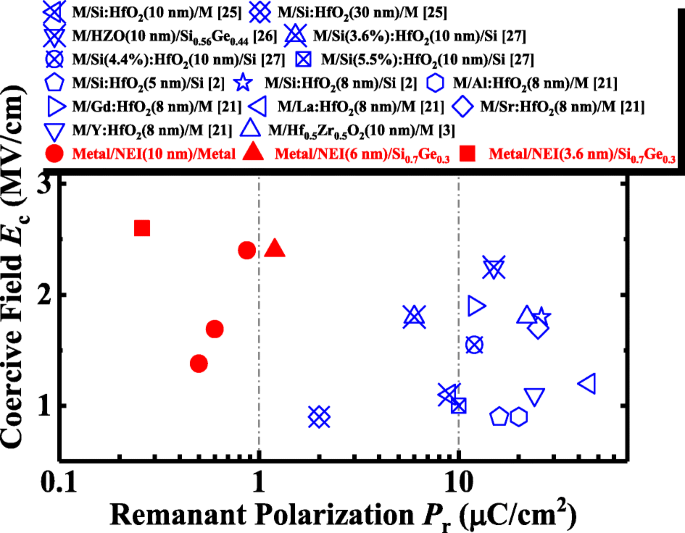

Schließlich die Vorteile des NEI FeFET von ZrO2 In amorphen Gate-Isolatoren eingebettete Nanokristalle werden diskutiert. Abbildung 13 vergleicht die NEI-Schicht mit dem gemeldeten dotierten HfO2 Filme [2, 3, 21, 25–27], bezüglich E c und P r . NEI kann einen viel niedrigeren P . erreichen r im Vergleich zu dotiertem HfO2 für ähnliche E c . Unsere Experimente haben gezeigt, dass ein P r unter 1 μC/cm 2 das erforderliche MW in den FeFETs bereitstellen kann. Eine übermäßige Polarisation könnte zu einer stärkeren Depolarisation führen, was zu schlechteren Retentionseigenschaften führt, was in [25] berichtet wurde. Außerdem können die FE- und DE-Eigenschaften der NEI-Schicht separat eingestellt werden:P r wird durch Erhöhen/Verringern des Volumens der FE-Nanokristalle verbessert/verringert, und wird durch Einbau anderer Elemente in die amorphe Matrix (z. B. . .) erhöht , LaAlO3 ), um die FeFET-Leistung zu optimieren.

Benchmarking von NEI-Schichten mit gemeldetem dotiertem HfO2 Filme, in Bezug auf E c und P r . NEI erreicht viel niedrigeres P r im Vergleich zu dotiertem HfO2 unter Beibehaltung ähnlicher E c. [2, 3, 21, 25,26,27]

Schlussfolgerungen

Neuartige FeFETs mit ZrO2 Nanokristalle eingebettet in ein amorphes Al2 O3 Gate-Isolierschicht berichtet. Physikalische Analysen zeigen, dass weniger als 0,5 % Zr in Al2 . enthalten sind O3 erzeugt ausreichend Ferroelektrizität für NCFET- und NVM-Anwendungen. Bei verschiedenen Messtemperaturen wird ein stabiler NC-Effekt beobachtet. Ein stabiler FeFET-Speicherbetrieb mit einem rekorddünnen (3,6 nm Gesamtdicke) Gate-Isolator wird demonstriert. Stabiles MW wird über 1000 DC-Ausdauerzyklen erreicht. Das vorgeschlagene NEI-FeFET-Design bietet einen Weg zum Verringern der Dicke der FE/DE-Gate-Isolatorschicht, um mit FinFETs mit sehr kleinen Finnenabständen kompatibel zu sein.

Abkürzungen

- Al2 O3 :

-

Aluminiumoxid

- ALD:

-

Atomlagenabscheidung

- BF2 + :

-

Borfluoridion

- DC:

-

Gleichstrom

- Ec:

-

Zwangsfeld

- FeFET:

-

Ferroelektrischer Feldeffekttransistor

- Ge:

-

Germanium

- GeOx :

-

Germaniumoxid

- HF:

-

Flusssäure

- HRTEM:

-

Hochauflösendes Transmissionselektronenmikroskop

- I DS :

-

Strom entziehen

- MOSFETs:

-

Metall-Oxid-Halbleiter-Feldeffekttransistoren

- MW:

-

Speicherfenster

- NC:

-

Negative Kapazität

- NDR:

-

Negativer Differenzwiderstand

- NEI:

-

Nanokristall-embedded-Isolator

- Ni:

-

Nickel

- Pr:

-

Restpolarisation

- RTA:

-

Schnelles thermisches Glühen

- SS:

-

Schwung unter der Schwelle

- TaN:

-

Tantalnitrid

- V GS :

-

Gatespannung

- V TH :

-

Schwellenspannung

- ZrO2 :

-

Zirkoniumdioxid

Nanomaterialien

- Sensoren und Prozessoren konvergieren für industrielle Anwendungen

- Multifunktionale Goldnanopartikel für verbesserte diagnostische und therapeutische Anwendungen:Eine Übersicht

- Fortschritte und Herausforderungen fluoreszierender Nanomaterialien für die Synthese und biomedizinische Anwendungen

- Advanced Atomic Layer Deposition Technologies für Mikro-LEDs und VCSELs

- Graphen- und Polymerverbundstoffe für Superkondensatoranwendungen:ein Rückblick

- Bewertung von Graphen/WO3- und Graphen/CeO x -Strukturen als Elektroden für Superkondensatoranwendungen

- Doppelfunktionen von V/SiOx/AlOy/p++Si-Gerät als Selektor und Speicher

- Antriebe für industrielle Kälte- und industrielle Kühlanwendungen

- Schwenkdrehmaschinen für Bohr- und Drehanwendungen

- Spezialmetalle für medizinische Geräteanwendungen