Eingebettet

RTOS Revealed-Serie anzeigen Dieser Artikel setzt den Blick auf Semaphoren fort. Semaphore Utility Services Nucleus RTOS hat vier API-Aufrufe, die mit Semaphoren verbundene Hilfsfunktionen bereitstellen:Semaphor zurücksetzen, Informationen über einen Semaphor zurückgeben, Anzahl der Semaphoren in

RTOS Revealed-Serie anzeigen Mailboxen wurden in einem früheren Artikel vorgestellt. Sie sind vielleicht die zweiteinfachste Methode der Inter-Task-Kommunikation – nach Signalen – die von Nucleus SE unterstützt wird. Sie bieten eine kostengünstige, aber flexible Möglichkeit, einfache Nachrichten z

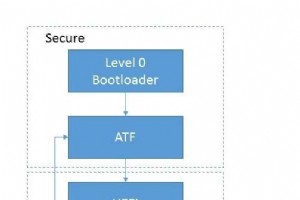

Seit ihrer Veröffentlichung im Jahr 2011 hat sich die ARMv8-Prozessorarchitektur auf dem Markt für mobile Geräte weit verbreitet. Nach den Prognosen des CEO von ARM Limited werden die Prozessoren dieser Generation bis 2020 einen Weltmarktanteil von bis zu 25 % erreichen. Es ist selbstverständlich, d

Anmerkung der Redaktion:Unser guter Freund Max sucht nach Vorschlägen für elektronische Taschenrechner und Löser. Nichts ist zu groß oder zu klein. Lassen Sie ihn wissen, welche Ihrer Meinung nach es wert sein könnten, in die Liste der Tools von EEWeb.com aufgenommen zu werden. Hin und wieder bri

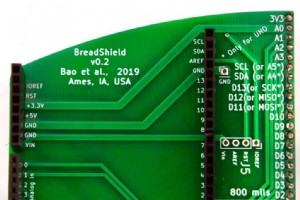

Ich erhalte außergewöhnlich viele E-Mails von Leuten, die Crowdfunding-Kampagnen für verschiedene Projekte gestartet haben. Dies liegt wahrscheinlich daran, dass ich gelegentlich selbst in Crowdfunding-Wasser getaucht habe und dass ich mehrere Kolumnen über Projekte gepostet habe, die mir besonders

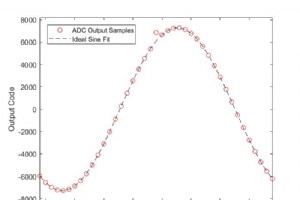

Da die Abtastrate von Hochgeschwindigkeits-Analog-Digital-Wandlern (ADCs) zugenommen hat, besteht auch das Problem von Codefehlern – auch als Sparkle-Codes bekannt – in den Ausgangsdaten des ADC. Ein Codefehler ist definiert als ein Fehler im Ausgabecode eines ADC, der einen definierten Schwellenwer

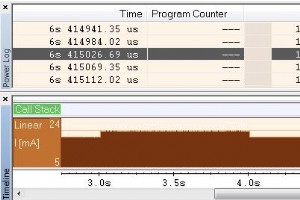

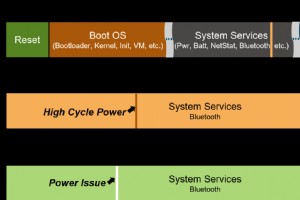

In meinem letzten Beitrag, „Grundlagen des Arm Cortex-M Low-Power-Modus“, haben wir die Grundlagen der Low-Power-Modi untersucht, die auf jedem Arm Cortex-M-Prozessor zu finden sind, und wie wir die WFI- und WFE-Anweisungen nutzen können, um einen Prozessor zu installieren schlafen. Die Frage, die w

Strom kostet tendenziell; hoher Strom kostet viel. Diese eher erzwungene Adaption des berühmten Zitats von Lord Acton erfasst zwei wichtige Aspekte des Halbleiterdesigns und des Stromverbrauchs. Betrachtet man den durchschnittlichen Stromverbrauch im Laufe der Zeit, ist klar, dass ein Chip mit hoher

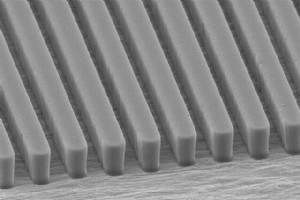

In den letzten Jahren haben wir eine Zunahme neuer Elektronikanwendungen erlebt, die kleinere Gehäuse, neue Formfaktoren, einen geringeren Stromverbrauch und eine erhöhte Funktionalität erfordern, einschließlich eingebetteter Signalverarbeitung, Sensoren, Bildgebungsschnittstellen und Power-Manageme

Seit den Anfängen des Elektronikdesigns, wo es Designs gab, gab es Fehler. Aber wo es Fehler gab, gab es unweigerlich Debugging, in einem epischen Wrestling-Match mit Fehlern, Fehlern und Fehlern, um festzustellen, welche sich durchsetzen würden – und wie gründlich. In vielerlei Hinsicht ist die En

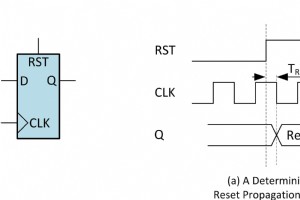

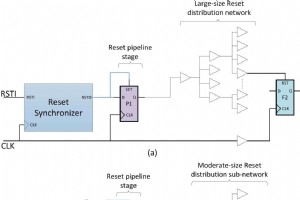

Ein Mangel an Koordination zwischen asynchronen Resets und synchronen Logiktakten führt zu zeitweiligen Ausfällen beim Einschalten. In dieser Artikelserie diskutieren wir die Anforderungen und Herausforderungen des asynchronen Resets und erkunden fortschrittliche Lösungen für ASIC- und FPGA-Designs.

Ein Mangel an Koordination zwischen asynchronen Resets und synchronen Logiktakten führt zu zeitweiligen Ausfällen beim Einschalten. In dieser Artikelserie diskutieren wir die Anforderungen und Herausforderungen des asynchronen Resets und erkunden fortschrittliche Lösungen für ASIC- und FPGA-Designs.

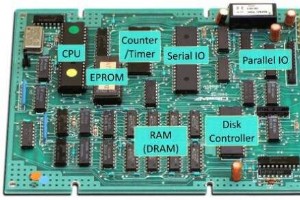

Es gibt eine Vielzahl von Echtzeit-Betriebssystemen (RTOS) im Internet (Klicken Sie hier, um eine „kleine“ Liste anzuzeigen). Viele dieser Angebote sind jedoch jetzt tote/nicht gewartete Projekte. Von den verbleibenden unterstützen die meisten nur einen Mikrocontroller oder eine Mikrocontrollerfami

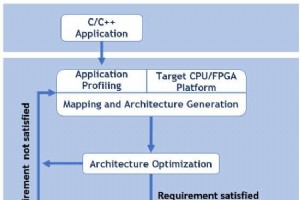

Vor kurzem organisierte Brian Bailey einen runden Tisch, der zu einem zweiteiligen Artikel mit dem Titel Supporting CPUs Plus FPGAs . führte . Die Experten diskutierten die sich entwickelnde Realität des Systemdesigns auf Basis von FPGAs und CPUs. Diese Diskussion befasst sich mit den jüngsten Entwi

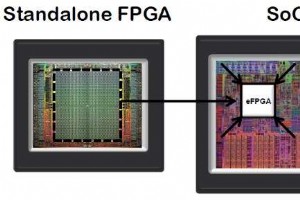

Ich interessiere mich schon lange für die Technologie von Achronix. Sie haben mein Interesse zum ersten Mal um 2004/2005 mit ihrer asynchronen FPGA-Struktur geweckt. Schließlich erreichte dies Geschwindigkeiten, die einem synchronen FPGA mit einer Taktrate von 2 GHz (wenn es ein solches Biest gäbe)

Hearables und wirklich kabellose Stereo-Ohrhörer werden immer beliebter, erreichen aber noch lange nicht ihr volles Potenzial. Diese winzigen Geräte können die Art und Weise, wie Menschen mit ihrer Umgebung interagieren, verändern und das tägliche Leben mit verbesserten Hörfähigkeiten, Freude und Si

Anmerkung der Redaktion:Drahtloses Design kann die besten Pläne für die Entwicklung vernetzter Geräte zunichte machen. Insbesondere eine falsch ausgelegte Antennenzuleitung kann während des Tests erst spät in der Entwicklungsphase schwer zu entdecken sein. Hier ist ein Vorgeschmack auf einen netten

In den letzten Jahren haben bedeutende Fortschritte in der automatischen Spracherkennung (ASR) zu einer Fülle von Geräten und Anwendungen geführt, die Sprache als ihre Hauptschnittstelle verwenden. Das IEEE-Spektrum Magazin hat 2017 zum Jahr der Spracherkennung erklärt; ZDNet berichtete von der CES

Im Laufe meiner Karriere war ich an der Entwicklung einer Reihe von FPGA-Designs für einige wirklich interessante Projekte beteiligt. Leider war ich auch an der Rettung mehrerer FPGA-Designs beteiligt, die stark in die Irre gegangen sind. Als ich an diesen Problemdesigns arbeitete, wurde klar, dass

Der Begriff 5G – also die fünfte Generation von Mobilfunknetzen oder drahtlosen Systemen – taucht heutzutage immer häufiger auf. Von Erstimplementierungen ist bereits im Jahr 2020 die Rede. Weniger wird darüber gesprochen, dass die 5G-Standards noch in Erwägung gezogen und definiert werden und sich

Eingebettet