Ein zeitkontinuierlicher Delta-Sigma-Modulator mit 100 MHz Bandbreite und 80 dB Dynamikbereich mit einer Taktrate von 2,4 GHz

Zusammenfassung

Die Bandbreite eines Δ Σ Modulator ist durch die Taktrate aufgrund der Anforderung des Oversampling-Verhältnisses begrenzt. Da sich die nanoskaligen CMOS-Prozesse schnell entwickeln, ist es möglich, zeitkontinuierlich eine große Bandbreite und einen hohen Dynamikbereich zu entwickeln Δ Σ Modulatoren für Hochfrequenzanwendungen. Dieses Papier schlägt ein zeitkontinuierliches Δ . 3. Ordnung vor Σ Modulator mit einer Single-Loop-Feedforward-Topologie. Dieser Modulator ist in einem 40-nm-CMOS-Prozess aufgebaut und erreicht einen Dynamikbereich von 80 dB und eine Bandbreite von 100 MHz bei einer Taktrate von 2,4 GHz. Der Modulator verbraucht 69,7 mW aus einer 1,2-V-Stromversorgung.

Einführung

Angetrieben durch die steigenden Anforderungen in drahtlosen Kommunikationsanwendungen wie Mobilfunkstandards entwickeln sich Analog-Digital-Wandler (ADCs) schnell weiter, um eine höhere Signalbandbreite (BW) und einen höheren Dynamikbereich (DR) zu unterstützen. Der Bedarf an BW im Kommunikationsstandard Long-Term-Evolution Advanced (LTE-A) ist auf 100 MHz gestiegen. Nyquist-ADCs, typischerweise Pipeline-ADCs [1, 2], wurden in Makro-Basisstationen wegen ihres hohen BW verwendet. Unverzichtbare Eingangspuffer zum Treiben von durch thermisches Rauschen begrenzten geschalteten Eingangskondensatoren und Anti-Aliasing-Filter verursachen jedoch einen erheblichen Stromverbrauch und eine erhebliche Designkomplexität. Darüber hinaus führt die Tatsache, dass Pipeline-ADCs auf einer genauen Zwischenstufenverstärkung beruhen, die den Breitband-Restverstärker mit hoher Verstärkung und die Kalibrierungstechnologie bestimmt, zu Komplexität und Verlustleistung. Δ Σ ADCs sind bekannt für ihre hohe Leistung und Energieeffizienz, die Oversampling- und Noise-Shaping-Technologie verwenden. Die Anforderung von Oversampling-Verhältnissen (OSRs), die typischerweise über 16 liegen [3–6], bestimmt jedoch die Abtastfrequenz jenseits von GHz. Vor kurzem Δ Σ ADCs mit mehr als 50 MHz BW wurden unter Verwendung von nanoskaligen CMOS-Prozessen vorgeschlagen, die eine Multi-GHz-Taktrate ermöglichen. Zuvor Hochfrequenz Δ Σ ADCs verwenden normalerweise zeitkontinuierliche (CT) Realisierungen [3–9] anstelle von zeitdiskreten (DT) Realisierungen. Letzteres wird durch eine Schaltung mit geschalteten Kondensatoren implementiert, und ihre Genauigkeit hängt von der Kondensatoranpassung ab, was bedeutet, dass ein robuster Betrieb unter Prozessschwankungen geboten wird. Außerdem wird eine überlegene Immunität gegenüber Taktjitter bereitgestellt, da die Zeitkonstanten der Kondensatoren und Schalter ausreichend klein sind. Da jedoch die Abtastoperation vor dem Modulator ausgeführt wird, wird das Anti-Aliasing-Filter benötigt. Andererseits werden Operationsverstärker in DT-Modulatoren aufgrund des Einschwingerfordernisses, um die Stabilität in den Stufen zu gewährleisten, mit einer breiteren Bandbreite mit Verstärkungsfaktor Eins (UGBW) als in CT-Modulatoren implementiert. Zusammenfassend können DT-Modulatoren eine hohe Genauigkeit, aber ein schmales Signal liefern [10, 11] und werden häufig verwendet, um Messanwendungen wie intelligente Sensoren und biomedizinische Bildgebung zu implementieren. Im Gegensatz dazu gab es weit verbreitetere Bemühungen, CT-Modulatoren für Hochfrequenzanwendungen zu entwickeln als DT-Modulatoren mit vergleichbarer Komplexität und Leistungsaufnahme.

Das anspruchsvolle Designziel eines höheren BW in einem bestimmten Prozess bestimmt aufgrund der prozessbegrenzten Taktrate einen niedrigeren OSR. Um einen ausreichenden DR zu erreichen, ist eine aggressive Rauschformung erforderlich, die durch eine hohe Rauschübertragungsfunktionsordnung implementiert wird, die herkömmlicherweise durch eine Schleifenfilterkaskade durchgeführt wird und in früheren Arbeiten im Allgemeinen gleich oder größer als 3 ist. Die erhöhten Schleifenfilterordnungen verursachen jedoch Energieverbrauch, Instabilität und Designkomplexität. Die mehrstufige Noise-Shaping (MASH)-Architektur [6, 8], implementiert durch kaskadierte lokale Δ . niedriger Ordnung Σ Modulatoren ohne Rückkopplungspfad untereinander, wurde verwendet, um Stabilitätsprobleme zu mildern, jedoch mit Mismatch-Empfindlichkeit. Darüber hinaus erhält ein Modulator mit einem Multi-Bit-Quantisierer einen bedingt hohen DR mit einem exponentiell ansteigenden Komparatorbetrag.

Dieses Papier beschreibt einen CT-Modulator in 40-nm-CMOS, der 80 DR über 100 MHz BW mit 69,7 mW Verbrauch unter Verwendung eines 40-nm-CMOS-Prozesses erreicht. Dieses Papier ist wie folgt aufgebaut. Der Abschnitt „Methode“ beschreibt die Modulatortopologie und die Schaltungsimplementierung. Der Abschnitt „Ergebnisse und Diskussion“ zeigt simulierte Ergebnisse und der Abschnitt „Schlussfolgerung“ bietet eine Zusammenfassung dieser Arbeit.

Methode

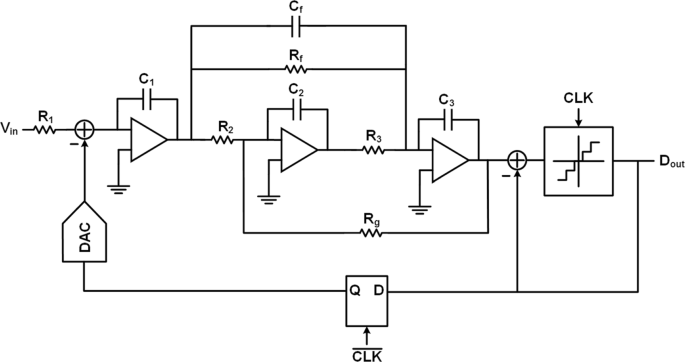

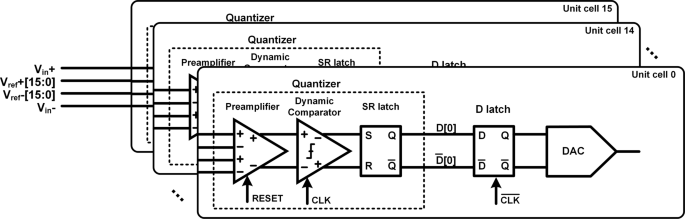

Abbildung 1 zeigt das Gesamtschema des vorgeschlagenen CT 3. Ordnung Δ Σ Modulator mit der Single-Ended-Struktur zur Vereinfachung. Die Rauschformung 3. Ordnung bietet einen guten Kompromiss zwischen DR und Schleifenstabilität. Der vorgeschlagene Modulator hat eine Abtastrate von 2,4 GHz mit einem 12 OSR. Der relativ hohe OSR in Δ Σ Modulatoren über 100 MHz BW gewährleisten einen hohen DR. Der Modulator enthält drei RC-Integratoren, einen 4-Bit-Quantisierer und einen 4-Bit-Stromsteuerungs-DAC. Die Integratoren werden durch innovative Feedforward-Verstärker mit geringer Verlustleistung für eine hohe Energieeffizienz implementiert. Der Rückkopplungs-DAC weist eine zusätzliche Verzögerung der halben Abtastperiodendauer auf, um die Metastabilitätsanforderung des Quantisierers zu lockern. Ein schneller Rückkopplungspfad, der von einem passiven Addierer implementiert und direkt vom Quantisierer angesteuert wird, realisiert die Excess-Loop-Delay (ELD)-Kompensation. Eine Feedforward-Topologie wird für die Energieeffizienz auf Kosten der Außerband-Signalübertragungsfunktion verwendet.

Gesamtschema der vorgeschlagenen 4-Bit-CT mit einer Schleife 3. Ordnung Δ Σ Modulator mit Feedforward-Topologie

Verstärkerdesign

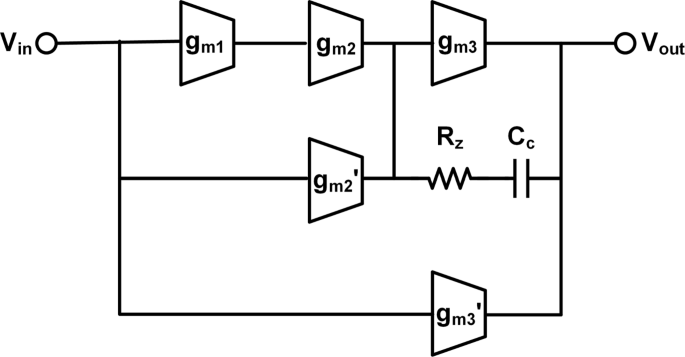

In Δ . ist eine hohe Verstärkerverstärkung erforderlich Σ Modulatoren, um die gewünschte Rauschtransformationsfunktion sicherzustellen. Die nanoskaligen Technologien, die verwendet werden, um eine Multi-GHz-Taktrate zu erreichen, leiden jedoch unter einer geringen intrinsischen Verstärkung. Daher wird ein dreistufiger Verstärker verwendet, um eine ausreichende DC-Verstärkung zu implementieren, wie in 2 gezeigt. Feedforward-Topologie und Miller-Kompensation werden kombiniert, um den Phasenspielraum ohne Einheitsverstärkungsbandbreitenreduzierung zu verbessern. Feedforward-Verstärker sind eine beliebte Lösung, um eine hohe Verstärkung mit adäquatem UGBW und Phasenspielraum (PM) zu erreichen. Der Nullpunkt der linken Hälfte der Ebene, der durch den Vorwärtskopplungspfad verursacht wird, soll die negative Phasenverschiebung der Pole effektiv aufheben. Es erfordert eine hohe Transkonduktanz der Verstärker auf dem Feed-Forward-Pfad und verbraucht viel Energie. Das vorteilhafte Schema der Wiederverwendung des Vorspannungsstroms spart Energie, während es g . begrenzt m Werte. Unzureichende g m verursacht typischerweise den Nullpunkt jenseits des UGBW und kann keinen angemessenen Phasenspielraum bereitstellen. Eine optimierte Nullstelle, die sich unterhalb des gesamten UGBW befindet, wird durch Hinzufügen eines Miller-Kompensationskondensators und eines Nullungswiderstands bereitgestellt.

Topologie des vorgeschlagenen dreistufigen Feedforward-Verstärkers mit Miller-Kompensation

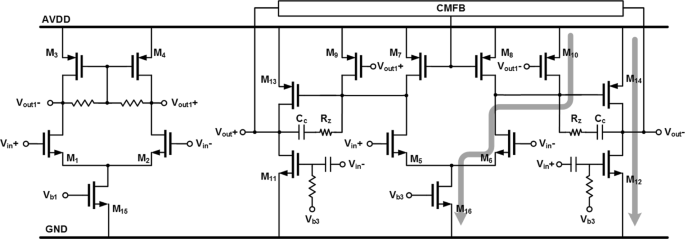

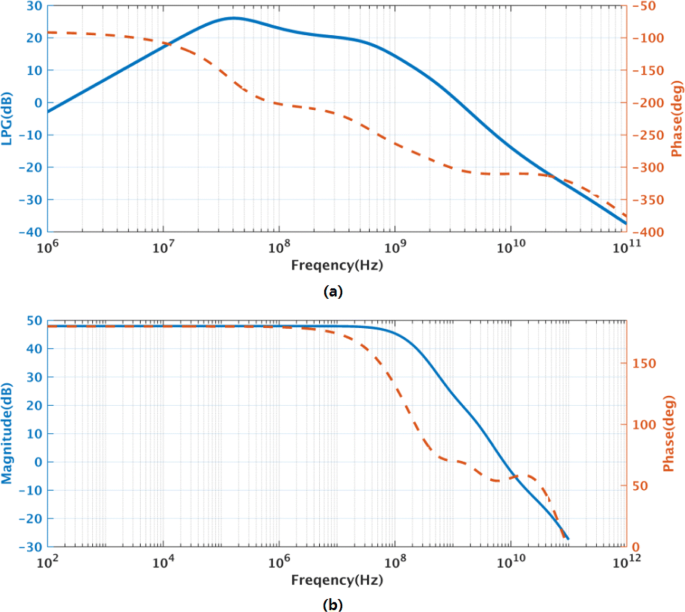

Abbildung 3 zeigt das Schaltbild des Verstärkers auf Transistorebene, der im ersten Integrator verwendet wird. Transistoren M 1−4 bilden die Eingangsstufe des Verstärkers, während die Transistoren M 9,10 und M 13,14 bilden die zweite bzw. dritte Stufe. Transistoren M 5−8 und M 11,12 schaffen zwei Hochgeschwindigkeits-Feedforward-Pfade zwischen Eingang und Ausgang, während die Vorspannungsströme mit den Verstärkern der zweiten und dritten Stufe geteilt werden. Der Gleichtaktausgang der ersten Stufe (CM) ist lokal festgelegt. Der Ausgangs-CM der zweiten und dritten Stufe wird durch einen Rückkopplungspfad der zweiten Stufe über einen CMFB-Verstärker fixiert, M 7,8 und M 13,14 . Abbildung 4 a zeigt die simulierte Open-Loop-Antwort des Verstärkers des ersten Integrators nach dem Layout mit allen Lasten, während Abb. 4 b die Closed-Loop-Antwort zeigt. Der erste Integrator erreicht 3,6 GHz UGBW und 57,8 ∘ von PM mit allen Ladeeffekten, während 10,5 mW von einer 1,2-V-Versorgung verbraucht werden. Der zweite und der dritte Integrator verwenden die gleiche Topologie, jedoch mit skalierten Vorspannungsströmen und erreichen UGBW von 4,7 und 3,3 GHz und PM von 58,0 und 57,8 ∘ bei einem Verbrauch von 4,3 bzw. 17,3 mW.

Schaltplan auf Verstärkertransistorebene

Die nach dem Layout simulierten Ergebnisse des Verstärkers im 1. Integrator. a Open-Loop-AC-Antwort; b Close-Loop-AC-Reaktion

Quantizer und DAC

Wie das Schema des Quantisierers und des DAC in Fig. 5 gezeigt ist, besteht jede aus 16 Einheitszellen. Der Quantisierer ist als 4-Bit-Flash-ADCs mit 16-Level-Encoder realisiert, der aus einer 17-Tap-Widerstandsleiter generiert wird. Der Quantisierer, dessen Betriebsdauer von ELD auf weniger als eine halbe Abtastperiode verlangt wird, um die Schleifenstabilität zu gewährleisten, ist ein Schlüsselblock zur Begrenzung des maximalen BW.

Das vereinfachte Schema der Quantisierer und der DACs

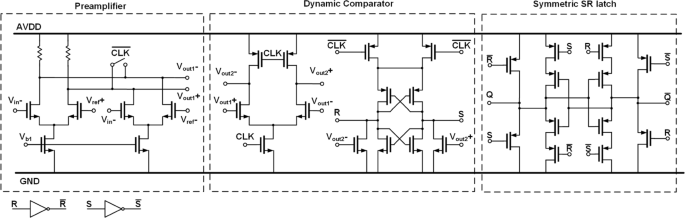

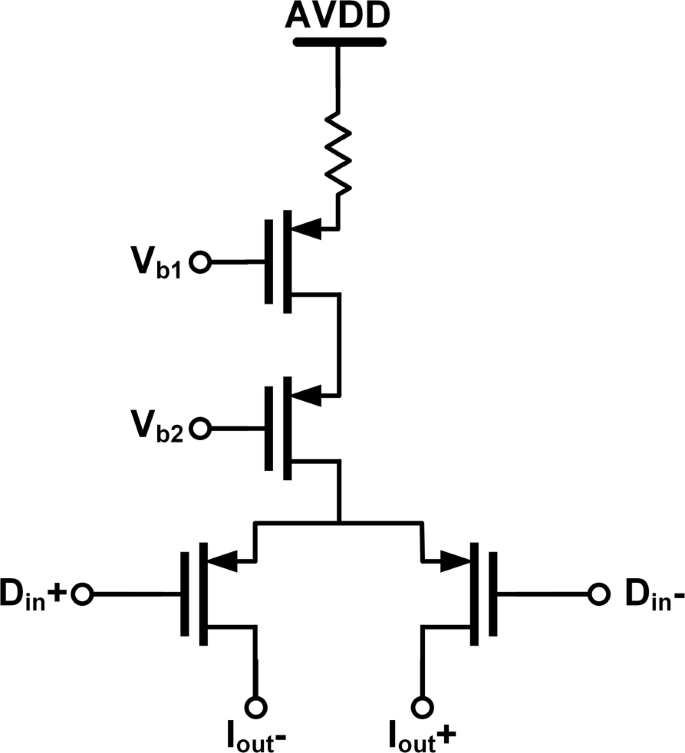

Um Hochgeschwindigkeits-Flash-ADCs zu implementieren, wird eine dreistufige Komparatorarchitektur verwendet, die aus einer Vorverstärkerstufe, einer dynamischen Komparatorstufe und einem symmetrischen Set-and-Reset-(SR)-Latch[12] besteht, wie in Fig. 6 dargestellt. Der Vorverstärker für die eingangsbezogene Offset-Reduzierung besteht aus zwei Widerstandslast-Differenzialpaaren mit einem Reset-Schalter, der über die Ausgänge geschaltet ist, um eine schnelle Wiederherstellung zu ermöglichen. Im Gegensatz zu herkömmlichen dynamischen Komparatoren sind das Differentialpaar und die kreuzgekoppelten Inverter in zwei Teile geteilt, um die Menge an Transistoren in jedem Strompfad für Niederspannungsversorgungen zu minimieren. Wenn der Takt auf den hohen Pegel wechselt, beginnen dynamische Komparatoren, die eingangsabhängige Vergleichsentscheidung zu treffen. Dann werden die beiden Ausgänge jedes dynamischen Komparators beide auf 0 zurückgesetzt, wenn die Taktrückkehr von hoch auf niedrig geht, was die Regeneration und das Zwischenspeichern des symmetrischen SR-Latch auslöst. Da in jedem Zweig nur ein Transistor aktiv ist, führt die symmetrische SR-Latch-Struktur zu einer starken Lasttreiberfähigkeit. Es ermöglicht eine kleine Transistorgröße mit signifikanter Abschaltgeschwindigkeit und geringem Stromverbrauch. Außerdem führt dies zu gleichen Verzögerungen beider Ausgangssignale. Die D-Latches vor den DAC-Einheiten sind in Bezug auf den Pegel des Taktsignals niedrigpegelempfindlich, wodurch eine halbe ELD-Dauer sichergestellt wird. Die Schaltung auf Transistorebene der stromsteuernden DAC-Einheit ist in Fig. 7 gezeigt.

Schaltung auf Transistorebene eines Einheitselements des vorgeschlagenen Quantisierers

Das Element der PMOS-Stromsteuerungs-DAC-Einheit

Ergebnisse und Diskussion

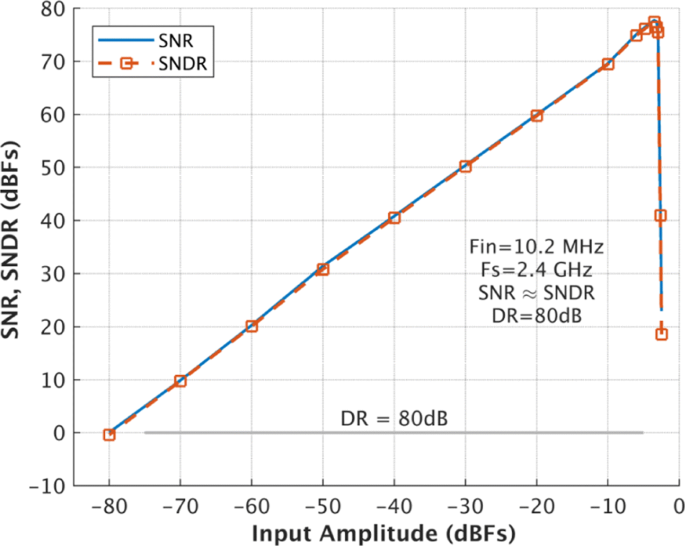

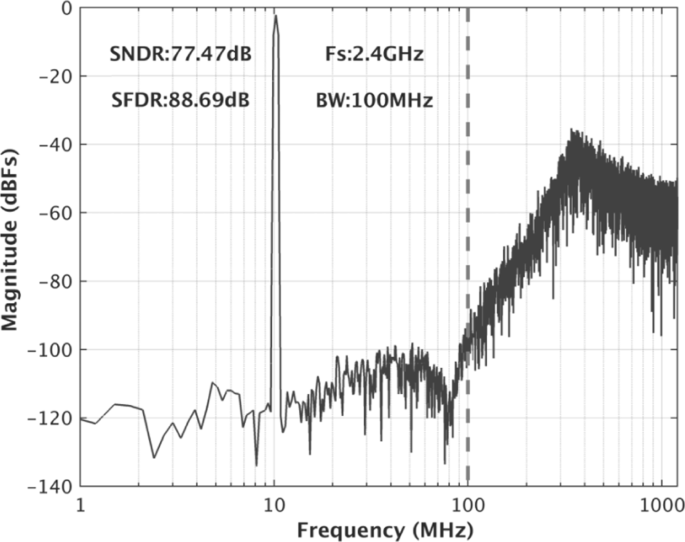

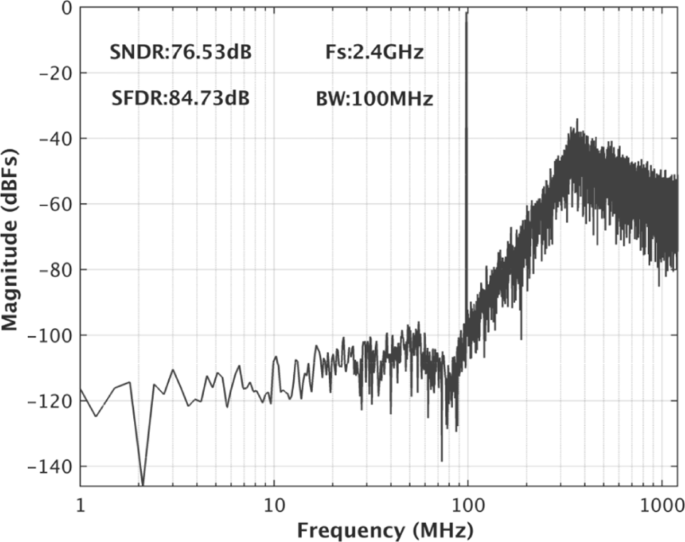

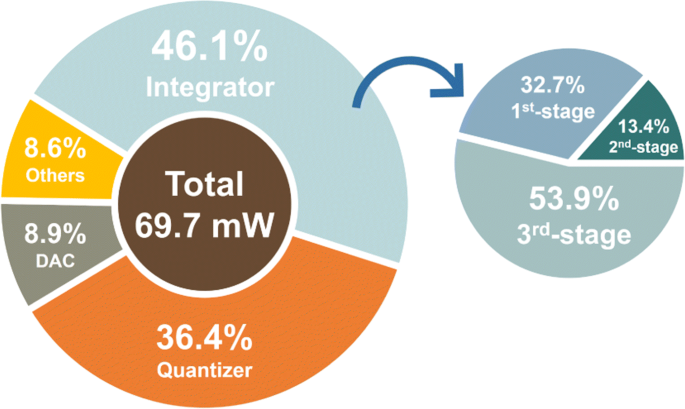

Der Prototyp Δ Σ Modulator ist in einem 40-nm-CMOS-Prozess aufgebaut. Wie die nachsimulierten Ergebnisse des SNR und SDNR gegenüber der Eingangsamplitude bei 10,2 MHz in Fig. 8 gezeigt sind, wird ein DR von 80 dB erreicht. Die Abbildungen 9 und 10 zeigen die simulierten Spektren mit einem − 3,52-dBF-Einzeltoneingang bei 10,2 MHz bzw. 97 MHz, da 0 dBF dem 2,4 Vss-Modulator-Full Scale entspricht. Der SNDR beträgt 77,47 dB bzw. 76,53 dB. Wie in Abb. 11 dargestellter Durchbruchsverbrauch kostet der Modulator 69,7 mW Leistungsaufnahme. Der Integrator, der Quantisierer und der DAC verbrauchen jeweils 32,1 mW, 25,4 mW und 6,2 mW. 6,0 mW Leistung wird von den anderen Strömen verbraucht, einschließlich Taktpuffern, Stromvorspannungen und Spannungsreferenzen. Der Modulator erreicht einen Schreier FOM von 171,6 dB basierend auf DR. Tabelle 1 vergleicht diese Arbeit mit mehreren zuvor veröffentlichten Arbeiten. Der vorgeschlagene Modulator erreicht ein breites BW mit dem höchsten FOM.

Post-simuliertes SNR und SNDR im Vergleich zur Eingangssignalamplitude mit einem 10,2-MHz-Eingang

Die postsimulierten Spektren mit einem Einzeltoneingang bei 10,2 MHz

Die postsimulierten Spektren mit einem Einzeltoneingang bei 97 MHz

Die postsimulierte Aufschlüsselung des Stromverbrauchs

Schlussfolgerung

In dieser Arbeit haben wir einen 4-Bit-CT 3. Ordnung vorgeschlagen Δ Σ Modulator mit einer Single-Loop-Feedforward-Topologie. Dieser Modulator ist in einem 40-nm-CMOS-Prozess aufgebaut und erreicht 80 dB DR über 100 MHz BW bei einer Taktrate von 2,4 GHz. Die Verstärkerkonstruktion mit geringer Verlustleistung führt zu einer hohen Energieeffizienz, und der Modulator verbraucht 69,7 mW aus einer 1,2-V-Stromversorgung und erreicht einen Schreier-FOM von 171,6 dB.

Verfügbarkeit von Daten und Materialien

Alle während dieser Studie generierten oder analysierten Daten sind in diesem veröffentlichten Artikel enthalten.

Abkürzungen

- ADC:

-

Analog-Digital-Wandler

- BW:

-

Bandbreite

- CT:

-

Kontinuierliche Zeit

- DR:

-

Dynamikumfang

- DT:

-

Diskrete Zeit

- ELD:

-

Überschleifenverzögerung

- LTE-A:

-

Langzeitentwicklung Advanced

- OSR:

-

Oversampling-Verhältnisse

- PM:

-

Phasenreserve

- UGBW:

-

Unity-Gain-Bandbreite

Nanomaterialien

- DIY einfachste IV9 Numitron-Uhr mit Arduino

- Hochgeschwindigkeits-3D-Druck mit AION500MK3

- Vollständige Terahertz-Polarisationskontrolle mit erweiterter Bandbreite über dielektrische Metaoberflächen

- Herstellung von nanoskaligen Gruben mit hohem Durchsatz auf Polymerdünnschicht unter Verwendung der AFM-Spitzen-basierten dynamischen Pfluglithographie

- RGO und dreidimensionale Graphen-Netzwerke modifizierte TIMs mit hoher Leistung gemeinsam

- Graphen/Polyanilin-Aerogel mit Superelastizität und hoher Kapazität als hochkompressionstolerante Superkondensatorelektrode

- Polarisationskonverter mit steuerbarer Doppelbrechung basierend auf einer hybriden volldielektrischen Graphen-Metaoberfläche

- Hochleistungsfähige organisch-nanostrukturierte Silizium-Hybridsolarzelle mit modifizierter Oberflächenstruktur

- Die extrem verbesserte Photostromantwort in topologischen Isolator-Nanoblättern mit hoher Leitfähigkeit

- Multifunktionales Gerät mit schaltbaren Funktionen der Absorption und Polarisationsumwandlung im Terahertz-Bereich