Auswirkungen von Ätzvariationen auf die Ge/Si-Kanalbildung und die Geräteleistung

Zusammenfassung

Während der Bildung von Ge-Fin-Strukturen auf einem Silizium-auf-Isolator-(SOI)-Substrat haben wir festgestellt, dass der Trockenätzprozess sorgfältig kontrolliert werden muss. Andernfalls kann es zu einer Überätzung von Ge oder der Bildung eines unerwünschten Ge-Rippenprofils kommen. Wenn der Ätzprozess nicht gut kontrolliert wird, wird die obere Ge/SOI-Struktur weggeätzt und nur die Si-Fin-Schicht verbleibt. In diesem Fall weist das Gerät abnormale Eigenschaften auf. Der Ätzprozess entwickelt sich zu einem kritischen Schritt bei der Skalierung und Verpackung von Geräten und beeinflusst Versuche, die Packungsdichte zu erhöhen und die Geräteleistung zu verbessern. Daher wird vorgeschlagen, den Betrieb des Plasmareaktors durch Simulationen zu optimieren, um nicht nur die verwendeten Prozessparameter anzupassen, sondern auch die eingesetzte Hardware zu modifizieren. Wir werden übergangslose Ge-Geräte entwickeln, indem wir aktualisierte Herstellungsparameter verwenden. Außerdem möchten wir Fehlanpassungsversetzungen an der Grenzfläche eliminieren oder Gewindeversetzungen reduzieren, indem wir zyklische thermische Glühprozesse anwenden, um das Ziel zu erreichen, eine schwebende Struktur von epitaktischen Ge-Schichten mit hoher Qualität zu erhalten.

Hintergrund

Eine Möglichkeit, die Ansprechgeschwindigkeit von Halbleiterbauelementen zu erhöhen und ihren Energieverbrauch zu reduzieren, besteht darin, einen Halbleiter mit einer hohen Trägermobilität zu verwenden. Beispiele für solche Materialien umfassen Ge sowie seine Legierungen und Verbindungen. Wenn jedoch eine Struktur durch Stapeln einer Schicht eines Halbleitermaterials auf einem Substrat eines anderen Halbleiters gebildet wird, können Probleme auftreten. Zum Beispiel kann der Unterschied in den Gittergrößen des Halbleitersubstrats und der darüber liegenden Schicht eines anderen Halbleitermaterials Versetzungen verursachen, die eine nachteilige Wirkung auf die Leistungsfähigkeit der Vorrichtung haben können. Herkömmlicherweise wird zur Herstellung von Ge-basierten Halbleitervorrichtungen, die ein Si-Substrat umfassen, eine dickere Pufferschicht oder Opferschicht (z. B. eine Si/Ge-Pufferschicht) auf dem Siliziumsubstrat gebildet. Anschließend wird eine epitaktische Ge-Schicht auf der Si/Ge-Pufferschicht aufgewachsen. Als nächstes werden nacheinander anisotrope und isotrope Ätzprozesse durchgeführt, um einen Teil der Pufferschicht zu entfernen und die epitaxiale Ge-Schicht zu erhalten. VLSI-Geräte müssen einen hohen Treiberstrom, einen geringen Leckstrom im Sperrzustand und eine niedrige Versorgungsspannung aufweisen, um eine hohe Leistung einschließlich eines geringen Standby-Stromverbrauchs und einer reduzierten dynamischen Verlustleistung sicherzustellen. Derzeit sind dehnungsverstärkte Mobilität, High-k/Metall-Gate und dreidimensionale (3D) Bauelementarchitektur am 22-nm-Knoten [1] einige der Technologien, die für die kontinuierliche Skalierung komplementärer Metalloxid-Halbleiter ( CMOS) Geräte mit einem Si-Kanal. Neben Eigenschaften wie hoher Mobilität werden neue Bauelementarchitekturen wie die von Gate-all-around (GAA) [2] und Ultrathin-Body-Feldeffekttransistoren (FETs) [3] benötigt, um die elektrostatische Kontrolle im Sub . zu verbessern -10 nm Knoten. Ge-basierte GAA-pFETs [4] und nFETs [5] mit Inversionsmodus (INV) wurden demonstriert. Die Übergangsbildung in Ge-INV-Vorrichtungen ist jedoch aufgrund der geringen Dotierstofflöslichkeit, der schnellen Dotierstoffdiffusion und des geringen thermischen Budgets ein kritischer Punkt. Um diese Probleme zu lösen, wurden als Alternativen übergangslose (JL)-Bauelemente [6] vorgeschlagen, die einen stark dotierten Kanal mit dem gleichen Trägertyp wie dem der Source/Drain-(S/D)-Gebiete verwenden. Die schnelle Skalierung von Transistoren erfordert jedoch die Entwicklung neuer und effektiverer Bauelemente, die mit modernen Transistoren mithalten können. In den letzten Jahren haben sich JL-FETs als vielversprechende Transistoren der nächsten Generation erwiesen. Der JL-FET ist im Grunde ein Widerstand, bei dem die mobile Trägerdichte durch das Gate gesteuert werden kann. Im EIN-Zustand existiert aufgrund der relativ hohen Dotierungskonzentration im Kanalgebiet ein großer Bodystrom; zu diesem Strom wird der Oberflächenakkumulationsstrom addiert Die Dotierung im JL-FET muss hoch sein, um eine geeignete Stromansteuerung zu erreichen, während der Gerätequerschnitt klein genug sein muss, damit das Gerät ausgeschaltet werden kann . Bei hochdotierten JL-FETs unterliegen die Ladungsträger jedoch einer erheblichen Störstellenstreuung, wodurch der Ansteuerstrom deutlich verschlechtert wird [7]. Darüber hinaus haben JL-FETs die Vorteile, dass sie einfach herzustellen sind und im Gegensatz zu INV-Bauelementen eine hohe Ladungsbeweglichkeit und eine niedrige Gate-Kapazität aufweisen [8,9,10,11,12]. Kürzlich wurden Ge-JL-FET-pMOSFETs mit doppeltem Gate [13] und körpergebundenem Tri-Gate [14] auf Germanium-auf-Isolator-Substraten bzw. Bulk-Si demonstriert.

Da mikroelektronische Bauelemente weiter schrumpfen und die Prozessanforderungen immer strenger werden, wird die Plasmamodellierung und -simulation als Werkzeug für Design, Steuerung und Optimierung von Plasmareaktoren immer attraktiver [15]. Es werden verschiedene Techniken verwendet, um das Verhalten von Plasmaprozessen basierend auf der Ungleichheit der Längen- und Zeitskalen zu simulieren. Eine der Simulationstechniken, Computational Fluid Dynamics (CFD), wird häufig verwendet, um die Strömungsfelder für Konstruktionsmerkmale vorherzusagen und experimentelle Grenzen zu extrapolieren. Seine Modellierung wurde angewendet, um das Phänomen der Strömungsmischung zu untersuchen [16], aber seltene Studien im Ätzprozess. Daher schlug diese Studie vor, das thermische Strömungsfeld von Plasmareaktoren für den Ätzprozess im Detail zu charakterisieren und dann numerische Parameter abzuleiten, die für Experimente von Vorteil sein können.

In dieser Arbeit wurde Ätzen durchgeführt, um suspendierte epitaktische Ge-Schichten über Si sowie anderen Legierungshalbleitern für die Geräteintegration zu bilden. Die simulierten Ergebnisse werden durch Experimente validiert; Daher werden Anfangs- und Randbedingungen sowie Parameter im numerischen Modell modifiziert, um die Datenzuverlässigkeit zu erhöhen. Wir gehen davon aus, dass durch Experimente und Simulationen optimale Parameter erhalten werden können, um die Ätztechniken zu verbessern, und diese Transistorentwicklung durch eine höhere Qualität des Herstellungsprozesses sowie niedrigere Produktionskosten erfüllen.

Methoden/Experimental

Die Ausgangssubstrate waren SOI-Wafer mit einer 70-nm-Top-Siliziumschicht (p-Typ, 9–18 cm). Die Wafer wurden mit den Verfahren RCA Standard Clean 1 (SC-1) und RCA Standard Clean 2 (SC-2) gereinigt, um vorhandene organische Stoffe, unerwünschte Metalle und Partikel zu entfernen. Anschließend wurde in entionisiertem Wasser gespült und in N2 . getrocknet . Der Ge-Film wurde in einem epitaktischen Niederdruckreaktor zur chemischen Gasphasenabscheidung (Epsilon 2000, ASM) unter Verwendung von 10 % GeH4 . abgeschieden als Vorläufer. Als Trägergas wurde Wasserstoff verwendet. Vor der Abscheidung des Ge-Films wurde eine in situ HCl-basierte Vorbehandlung bei 850 °C und 10 Torr durchgeführt, um die Waferoberfläche vorzubereiten. Die Substrattemperatur wurde dann auf 400 °C geändert, um einen Ge-Film auf dem SOI-Wafer unter Verwendung von 10 % GeH4 . wachsen zu lassen . Die Dicken der abgeschiedenen Ge-Filme wurden mittels Transmissionselektronenmikroskopie (TEM, thermische Emission vom Schottky-Typ, 0,5–200 kV) bestimmt. Die Kristallinitäten der Ge-Filme wurden mittels Röntgenbeugungsanalyse (XRD) untersucht (D8A, Bruker, CuKα-Strahlung, λ = 1.5408 Å, 20–70°). Darüber hinaus wurden Ω–2θ-Scans um den (004)-Beugungspeak mit einem X’Pert MRD (PANalytical)-System durchgeführt. Ein zweifacher Ge-{400}-Kristallkollimator mit Kanalschnitt wurde verwendet, um die CuKα1-Strahlung zu selektieren. Während der Standard-XRD-Messungen wurde die Probe in horizontaler Position fixiert und der Strahler- und Detektorarm des Diffraktometers im θ–θ-Modus bewegt. Die reziproke Raumabbildung wurde im Modus mittlerer Auflösung unter Verwendung des oben erwähnten Kristallkollimators durchgeführt; Auf dem Detektorarm vor dem Szintillationszähler waren 0,4 mm breite Schlitze vorhanden. Die Dicken der Ge-Schichten wurden durch Ellipsometrie-Messungen bestimmt (M2000, J. A. Woollam Co., = 193–1690 nm). Die Finne wurde durch anisotropes Plasmaätzen unter Verwendung von Cl2 . gebildet /HBr-Gas. Nach der Bildung des ZrO2 /TiN-Gate, den S/D wurde B implantiert (1 × 10 15 cm −2 , 15 keV) und aktiviert durch schnelles thermisches Glühen bei 550 °C für 30 s.

Hochselektives Trockenätzen des Germanium-Mechanismus

Elektronen- und Neutralreaktionen sind isotrop, während Ionenreaktionen stark gerichtet sind und mit der angelegten Vorspannung variieren. Durch Einstellen der Vorspannungsleistung können die Ionen entlang der gewünschten Richtung beschleunigt werden, um die Ätzreaktion zu unterstützen. Es ist allgemein anerkannt, dass Br nicht spontan mit Si reagiert und dass energiereiche Ionen benötigt werden, damit die Reaktion abläuft. Ionen-unterstützte Br- und Cl-Atome können unter Aktivierung spontan mit Ge- oder Si-Atomen reagieren, um die flüchtigen Produkte GeBr4 . zu bilden , GeCl4 , SiBr4 , und SiCl4 , die von der Substratoberfläche desorbiert werden und abgepumpt werden können. Diese ionenunterstützte chemische Reaktion von Si mit Br hat sich als stark anisotrop erwiesen. Höhere vertikale Ätzraten wurden unter Verwendung von HBr für Schwankungen der Vorspannungsleistung erzielt, was bestätigt, dass die Zugabe von HBr in Cl2 kann die Ätzrate erhöhen [17]. Da Cl- und Br-basierte Plasma Ge und Si durch einen ionenunterstützten Mechanismus ätzen, ist die Energie von Ionen wie Br + , Br 2+ , HBr + , Cl + , und Cl2 + kann durch Vorspannen des Substrathalters gesteuert werden. Es gibt keine ausgeprägte Änderung der seitlichen Ätzrate durch Variieren der Vorspannungsleistung sowohl für das Ätzen an der oberen Oberfläche als auch an der Einschnürungsfläche. In den mit HBr-Mischungen geätzten Finnenstrukturen wurden im Einschnürungsbereich Unterätzungen gefunden, da die seitliche Ätzung durch die Defekte entlang der Ge/Si-Grenzfläche verstärkt wurde. Außerdem beeinflusst die Maske möglicherweise die Formentwicklung aufgrund des Auftreffens der Seitenwand durch den Ionenfluss. Dieses Phänomen wird verstärkt, wenn das Profil tiefer wird und die seitliche Ionengeschwindigkeitskomponente zunimmt. Aufgrund der hohen Winkelabhängigkeit des HBr-Plasma-Ätzprozesses [18] kann daher geschlossen werden, dass die Kristallstruktur an der Ge/Si-Grenzfläche aufgrund der teilweise gebundenen Atome aus den Fehlanpassungsversetzungen und der relativ schwachen Ge-Ge- und Ge-Si-Bindungen. Durch Anpassen des Verhältnisses von HBr/Cl2 und Vorspannungsleistung können während der Herstellung von Ge-Vorrichtungen verschiedene Arten von flossenartigen Strukturen erhalten werden. Die Ätzeigenschaften von Ge und Si sind sehr ähnlich. Gase, die Si ätzen, ätzen Ge normalerweise mit einer größeren Rate. Die Stärke der Ge- und Si-Bindungen beträgt Ge-Ge = 263.6 ± 7.1 kJ mol −1 und Si-Si = 325 ± 7 kJ mol −1 [2]. Es wurden verschiedene Vorspannungsleistungen angelegt, um die vertikale Ätzrate durch gerichtete Beschleunigung der Ionen einzustellen. Bilder wurden nach dem Gate-Stack-Prozess aufgezeichnet. Die vertikale Ätzrate wurde aus der Filmhöhe relativ zum Oxidsubstrat berechnet. Laterale Ätzraten wurden aus zwei Teilen der Finne bestimmt:der lateralen Ätzung an der oberen Oberfläche der Finne und der Ätzung im Einschnürungsbereich nahe der Ge/Si-Grenzfläche. Zusammenfassend wurde experimentell festgestellt, dass die Vorspannungsleistung der kritischste Parameter im Ätzprozess ist und daher die Geräteeigenschaften entsprechend beeinflusst.

In dieser Studie wurden alle Ätzprozesse in einem TCP 9600 Reaktor von Lam Research durchgeführt. Dies ist ein transformatorgekoppelter Plasmareaktor, der eine separate Steuerung der Spulenleistung (obere Elektrode) und der Substratvorspannung (untere Elektrode) ermöglicht. Eine Helium-Rückseitenkühlung wurde eingebaut, um die Temperatur des Substrats effektiver steuern zu können. Die Proben wurden auf einem 6-Zoll montiert. Si-Trägerwafer mit Vakuumfett vor dem Einbringen in die Ätzkammer. HBr/Cl2 Chemie wurde für den anisotropen Ätzprozess genutzt. Der Prozessdruck wurde auf 10 mTorr kontrolliert. Der detaillierte experimentelle Aufbau und die Bedingungen sind in der Studie von Hsu et al. [4].

Physisches Modell

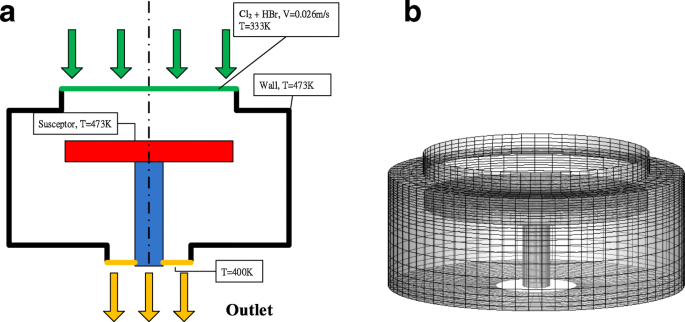

CFD wird verwendet, um auf die internen Informationen innerhalb des Reaktors zuzugreifen, und die Strömung wird aufgrund der höheren Knudsen-Zahl in der Kammer als laminar mit der Schlupfrandbedingung angesehen (Abb. 1). In der vorliegenden Simulation wird der thermische Plasmafluss in den Impulsgleichungen als Mischung betrachtet; Der Teilchentransport wird in den speziesspezifischen Gleichungen berücksichtigt und chemische Reaktionen sind an der Suszeptorwand beteiligt. Ein Modellfall für die Simulation ist in Abb. 3 dargestellt. Das Einlassgas ist eine Mischung aus Chlor (Cl2 ) und Bromwasserstoff (HBR). Die Mischungsgeschwindigkeit am Einlass beträgt 0,026 m/s bei einer Temperatur von 333 K. Der Suszeptor und die Kammerwand werden auf die Betriebstemperatur von 473 K erhitzt. Diese Plasmaströmung wird durch eine elektrische Vorspannung angetrieben und führt chemische Reaktionen an der Suszeptoroberfläche in a gleichmäßig, wiederholbar und schließlich aus dem Reaktor auszutragen. Nach Erstellung der Volumenkörpermodellierung durch die CAD-Software wurde das Netzsystem in strukturierten Gittern mit 50.000 Knoten konstruiert, wie in Abb. 3 gezeigt. Die transiente Erhaltungsgleichung für den Transport einer skalaren Größe ϕ wird durch die folgende Gleichung in Integralform dargestellt Form für ein beliebiges Kontrollvolumen V wie folgt [19]:

Physikalisches Modell zur numerischen Simulation eines Plasmareaktors. a Die Skizze der Reaktorkammer mit vorgegebenen Randbedingungen. b Netzsystem für numerische Simulationen

$$ \frac{d}{dt}\underset{V}{\oint}\rho \varphi\;dV+\oint \kern0.27em \rho \varphi \overset{\rightharpoonup }{v}\cdot \mathrm{ d}\overrightarrow{\mathrm{A}}=\oint\Gamma\mathrm{\nabla}\varphi\cdot\mathrm{d}\overrightarrow{\mathrm{A}}+{\int}_{\mathrm{ V}}{\mathrm{S}}_{\varphi}\mathrm{dV} $$ (1*)wobei ρ die Dichte angibt; \( \overset{\rightharpoonup }{v} \) ist der Geschwindigkeitsvektor; \( \overset{\rightharpoonup }{A} \) ist der Flächenvektor; V ist Volumen; Γ ist der Diffusionskoeffizient für ϕ und Sϕ ist der Quellterm von ϕ pro Volumeneinheit. Das Symbol ϕ kann für die Kontinuitätsgleichung durch 1 ersetzt werden, u , v , und w sind die Impulsgleichungen in X-, Y- und Z-Richtung und Ci für die Speziestransportgleichungen in der Reaktorkammer. Gl. (1*) kann in verallgemeinerten Koordinaten ausgedrückt werden, indem der Ansatz der Finite-Volumen-Methode für die Simulation verwendet wird. Gl. (1*) kann linearisiert und im Berechnungsbereich als Satz algebraischer Gleichungen ausgedrückt werden, die durch den SIMPLE-Algorithmus unter Verwendung der CFD-Technik [19] gelöst werden können. Es sei darauf hingewiesen, dass die meisten Halbleiterfertigungsvorrichtungen weit unter Atmosphärendruck arbeiten. Bei solch niedrigen Drücken befindet sich die Fluidströmung im Schlupfbereich und die normalerweise verwendeten schlupffreien Randbedingungen für Geschwindigkeit und Temperatur sind nicht mehr gültig. Der gegenwärtige Plasmafluss bei sehr niedrigem Druck befindet sich im Gleitbereich, der zwischen freiem Molekülfluss und dem Kontinuumsbereich liegt [20]. Daher werden in unseren numerischen Simulationen Schlupf-Randbedingungen für Geschwindigkeit und Temperatur zur Modellierung von Fluidströmungen auferlegt.

Die Halbleitermaterialien Si(s) und Ge(s) werden auf der erhitzten Suszeptoroberfläche weggeätzt, die durch die folgenden Oberflächenreaktionen bestimmt werden:

$$ {\mathrm{Cl}}_2+\mathrm{Si}={\mathrm{SiCl}}_4 $$ (2*.1) $$ 4\mathrm{HBr}+\mathrm{Si}={\mathrm {SiBr}}_4+2{\mathrm{H}}_2 $$ (2*.2) $$ 2{\mathrm{Cl}}_2+\mathrm{Ge}={\mathrm{GeCl}}_4 $$ (2*.3) $$ 4\mathrm{HBr}+\mathrm{Ge}={\mathrm{GeBr}}_4+2{\mathrm{H}}_2 $$ (2*.4)Die chemischen Reaktionen sind beim Si-Ätzen in Gl. (2*.1) und Gl. (2*.2), oder Ge-Ätzen in Gl. (2*.3) und Gl. (2*.4). Daher wird der Si-Ätzprozess durch eine Mischung aus Chlor und Bromwasserstoff in den folgenden Simulationen demonstriert.

Ergebnisse und Diskussion

Materialcharakterisierung

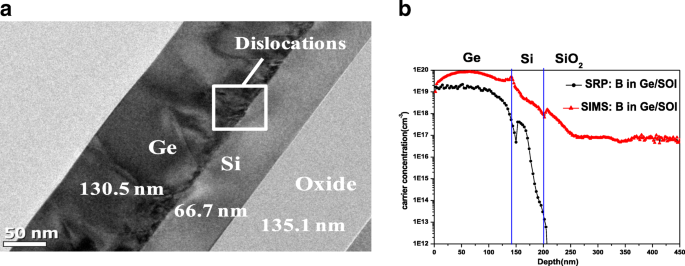

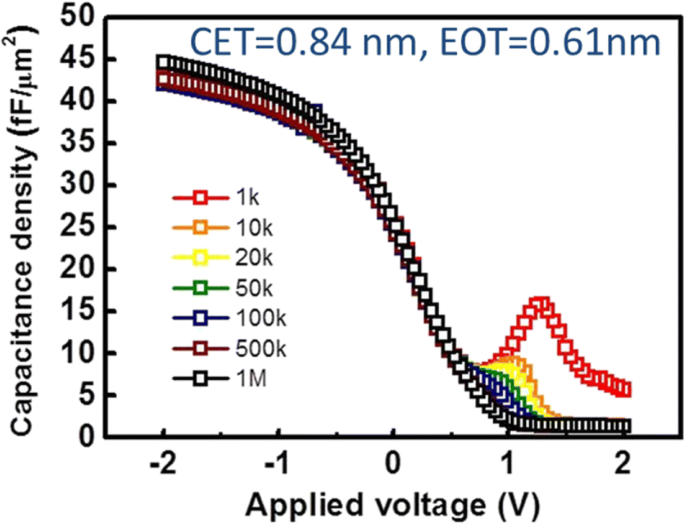

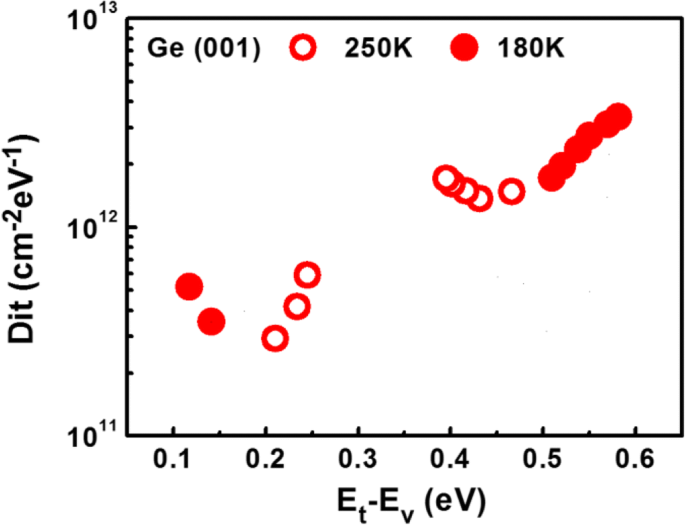

TEM-Querschnittsbilder der auf dem SOI-Substrat gebildeten Ge-Schicht sind in Fig. 2a gezeigt. Wie zu sehen ist, sind Fehlanpassungsversetzungen an der Ge/Si-Grenzfläche vorhanden; diese wiederum führen zu Durchdringungsversetzungen über den epitaktischen Ge-Film. Es wird angenommen, dass diese Durchdringungsversetzungen die thermische Fehlanpassung zwischen Ge und Si ausgleichen. Die meisten der Durchfädelungsversetzungen endeten innerhalb von 80 nm von der Grenzfläche; viele breiteten sich jedoch auch auf der Filmoberfläche aus. Der epitaktische Ge-Film auf dem SOI-Substrat wurde mit Bor implantiert und anschließend aktiviert, um die Dotierstoffverteilung und das Aktivierungsniveau zu untersuchen. Für den oberen 130-nm-Teil der Ge-Schicht betrug die Boraktivierungsrate ∼ 85%, wie in den PCOR-SIMS- und Spreading Resistance Profiling (SRP)-Profilen gezeigt. (siehe Abb. 2b). Im Fall des Bodens der Ge-Schicht nahe der Ge/Si-Grenzfläche sank die Lochkonzentration aufgrund des Vorhandenseins von Defekten und aufgrund der Messgrenzen von SRP deutlich. Im Fall der hergestellten Vorrichtungen wurde das defekte Ge nahe der Ge/Si-Grenzfläche durch selektives Ätzen entfernt; daher sollten die im Kanal durchgeführten PCOR-SIMS- und SRP-Messungen genau sein. Die maximale Aktivierungsstufe von ~ 3 × 10 19 cm −3 entspricht vollständig der konventionellen Aktivierungsgrenze. Beachten Sie, dass aufgrund der Niedrigtemperaturaktivierung (550 °C) während der Borimplantation das S/D in der Nähe des parasitären Si-Kanals hochohmig war (Abb. 2); dies verhinderte eine parasitäre Si-Leitung. Abbildung 3 zeigt die Kapazitäts-Spannungs-(CV)-Kennlinien des TiN/ZrO2 /Ge-Metall-Isolator-Halbleiter-Kondensatoren (MISCAPs). Um die Bildung eines instabilen GeOx . zu verhindern Schicht während der High-k-Dielektrikum-Abscheidung und dem Temperprozess nach der Abscheidung, das Nitrid-basierte Material Ge3 N4 und nicht GeO2 wurde als Grenzschicht auf der Ge(001)-Oberfläche durch ein NH3 . eingefügt /H2 Plasma-Fernbehandlung. Das ZrO2 Die Schicht wurde bei 250°C für 20 Zyklen durch Atomlagenabscheidung abgeschieden. Die gemessenen CV-Kurven zeigen keine Frequenzstreuung oder Dehnung von 1 KHz bis 1 MHz und sind konsistent. Der Verlust, der Fallenniveaus in der Nähe des ZrO2 . erzeugt /Ge-Grenzfläche, verschiebt die thermische Aktivierungsenergie für die Minoritätsträgererzeugung von derjenigen, die der p-Ge-Bandlückenenergie entspricht, auf die Mittellückenenergie. Die äquivalente Oxiddicke (EOT) beträgt 0,6 nm und der D es (Grenzflächenfallendichte) Wert ist ~ 3 × 10 12 cm 2 eV −1 in der Nähe der Mittellücke, gemessen mit der Niedertemperatur-Leitfähigkeitsmethode (siehe Einschub von Fig. 4).

a Das TEM-Bild des p-Typ-Ge auf SOI-Substrat. b Die SIMS- und SRP-Profile der in situ mit Bor dotierten Epi-Ge-Schicht auf SOI. Die Lochkonzentration ist im unteren defekten Ge in der Nähe der Ge/Si-Grenzfläche niedrig

C-V-Eigenschaften von TiN/ZrO2 /Ge MISCAPs mit EOT ~ 0.6 nm

Dit gemessen mit der Niedertemperatur-Leitfähigkeitsmethode

Simulation der Parameter des Reaktorbetriebs

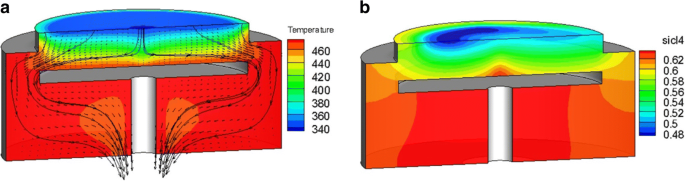

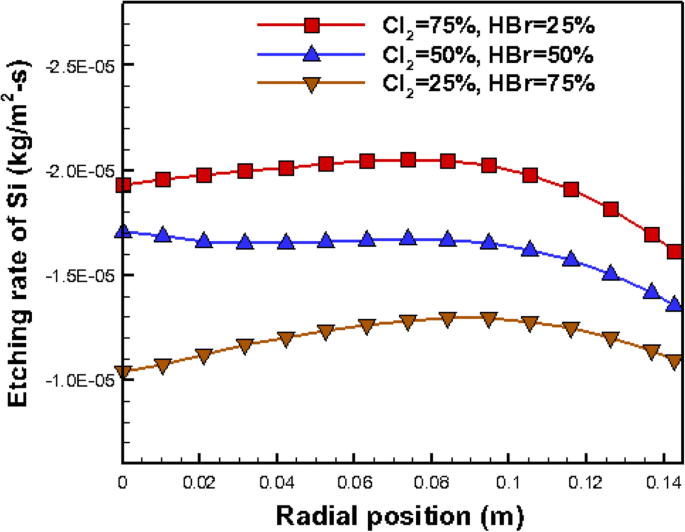

Ein typisches Modell von stationären laminaren Plasmaströmen wurde auf Hochgeschwindigkeits-Personalcomputern simuliert. Das Einlassgas ist eine Mischung aus Cl2 , das einen Massenanteil von 0,75 hat, und HBr, das einen Massenanteil von 0,25 hat. Fig. 5a veranschaulicht die Konturen des Niedertemperatureinstroms, der im Inneren bei höheren Temperaturen betrieben wird, und die Partikelpfadlinien in der Reaktorkammer. Abbildung 5b zeigt die Massenanteilkonturen des Produkts SiCl4, das eine niedrige Konzentration oberhalb des Suszeptors und eine hohe Konzentration unterhalb des Suszeptors zum Ausgang aufweist. Außerdem höherer Massenanteil an Cl2 erzielt eine gute Ätzleistung, und dieses Know-how wurde durch aktuelle Simulationen validiert, wie in Abb. 6 gezeigt. Die horizontale Achse repräsentiert entlang einer radialen Position auf dem Suszeptor und die vertikale Achse zeigt die Ätzrate (kg/m 2 s) von Si. Abbildung 6 zeigt, dass der bessere Ätzprozess durch die Einlassmischung von 75% Cl2 . archiviert wird und 25% HBr, und diese Mischung wurde verwendet, um Experimente in dieser Studie durchzuführen.

Konturen der Plasmaparameter im Reaktor. a Temperaturverteilung und Partikelpfadlinien r. b Massenanteilkonturen des Produkts SiCl4

Ätzraten von Si auf dem Suszeptor aus Gemischen von Einlassgasen mit verschiedenen Fraktionen

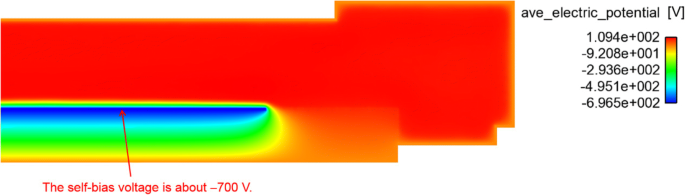

Ein weiterer Fall, der die Machbarkeit eines computergestützten Experiments zeigt, ist die Verteilung des elektrischen Potentials in der Kammer zum Plasmaätzen. Basierend auf dem zugrunde liegenden Mechanismus dieses Ätzprozesses wurde ein 2D-Simulationsmodell für die Verteilung der Plasmaleistungsdichte gemäß Abb. 7 entwickelt und zur Anpassung der Messdaten verwendet, um die Genauigkeit des Modells zu bestätigen und zu unterstützen das Experiment.

Simulation der elektrischen Potentialverteilung beim Plasmaätzen in der Kammer

Wie von Sugai [21] vorgeschlagen, kann die Selbstvorspannung mit den Kapazitäten der Hülle auf der HF-Elektrode (CK ) und Masseelektrode (CA ) und wie folgt ausgedrückt:

$$ {V}_{\mathrm{DC}}=\frac{C_{\mathrm{K}}-{C}_{\mathrm{A}}}{C_{\mathrm{K}}+{C }_{\mathrm{A}}}\ {V}_{\mathrm{RF}} $$ (3*)Gemäß den vorliegenden Simulationen, wie in Fig. 7 gezeigt, beträgt die Self-Bias-Spannung etwa – 700 V, was nahe am theoretischen Wert von – 650 V liegt, wie aus Gl. (3*). Daher wird vorgeschlagen, die Optimierung mittels Simulationen durchzuführen, um nicht nur die verwendeten Prozessparameter anzupassen, sondern auch die eingesetzte Hardware zu modifizieren. Dies trägt dazu bei, die Einheitlichkeit über die gesamte Auflage zu gewährleisten und führt zu qualitativ hochwertigen, kostengünstigen und optimierten Prozessen.

Geräteherstellung und -charakterisierung

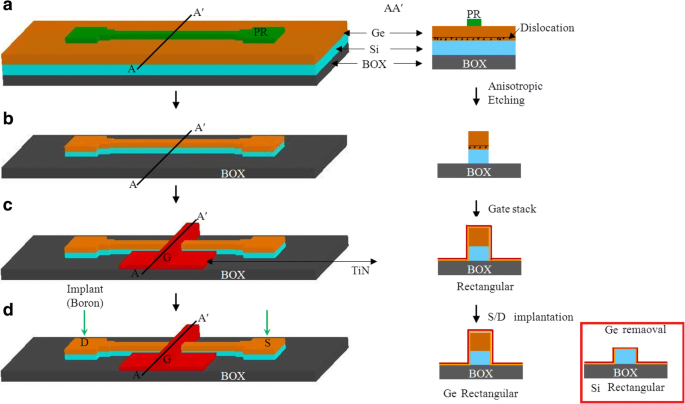

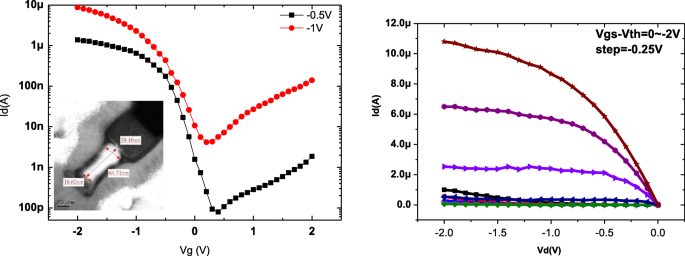

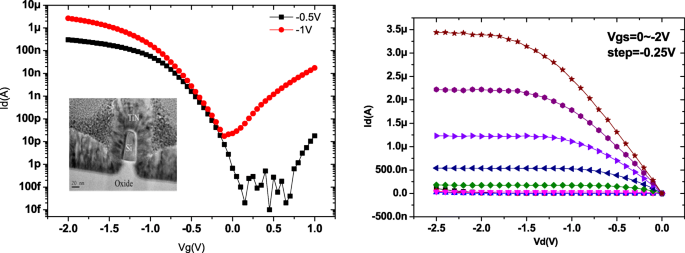

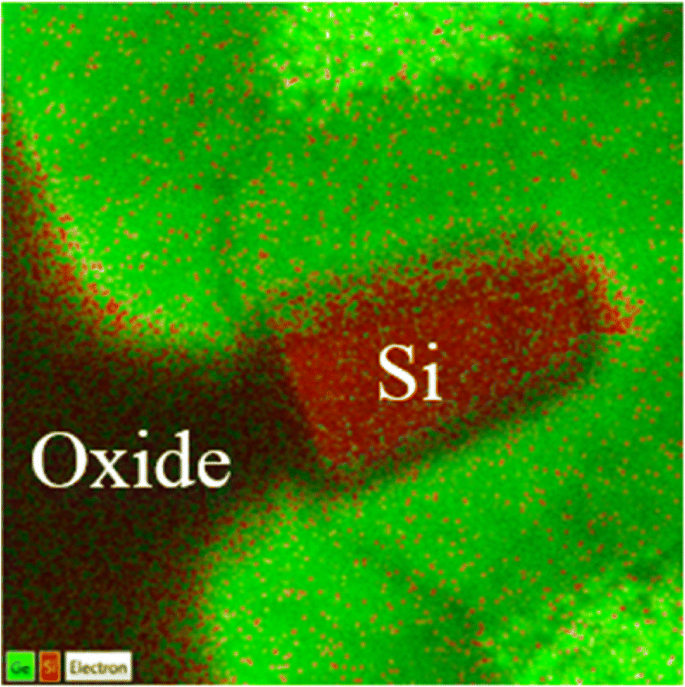

Die epitaktische Ge-Schicht wurde unter Verwendung von Elektronenstrahllithographie zu Finnen mit den gewünschten Strukturgrößen strukturiert. Die Finne wurde durch anisotropes Ätzen mit Cl2 . gebildet /HBr-basiertes Plasma zum Wegätzen des hochdefekten Ge in der Nähe der Ge/Si-Grenzfläche. Die Floating-Ge-Finne auf SOI wurde mit der höheren Ätzselektivität von Ge als Si und der erhöhten Ätzrate des defekten Bereichs gebildet [4]. A SiO2 Die Deckschicht wurde dann abgeschieden und wurde der Abstandshalter nach der Gatestrukturierung. Nach dem Definieren der aktiven Region werden die Gate-Stapel von ZrO2 Schicht wurden jeweils durch ALD gebildet. Die Kanalquerschnitte hergestellter Bauelemente sind in Abb. 8 dargestellt. Die Finnenbreite (W fin ) wird für die Kanalkonzentration von 8 × 10 19 . verwendet cm − 3 die mit der Van-der-Pauw-Methode auf einer deckenden Ge-Epi-Schicht auf SOI extrahiert wird. Beachten Sie, dass die Kanalsteuerbarkeit mit zunehmender Kanalkonzentration und zunehmendem W . abnimmt fin [12, 13]. Die große Kanalkonzentration erfordert das kleine W fin um die niedrige SS zu halten. Schließlich wurden die Gate-Elektroden definiert und abgeschieden. Abbildung 9 zeigt die Ausgangs- und Übertragungseigenschaften eines dreieckigen Ge-FinFET mit einer Finnenbreite (W fin ) von 18 nm und Gatelänge (L g ) von 90 nm. Das Ich an /Ich aus Verhältnis des Ge-JL-FET ist so hoch wie 10 5 und der unterschwellige Swing (SS) beträgt ~ 100 mV dec − 1 . Die Übertragungseigenschaften des Si-JL-FET sind in Abb. 10 dargestellt. Das I an /Ich aus Verhältnis des Si-JL-FET ist hoch wie ~ 10 8 , seine SS beträgt 90 mV dec − 1 , es ist L g ist 80 nm und sein W fin beträgt 20 nm. Abbildung 8 zeigt auch, dass die Spanne der Gatespannung, ΔV g , beträgt ungefähr 0,5 V und liegt nahe der Bandlücke von Ge (E g /q = 0,66 V). Dies bestätigt, dass das Ich d –V g Die in Fig. 8 gezeigten Kurven gelten für einen Ge-FinFET. Die Spanne der Gatespannung, ΔV g , in Abb. 6 gezeigt, beträgt ungefähr 1,8 V und liegt nahe der Bandlücke von Si (E g /q = 1.1 V), aber nicht das von Ge (E g /q = 0,66 V). Somit ist das Ich d –V g die in Fig. 9 gezeigten Kurven gelten für einen Si-JL-FET und nicht für einen Ge-JL-FET. Diese Beobachtung basiert auf der Physik von Halbleiterbauelementen und wird durch das experimentell bestimmte I . unterstützt d –V g Kurven der Ge- und Si-FinFETs sowie die Querschnitts-TEM/EDS-Si-Karten. Zwei Dinge sind aus den Einfügungen in Fig. 11 ersichtlich. Die Einfügungen zeigen die Ausgangs- und Übertragungseigenschaften des unerwarteten Si-JL-FET nach dem Überätzen von Ge; das Ich an /Ich aus Verhältnis dieses Geräts beträgt bis zu 10 8 . Sein EIN-Strom beträgt jedoch nur 17 μA μm − 1 bei − 1 V. Das hohe I an /Ich aus Verhältnis ist der Si-Schicht und nicht der Ge-Schicht zuzuschreiben. Wenn nur die Si-Schicht übrig ist, ist das Gerät eigentlich ein Si-JL-FET und kein Ge-JL-FET.

Schema der Geräteherstellung. a Flossenmusterung. Das Ausgangsmaterial ist Ge (130 nm) auf BOX. b Anisotropes Ätzen und Photoresist-Striping. c Gate-Bildung durch Atomlagenabscheidung von ZrO2 und TiN-Abscheidung. d Selbstjustierende Borimplantation auf S/D für guten Kontakt. Hinweis:die linke Seite ist das 3D-Schema und die rechte Seite ist die entsprechende Querschnittsansicht

Ich d –V g und ich d –V d Kurve für den Ge FinFET

Ich d –V g und ich d –V d für den Si-FinFET, nachdem das oberste Ge achtlos weggeätzt wurde. Obwohl ich an /Ich aus kann 10 8 . erreichen , sein Einschaltstromwert ist sehr niedrig

TEM-Mapping für die Kanalstruktur, die einem Überätzprozess unterzogen wird

Schlussfolgerungen

Wir bestätigen den Zusammenhang zwischen Simulationsmodell und Messdaten. Daher wird vorgeschlagen, die Optimierung mittels Simulationen durchzuführen, um nicht nur die verwendeten Prozessparameter anzupassen, sondern auch die eingesetzte Hardware zu modifizieren. Mit Hilfe numerischer Simulationen zur Ermittlung der Betriebsparameter des Rektors haben wir gezeigt, dass die Parameter für den Ätzprozess zur Bildung von Ge/Si-Kanälen experimentell optimiert werden können, um den Ätzprozess zu verbessern und die Entwicklung von Transistoren durch Verbesserung der Fertigungsqualität und Senkung der Produktionskosten. Die experimentellen Ergebnisse zeigten, dass die für Ge-FinFETs entwickelte Trockenätztechnik auch für die Herstellung von Tall-Fin-CMOS-Bauelementen äußerst nützlich ist.

Nanomaterialien

- Advanced Atomic Layer Deposition Technologies für Mikro-LEDs und VCSELs

- Tauchbeschichtungsverfahren und Leistungsoptimierung für elektrochrome Drei-Zustands-Bauelemente

- Grenzflächen-, elektrische und Bandausrichtungseigenschaften von HfO2/Ge-Stapeln mit in situ gebildeter SiO2-Zwischenschicht durch plasmaunterstützte Atomlagenabscheidung

- Substitutionsdoping für Alumosilikat-Mineral und überlegene Wasserspaltungsleistung

- Optische und elektrische Eigenschaften von Silizium-Nanodrähten, die durch stromloses Ätzen hergestellt wurden

- Die Auswirkungen des Li/Nb-Verhältnisses auf die Herstellung und photokatalytische Leistung von Li-Nb-O-Verbindungen

- Abstimmung der Oberflächenmorphologien und -eigenschaften von ZnO-Filmen durch das Design der Grenzflächenschicht

- Herstellung und photokatalytische Leistung von Hohlstruktur-LiNb3O8-Photokatalysatoren

- Die Kopplungseffekte von Oberflächenplasmonpolaritonen und magnetischen Dipolresonanzen in Metamaterialien

- Laserätzen und Lasergravieren