Kurz gesagt, VHDL ist eine Computersprache, die zum Entwerfen digitaler Schaltungen verwendet wird. Ich verwende den Begriff „Computersprache“, um VHDL von anderen, gebräuchlicheren Programmiersprachen wie Java oder C++ zu unterscheiden. Aber ist VHDL eine Programmiersprache? Ja, so ist es. Es i

Obwohl VHDL- und FPGA-Tools oft sehr teuer sind, ist es einfach, als Student kostenlos auf modernste Software zuzugreifen. Es gibt mehrere Simulatoren, Editoren und IDEs für die Arbeit mit VHDL. Dieser Artikel zeigt Ihnen, wie Sie zwei der beliebtesten Programme installieren, die von VHDL-Ingenieure

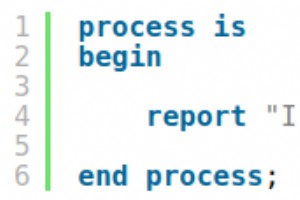

Wenn ich eine neue Programmiersprache lerne, fange ich immer gerne damit an, das Drucken zu lernen. Wenn Sie die Ausgabe von „Hello World!“ beherrschen, wissen Sie, dass die Umgebung funktioniert. Es zeigt Ihnen auch das Grundgerüst der Sprache, den absoluten Mindestcode, der erforderlich ist, um ei

Im vorherigen Tutorial haben wir gelernt, dass ein Prozess als Programmthread betrachtet werden kann. Wir haben auch erfahren, dass ein wait; Anweisung bewirkt, dass das Programm auf unbestimmte Zeit angehalten wird. Aber gibt es eine Möglichkeit, ein Programm auf einen anderen Zeitwert als ewig war

Im vorherigen Tutorial haben wir gelernt, wie man die Zeit mit wait for verzögert Aussage. Wir haben auch etwas über die Prozessschleife gelernt. Wir wissen jetzt, dass der Prozess-„Thread“ für immer in einer Schleife innerhalb des Prozesses schleifen wird, wenn wir es zulassen. Was aber, wenn wir

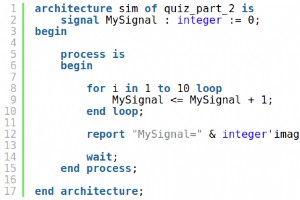

Im vorherigen Tutorial haben wir gelernt, eine Endlosschleife mit dem loop zu erstellen Aussage. Wir haben auch gelernt, wie man mit exit aus einer Schleife ausbricht Aussage. Aber was ist, wenn wir wollen, dass die Schleife eine bestimmte Anzahl von Wiederholungen durchläuft? Die For-Schleife ist d

Im vorherigen Tutorial haben wir gelernt, wie man eine For-Schleife verwendet, um über einen ganzzahligen Bereich zu iterieren. Aber was ist, wenn wir eine detailliertere Steuerung der Schleife wünschen als nur einen festen ganzzahligen Bereich? Wir können dafür eine While-Schleife verwenden. Die W

Damit haben Sie den ersten Teil der Basic VHDL Tutorial-Serie abgeschlossen. Herzliche Glückwünsche! Sie sind nur Stunden und Stunden und Stunden davon entfernt, ein echter VHDL-Experte zu werden. Aber Sie haben den ersten Schritt getan, und das ist jetzt der wichtigste Teil! Bevor wir fortfahren,

Im vorherigen Tutorial haben wir gelernt, wie man eine Variable in einem Prozess deklariert. Variablen eignen sich gut zum Erstellen von Algorithmen innerhalb eines Prozesses, sind aber für die Außenwelt nicht zugänglich. Wenn sich der Gültigkeitsbereich einer Variablen nur innerhalb eines einzelnen

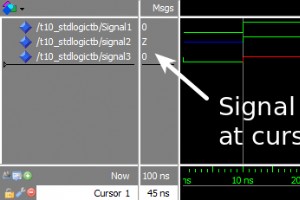

Im vorherigen Tutorial haben wir die Hauptunterschiede zwischen Signalen und Variablen kennengelernt. Wir haben gelernt, dass Signale einen größeren Anwendungsbereich haben als Variablen, die nur innerhalb eines Prozesses zugänglich sind. Wie können wir also Signale für die Kommunikation zwischen me

Im vorherigen Tutorial haben wir einen Bedingungsausdruck mit der Wait Until-Anweisung verwendet. Der Ausdruck sorgte dafür, dass der Prozess nur ausgelöst wurde, wenn die beiden Zählersignale gleich waren. Aber was wäre, wenn wir wollten, dass das Programm in einem Prozess verschiedene Aktionen bas

Sie sollten immer eine Vertraulichkeitsliste verwenden um Prozesse in Produktionsmodulen auszulösen. Empfindlichkeitslisten sind Parameter für einen Prozess, die alle Signale auflisten, auf die der Prozess empfindlich reagiert. Wenn sich eines der Signale ändert, wacht der Prozess auf und der darin

Der in VHDL am häufigsten verwendete Typ ist std_logic . Stellen Sie sich diesen Typ als ein einzelnes Bit vor, die digitale Information, die von einem einzigen physischen Draht übertragen wird. Die std_logic gibt uns eine feinkörnigere Kontrolle über die Ressourcen in unserem Design als integer Typ

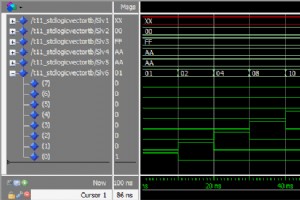

Der std_logic_vector Typ kann zum Erstellen von Signalbussen in VHDL verwendet werden. Die std_logic ist der am häufigsten verwendete Typ in VHDL und der std_logic_vector ist die Array-Version davon. Während die std_logic eignet sich hervorragend zum Modellieren des Werts, der von einem einzelnen D

Testen Sie Ihre Codierungsfähigkeiten mit diesem VHDL-Quiz, nachdem Sie die Tutorials 6-11 aus der Basic VHDL Tutorial-Reihe abgeschlossen haben! Wenn Sie die Blogbeiträge gelesen, die Videos angesehen und die Übungen gemacht haben, sollten Sie qualifiziert sein, die meisten Fragen im Quiz zu beant

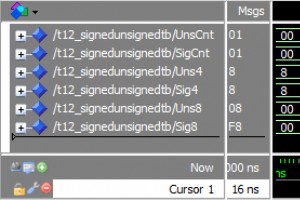

Die Typen mit und ohne Vorzeichen in VHDL sind Bitvektoren, genau wie der Typ std_logic_vector. Der Unterschied besteht darin, dass der std_logic_vector zwar großartig für die Implementierung von Datenbussen ist, aber für die Durchführung arithmetischer Operationen nutzlos ist. Wenn Sie versuchen,

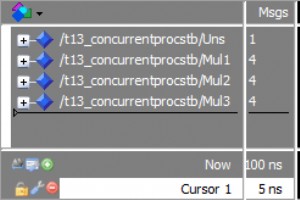

Eine gleichzeitige Anweisung in VHDL ist eine Signalzuweisung innerhalb der Architektur, aber außerhalb eines normalen Prozesskonstrukts. Die gleichzeitige Anweisung wird auch als gleichzeitige Zuweisung oder gleichzeitiger Prozess bezeichnet. Wenn Sie eine gleichzeitige Anweisung erstellen, erstel

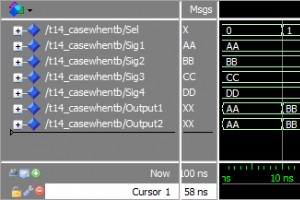

Die Case-When-Anweisung bewirkt, dass das Programm abhängig vom Wert eines Signals, einer Variablen oder eines Ausdrucks einen von mehreren verschiedenen Pfaden nimmt. Es ist eine elegantere Alternative zu einer If-Then-Elsif-Else-Anweisung mit mehreren Elsifs. Andere Programmiersprachen haben ähnl

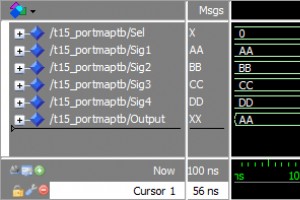

Ein Modul ist eine eigenständige Einheit von VHDL-Code. Module kommunizieren mit der Außenwelt über die Entität . Hafenkarte ist der Teil der Modulinstanziierung, in dem Sie angeben, mit welchen lokalen Signalen die Ein- und Ausgänge des Moduls verbunden werden sollen. In früheren Tutorials dieser

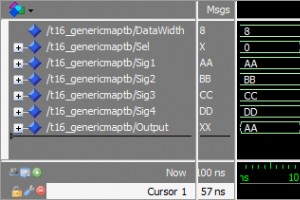

Das Erstellen von Modulen ist eine großartige Möglichkeit, Code wiederzuverwenden, aber oft benötigen Sie dasselbe Modul mit kleineren Variationen in Ihrem gesamten Design. Dafür sind Generika und die generische Karte da. Es erlaubt Ihnen, bestimmte Teile des Moduls zur Kompilierzeit konfigurierbar

VHDL

Experteninterview:Ein Gespräch mit Avi Reichental, Gründer von Xponentialworks und ehemaliger CEO von 3D Systems

Was ist der Unterschied zwischen Laserschneiden und Stanzen?

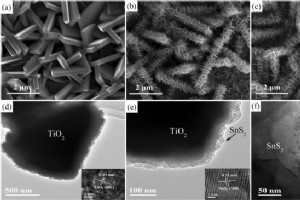

TiO2-Nanoblatt-Arrays mit geschichteten SnS2- und CoOx-Nanopartikeln für eine effiziente photoelektrochemische Wasserspaltung

Wie funktioniert ein 3D-Stift?